Magnetic Random Access Memory (STT-MRAM) Kui Cai 1 , K.A.S Immink 2 , - PowerPoint PPT Presentation

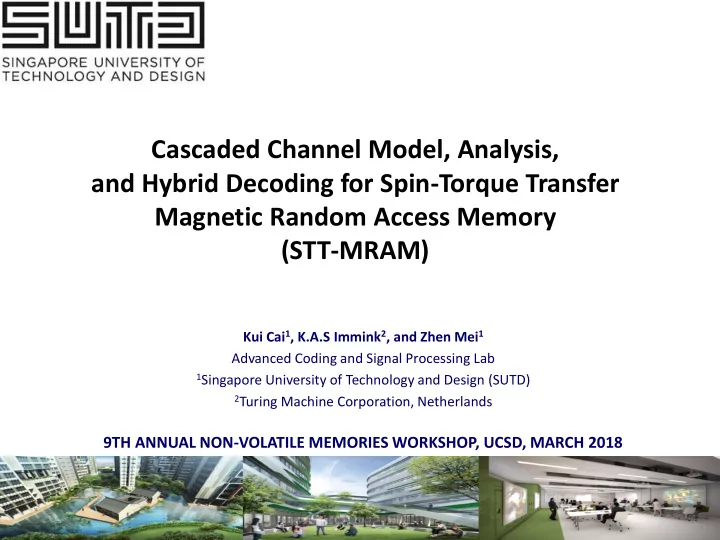

Cascaded Channel Model, Analysis, and Hybrid Decoding for Spin-Torque Transfer Magnetic Random Access Memory (STT-MRAM) Kui Cai 1 , K.A.S Immink 2 , and Zhen Mei 1 Advanced Coding and Signal Processing Lab 1 Singapore University of Technology and

Cascaded Channel Model, Analysis, and Hybrid Decoding for Spin-Torque Transfer Magnetic Random Access Memory (STT-MRAM) Kui Cai 1 , K.A.S Immink 2 , and Zhen Mei 1 Advanced Coding and Signal Processing Lab 1 Singapore University of Technology and Design (SUTD) 2 Turing Machine Corporation, Netherlands 9TH ANNUAL NON-VOLATILE MEMORIES WORKSHOP, UCSD, MARCH 2018 1/16

Introduction of STT-MRAM A promising emerging non-volatile memory (NVM) technology – Non-volatility – High endurance – Good scalability magnetic tunneling junction – High write/read speed (MTJ) ‘1 -> 0’ ‘0 -> 1’ – Low power consumption 2/16

Major Technical Challenges Process variation & thermal fluctuation result in the Block schematic of MTJ switching current distribution simultaneous existence of 3 types of errors probability density function Write errors – Process variation induced variation of the MTJ geometry and nMOS transistor size => widened distribution of the switching current threshold & variation of the transistor driving current – Thermal fluctuation => switching is probabilistic – The write error rate for 0->1 switching ( P 1 ), is much higher MTJ switching current than that for 1->0 switching ( P 0 ) Read disturb errors – Accidental flipping of MTJ during read ( P r ) – Caused by a large read current due to process variation or thermal fluctuation Read decision errors – Fail to differentiate the two resistance states due to widened resistance distributions – Caused by process variation induced variations of the tunneling oxide thickness and cross-section area, the tunneling oxide imperfection and the interfacial scattering effect 3/16

Modeling of STT-MRAM Memory physics based modeling [1] – Modeling of switching current distributions • Analytical approach to compute J c using macrospin model • Statistical approach to compute MTJ switching current distributions – Modeling of magnetization dynamical switching using LLG equations • Switching current vs switching time – Modeling of NMOS transistors • Generates MTJ driving current distributions for given NMOS parameters at a specific technology node – Modeling of static resistance distributions • Statistical model to estimate distributions due to parametric variations • Quantum tunneling model: interface imperfections; oxygen vacancy defects in MgO Memory circuit level modeling – Compact models [2] [1] B. Chen, K. Cai , G.C. Han, S.T. Lim, and M. Tran, “A portable dynamic switching model for perpendicular magnetic tunnel junctions considering both thermal and process variations”, IEEE Trans. Magnetic, vol. 51, no. 11, Article #:1300704, Nov. 2015. [2] W. Guo et al. , “SPICE modelling of magnetic tunnel junctions written by spin- transfer torque,” J. Phys. D, Appl. Phys. , vol. 43, no. 21, pp. 215001-1 – 215001-8, 2010. 4/16

The Cascaded BAC and GMC Channel Model We propose a new class of binary-input, asymmetric, and memoryless channel model, the cascaded binary asymmetric channel (BAC) and Gaussian mixture channel (GMC) model [3] – A communication type of channel model The combined model of the write error and read disturb error [3] K. Cai and K.A.S Immink, “Cascaded Channel Model, Analysis, and Hybrid Decoding for Spin -Torque Transfer Magnetic Random Access Memory (STT- MRAM),” IEEE Trans. Magnetics , vol. 53, no. 11, Article #:8204311, Nov. 2017. 5/16

The Cascaded BAC and GMC Channel Model Cascaded Binary Asymmetric Channel (BAC) and Gaussian Mixture Channel (GMC) Model Significantly improves the memory array error rate simulation speed Facilitates the theoretical design and analysis of the memory sensing and error correction coding schemes for STT-MRAM 6/16

Channel Raw Bit Error Rate (BER) Channel raw bit error rate (BER) analysis Dominant error events distributions 7/16

Soft-Output Channel Detection Algorithm Soft-output detector for the cascaded BAC-GMC channel 8/16

The Maximum Likelihood (ML) Decision Criterion Optimum decoding for the cascaded BAC-GMC channel 9/16

Extended Hamming Codes with Hybrid Decoding The state of the art ECCs for STT-MRAM – Everspin’s 16Mb MRAM: (71, 64) Hamming code [4] – TDK- Headway’s 8Mb STT -MRAM test chip (2017): 2-bit ECC [5] As an example, we adopt an extended Hamming code – (72, 64) extended Hamming code We first propose a modified Chase decoder with ML metric for STT-MRAM We further present a two-stage hybrid decoder Hard decision-decoding Successful error correction? Yes No Modified Chase decoding Exit [4] https://www.everspin.com/file/162/download [5] http://hobbydocbox.com/Radio/66149727-Basic-principles-challenges-and-opportunities-of-stt-mram-for-embedded-memory- applications.html 10/16

Simulation Results 0 • Chase decoder with ML metric 10 performs significantly better than both the hard-decision decoder -1 10 (HDD) and Chase decoder with the conventional metric -2 • The two-stage hybrid decoder 10 achieves similar performance with FER the full Chase decoder -3 P 1 =1 10 -4 10 • The (72, 64) code with hybrid 1 w/o ECC decoding performs significantly 2 (71,64) code, HDD -4 3 (71, 64) code, Chase, Cascaded ML metric better than (71, 64) code with 10 4 (71, 64) code, Hybrid hybrid decoding 5 (72, 64) code, HDD • The hybrid decoder can greatly 6 (72, 64) code, Chase, SED metric -5 7 (72, 64) code, Chase, GMC ML metric 10 improve the system’s tolerance to 8 (72, 64) code, Chase, Cascaded ML metric the process variation (2% more), in 9 (72, 64) code, Hybrid 8 9 10 11 12 13 14 15 16 the presence of write errors 0 / 0 (%) 11/16

Simulation Results ( contd .) • There is a high error floor at 0 10 1 w/o ECC FER = 4 × 10 -4 , for the HDDs of both 2 (71,64) code, HDD the (71,64) code and (72, 64) code. 3 (71, 64) code, Chase, BAC-GMC ML metric -1 10 This means the system will never 4 (71, 64) code, Hybrid 5 (72, 64) code, HDD work with the HDD, no matter how 6 (72, 64) code, Chase, SED metric small the write error rate P 1 is -2 7 (72, 64) code, Chase, GMC ML metric 10 • The hybrid decoder of the (71, 64) 8 (72, 64) code, Chase, BAC-GMC ML metric code only slightly lower the error 9 (72, 64) code, Hybrid FER -3 floor. 10 • The (72, 64) code with hybrid decoding overcomes the high error -4 10 floor with the HDD, and improves the maximum affordable write error rate -5 10 • The hybrid decoder can greatly improve the system tolerance to the write errors, irrespective of the -6 -5 -4 -3 -2 10 10 10 10 10 resistance spread. P 1 12/16

Decoding Latency Analysis Computational complexity analysis of the full-Chase decoder Latency of the hybrid decoder • The decoding latency of the hybrid decoder is just 0.11% higher than the hard-decision decoder 13/16

Conclusions We have proposed the cascaded BAC-GMC model, a new communication type of channel model for STT-MRAM – To significantly improve the memory array error rate simulation speed – To facilitate the theoretical design and analysis of the memory sensing and error correction coding schemes for STT-MRAM We have derived for the cascaded BAC-GMC channel – The channel raw BERs – The bit LLR – The ML decision criterion As an example, we present a hybrid decoding algorithm for extended Hamming codes for the cascaded channel – The hybrid decoding algorithm can significantly improve the system’s tolerance to both the write errors and the read errors, with little increase of the decoding latency over the HDD – It can also be directly applied to other extended BCH codes, for the applications of NVMs with relaxed requirement on the decoding latency 14/16

Subsequent Work “Polar coding for STT - MRAM” – Accepted by Intermag 2018 “Dynamic threshold detection based on pearson distance detection” – Accepted by IEEE Trans. Commun. 15/16

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.