M ethodologies for Reducing ULP Device Power Consumption Dr. Ivan - PowerPoint PPT Presentation

M ethodologies for Reducing ULP Device Power Consumption Dr. Ivan OConnell, & Donnacha ORiordan, M icroelectronic Circuis Centre Ireland (M CCI), Tyndall Wednesday 30 th M ay 2018 Energy Harvesting Source: Lorandt Foelkel, Energy

M ethodologies for Reducing ULP Device Power Consumption Dr. Ivan O’Connell, & Donnacha O’Riordan, M icroelectronic Circuis Centre Ireland (M CCI), Tyndall Wednesday 30 th M ay 2018

Energy Harvesting Source: Lorandt Foelkel, “Energy Harvesting Seminar," Wurth Elektronik eiSos, 2013

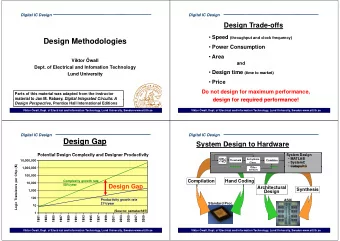

M otivation • Address the “Energy Gap” • Designers always look for ways to reduce unwanted components of power consumption – architecting the design in a fashion which includes low power techniques – adopting a process which can reduce the consumption • Always done at the expense of performance, reliability, chip area, or several of these – one has to reach a compromise between power, performance, and cost

Ultra Low Power Drivers • Battery Powered Systems – Phones – M obile revolution has really driven need for low power design • High-Performance Systems – Server Farms – Cost of removing the unused energy Heat – Reliability • IoT – Deploy and forget devices – Cost of transmitting data move processing being done at the edge

How to achieve this? • Dynamic Power Consumption • Static Power Consumption • Process T echnology • Architectural decisions

Dynamic Power Consumption • Switching & short circuit power V DD • P dyn = a C 2 F tot V DD Charge – C tot = C load + C par – V DD - Supply Voltage Out In – F – clock Frequency C tot discharge

Voltage Scaling – Reducing the Supply Voltage V DD Logic High V DD Limited by the ability to accurately differentiate Logic Low between a 1 and 0

Clock Gating • Remove unnecessary switching activity • Only clock necessary blocks • Remove clock from other blocks

Frequency scaling • Clock frequency adjusted to meet requirements • Frequency islands Island 20M Hz Thresholds Island Thresholds 5M Hz Island 1M Hz Thresholds

Asynchronous logic • Synchronous • Asynchronous • Clock Driven • Event Driven • P dyn activity independent • P dyn activity dependent

Static – Leakage Power Reduction • The power a circuit consumes when it’s doing nothing! V DD • Finite off Resistance • P = k V DD R off – Voltage scaling Out In 1 – T echnology 0 – Device Selection C tot • High Vt Devices

Power Gating • Remove the power to inactive blocks • Leakage Power zero V DD CM OS Block

Power Duty Cycling • Turning on and off sub-blocks to mininise the power consumption P on P leakag e T turn-off T turn- T T on slee on p

Power Duty Cycling • t sleep – time the device spends in sleep mode • T turn-on – time the device/ block takes to turn on • T on – active time • T turn-off – time it takes to turn the device/ block off • Objective Limited by the Leakage Current – P avg = 2x P leakage • e.g. P on = 100X P leakage • T sleep = 100 X T on

M OS Transistor Regions of operation • Linear Region • Near Threshold • Sub Threshold Near Subthreshold Linear Threshol d Source: www.design-reuse.com/news_img/20090316b_5.gif

T echnology Scaling – M oore – M ore than M oore

Technology Scaling – M oore – M ore than M oore

Technology Scaling – M oore – M ore than M oore

CM OS T echnology Scaling • Process scaling will continue • Cost/ transistor no longer reducing • Energy density increasing • Leakage currents increasing • M ature process nodes here to stay – Driven by reliability requirements – Cost Source: Z. Abbas, M. Oliveri “Impact of technology scaling on leakage power in nano-scale bulk CMOS digital standard cells” Microelectronics Journal

Adequate computing • Full precision is not always required! • Circuits / Systems are over designed • Driven by QoS

Source: EU Workshop ““Energy-Efficient Computing Systems, dynamic adaptation of Quality of Service and approximate computing”

Some recent developments

Conclusions • Significant progress in ULP design • Energy Gap is reducing • Most Power efficient block does not imply power efficient system • Portfolio of tricks/techniques available • No silver bullet technique 23

Q & A Thanks a lot for your time and attention! Any questions and/ or comments? 24

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.