Is branch prediction The article cited by Wikipedia important for - PowerPoint PPT Presentation

1 2 Is branch prediction The article cited by Wikipedia important for performance? says: Branch predictor (BP) is an essential component in modern Daniel J. Bernstein processors since high BP accuracy can improve performance and Spectre

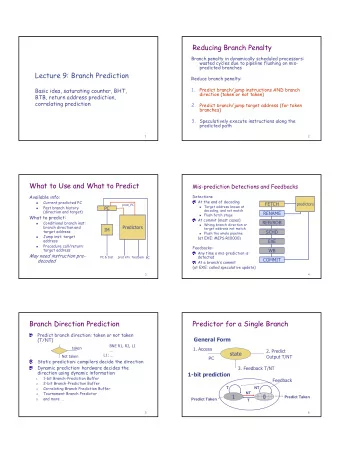

1 2 Is branch prediction The article cited by Wikipedia important for performance? says: “Branch predictor (BP) is an essential component in modern Daniel J. Bernstein processors since high BP accuracy can improve performance and Spectre paper: “Modern reduce energy by decreasing processors use branch prediction the number of instructions and speculative execution to executed on wrong-path.” maximize performance.” Wikipedia: “Branch predictors play a critical role in achieving high effective performance in many modern pipelined microprocessor architectures such as x86.”

1 2 Is branch prediction The article cited by Wikipedia important for performance? says: “Branch predictor (BP) is an essential component in modern Daniel J. Bernstein processors since high BP accuracy can improve performance and Spectre paper: “Modern reduce energy by decreasing processors use branch prediction the number of instructions and speculative execution to executed on wrong-path.” maximize performance.” — Omitting branch prediction Wikipedia: “Branch predictors reduces energy even more. play a critical role in achieving Eliminates all wrong-path high effective performance instructions. Also eliminates in many modern pipelined cost of prediction+speculation. microprocessor architectures such as x86.”

1 2 Is branch prediction The article cited by Wikipedia important for performance? says: “Branch predictor (BP) is an essential component in modern Daniel J. Bernstein processors since high BP accuracy can improve performance and Spectre paper: “Modern reduce energy by decreasing processors use branch prediction the number of instructions and speculative execution to executed on wrong-path.” maximize performance.” — Omitting branch prediction Wikipedia: “Branch predictors reduces energy even more. play a critical role in achieving Eliminates all wrong-path high effective performance instructions. Also eliminates in many modern pipelined cost of prediction+speculation. microprocessor architectures The real question is latency . such as x86.”

1 2 nch prediction The article cited by Wikipedia The CPU rtant for performance? says: “Branch predictor (BP) is Cycle 1: an essential component in modern J. Bernstein fetch processors since high BP accuracy can improve performance and decode ectre paper: “Modern reduce energy by decreasing register cessors use branch prediction the number of instructions execute eculative execution to executed on wrong-path.” register maximize performance.” — Omitting branch prediction edia: “Branch predictors reduces energy even more. critical role in achieving Eliminates all wrong-path effective performance instructions. Also eliminates many modern pipelined cost of prediction+speculation. rocessor architectures The real question is latency . as x86.”

1 2 rediction The article cited by Wikipedia The CPU pipeline rformance? says: “Branch predictor (BP) is Cycle 1: an essential component in modern Bernstein fetch processors since high BP accuracy can improve performance and decode “Modern reduce energy by decreasing register read ranch prediction the number of instructions execute execution to executed on wrong-path.” register write rmance.” — Omitting branch prediction “Branch predictors reduces energy even more. role in achieving Eliminates all wrong-path erformance instructions. Also eliminates pipelined cost of prediction+speculation. rchitectures The real question is latency .

1 2 The article cited by Wikipedia The CPU pipeline rmance? says: “Branch predictor (BP) is Cycle 1: an essential component in modern fetch processors since high BP accuracy a=b+c can improve performance and decode reduce energy by decreasing register read rediction the number of instructions execute to executed on wrong-path.” register write — Omitting branch prediction redictors reduces energy even more. achieving Eliminates all wrong-path instructions. Also eliminates cost of prediction+speculation. rchitectures The real question is latency .

2 3 The article cited by Wikipedia The CPU pipeline says: “Branch predictor (BP) is Cycle 1: an essential component in modern fetch processors since high BP accuracy a=b+c can improve performance and decode reduce energy by decreasing register read the number of instructions execute executed on wrong-path.” register write — Omitting branch prediction reduces energy even more. Eliminates all wrong-path instructions. Also eliminates cost of prediction+speculation. The real question is latency .

2 3 The article cited by Wikipedia The CPU pipeline says: “Branch predictor (BP) is Cycle 2: an essential component in modern fetch processors since high BP accuracy can improve performance and decode a=b+c reduce energy by decreasing register read the number of instructions execute executed on wrong-path.” register write — Omitting branch prediction reduces energy even more. Eliminates all wrong-path instructions. Also eliminates cost of prediction+speculation. The real question is latency .

2 3 The article cited by Wikipedia The CPU pipeline says: “Branch predictor (BP) is Cycle 3: an essential component in modern fetch processors since high BP accuracy can improve performance and decode reduce energy by decreasing register read a=b+c the number of instructions execute executed on wrong-path.” register write — Omitting branch prediction reduces energy even more. Eliminates all wrong-path instructions. Also eliminates cost of prediction+speculation. The real question is latency .

2 3 The article cited by Wikipedia The CPU pipeline says: “Branch predictor (BP) is Cycle 4: an essential component in modern fetch processors since high BP accuracy can improve performance and decode reduce energy by decreasing register read the number of instructions execute a=b+c executed on wrong-path.” register write — Omitting branch prediction reduces energy even more. Eliminates all wrong-path instructions. Also eliminates cost of prediction+speculation. The real question is latency .

2 3 The article cited by Wikipedia The CPU pipeline says: “Branch predictor (BP) is Cycle 5: an essential component in modern fetch processors since high BP accuracy can improve performance and decode reduce energy by decreasing register read the number of instructions execute executed on wrong-path.” register write a=b+c — Omitting branch prediction 1 instruction finishes in 5 cycles. reduces energy even more. Eliminates all wrong-path instructions. Also eliminates cost of prediction+speculation. The real question is latency .

2 3 The article cited by Wikipedia The CPU pipeline says: “Branch predictor (BP) is Another program, cycle 1: an essential component in modern fetch processors since high BP accuracy a=b+c can improve performance and decode reduce energy by decreasing register read the number of instructions execute executed on wrong-path.” register write — Omitting branch prediction reduces energy even more. Eliminates all wrong-path instructions. Also eliminates cost of prediction+speculation. The real question is latency .

2 3 The article cited by Wikipedia The CPU pipeline says: “Branch predictor (BP) is Cycle 2: an essential component in modern fetch processors since high BP accuracy d=e+f can improve performance and decode a=b+c reduce energy by decreasing register read the number of instructions execute executed on wrong-path.” register write — Omitting branch prediction Second instruction is fetched; reduces energy even more. first instruction is decoded. Eliminates all wrong-path Hardware units operate in parallel. instructions. Also eliminates cost of prediction+speculation. The real question is latency .

2 3 The article cited by Wikipedia The CPU pipeline says: “Branch predictor (BP) is Cycle 3: an essential component in modern fetch processors since high BP accuracy g=h-i can improve performance and decode d=e+f reduce energy by decreasing register read a=b+c the number of instructions execute executed on wrong-path.” register write — Omitting branch prediction Third instruction is fetched; reduces energy even more. second instruction is decoded; Eliminates all wrong-path first instruction does register read. instructions. Also eliminates cost of prediction+speculation. The real question is latency .

2 3 The article cited by Wikipedia The CPU pipeline says: “Branch predictor (BP) is Cycle 4: an essential component in modern fetch processors since high BP accuracy j=k+l can improve performance and decode g=h-i reduce energy by decreasing register read d=e+f the number of instructions execute a=b+c executed on wrong-path.” register write — Omitting branch prediction reduces energy even more. Eliminates all wrong-path instructions. Also eliminates cost of prediction+speculation. The real question is latency .

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![Semantic Wikipedia [[enhances::Wikipedia]] Wikipedia today A free online encyclopdia](https://c.sambuz.com/830932/semantic-wikipedia-s.webp)