Branch Prediction Philipp Koehn 11 October 2019 Philipp Koehn - PowerPoint PPT Presentation

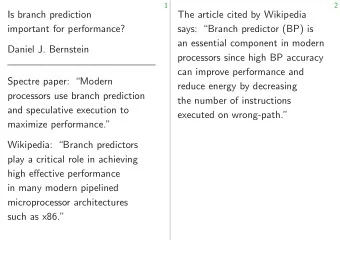

Branch Prediction Philipp Koehn 11 October 2019 Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019 Control Hazard 1 Also called branch hazard Selection of next instruction depends on outcome of previous

Branch Prediction Philipp Koehn 11 October 2019 Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Control Hazard 1 • Also called branch hazard • Selection of next instruction depends on outcome of previous • Example beq $s0, $s1, ff40 sub $t0, $s0, $t3 – sub instruction only executed if branch condition fails → cannot start until branch condition result known Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

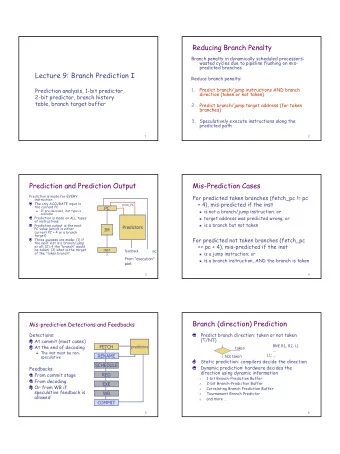

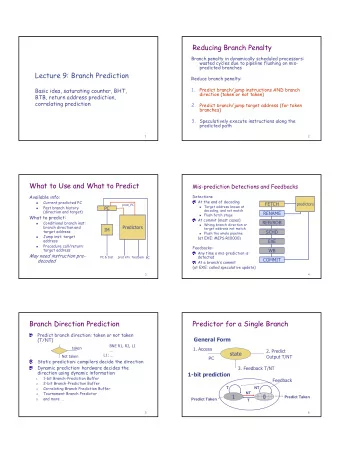

Methods 2 • Assume branch not taken – start execution of following instructions – if wrong, flush them • Reduce delay of branches – compute branch address and condition in fewer cycles → less flushing • Dynamic branch prediction Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

3 assume branch not taken Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Pipelined Datapath 4 IF: ID: Instruction decoder EX: Execute / MEM: WB: Instruction Fetch register file read address calculate Memory access Write Back 4 Add ADD Sign Shift extended Left Selector Read Read PC Address register 1 data 1 Zero Selector Read ALU Instruction register 2 Selector Address Memory Result Read Registers data Write Read Instruction Data register data 2 Memory Write Write data data Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Branch: Address Calculation 5 IF: ID: Instruction decoder EX: Execute / MEM: WB: Instruction Fetch register file read address calculate Memory access Write Back 4 Add ADD Sign Shift extended Left Selector Read Read Address PC register 1 data 1 Zero Selector Read ALU Instruction register 2 Selector Result Address Memory Read Registers data Write Read Instruction Data register data 2 Memory Write Write data data Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Branch: Condition Checking 6 IF: ID: Instruction decoder EX: Execute / MEM: WB: Instruction Fetch register file read address calculate Memory access Write Back 4 Add ADD Sign Shift extended Left Selector Read Read PC Address register 1 data 1 Zero Selector Read ALU Instruction register 2 Selector Address Memory Result Registers Read data Write Read Instruction Data register data 2 Memory Write Write data data Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Idea 7 • Assume branch not taken • Execute the subsequent instructions • If branch should have been taken → flush out subsequent instruction processing Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Branch Execution 8 200 400 600 800 1000 1200 beq $s0,$s1,ff40 IF Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Branch Execution 9 200 400 600 800 1000 1200 beq $s0,$s1,ff40 IF ID IF Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Branch Execution 10 200 400 600 800 1000 1200 beq $s0,$s1,ff40 IF ID EX IF ID IF Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Take Branch: Invalidates Instructions 11 200 400 600 800 1000 1200 beq $s0,$s1,ff40 Hazard IF ID EX IF ID EX IF ID IF Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Flush Instructions 12 200 400 600 800 1000 1200 beq $s0,$s1,ff40 IF ID EX MEM WB X X X IF ID EX bubble X X IF ID bubble X IF bubble IF Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Flush Instructions 13 • Change program counter • Flush instructions in stages IF, ID, EX, MEM ⇒ Re-fetch instruction in IF ⇒ Zero out control lines for ID, EX, MEM Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

14 fast branch execution Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Idea 15 • Branch instruction beq $s0, $s1, ff40 • Computations required – target address (PC + specified offset) – condition check (simple equality) • Idea: carry out these computations quickly Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Branch Computation in ID Stage 16 • Role of ID stage – decode what the instruction is – look up register values • Now – just assume that it is a branch – add special wiring for branch calculation – if not a branch, ignore results • Benefit: reduce branch flushing from 3 to 1 instruction Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Pipeline with Hazard Detection Unit 17 IF: ID: Instruction decoder EX: Execute / MEM: WB: Instruction Fetch register file read address calculate Memory access Write Back Branch Handling 4 Unit Add ADD Shift Sign Left extended Selector Read Read PC Address register 1 data 1 Zero Selector Read ALU Instruction register 2 Selector Address Memory Result Read Registers data Write Read Instruction Data register data 2 Memory Write Write data data Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Register Values for Condition Check 18 IF: ID: Instruction decoder EX: Execute / MEM: WB: Instruction Fetch register file read address calculate Memory access Write Back Branch Handling 4 Unit Add ADD Shift Sign Left extended Selector Read Read PC Address register 1 data 1 Zero Selector Read ALU Instruction register 2 Selector Address Memory Result Registers Read data Write Read Instruction Data register data 2 Memory Write Write data data Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Address Calculation 19 IF: ID: Instruction decoder EX: Execute / MEM: WB: Instruction Fetch register file read address calculate Memory access Write Back Branch Handling 4 Unit Add ADD Shift Sign Left extended Selector Read Read Address PC register 1 data 1 Zero Selector Read ALU Instruction register 2 Selector Result Address Memory Read Registers data Write Read Instruction Data register data 2 Memory Write Write data data Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Also a Data Hazard? 20 • Condition check requires register values • These may be changed by preceding instructions in pipeline ⇒ Forwarding and stalling needed • Adds complexity Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

21 branch prediction Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

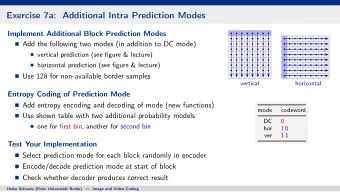

Prediction 22 • So far: predict branch not taken • Compiler may order instructions → more frequent case in sequence • Now: dynamic branch prediction based on branch history table Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Branch History Table 23 • Idea: keep record of branch history • Many branches, many executions • Keep it simple: – index by lower order bits of branch address (ignore collisions) – just store last decison (1 bit) • Special memory in ID stage Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Example: Loop 24 • Example: Loop 9 times, then exit loop • False predictions – last iteration (not taken, after 9 times taken) – first iteration (taken, previously exited loop) • Prediction accuracy: 8/10 = 80% • Can we do better? Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

2 Bits 25 • Idea: record frequency took took branch took branch took branch branch 0 1 2 3 not taken not taken not taken not taken • Previous example (loop 9 times, then exit loop) Iteration Value Prediction 1 2 take branch (correct) 2 3 take branch (correct) ... ... ... 9 3 take branch (correct) 10 3 take branch (wrong) Philipp Koehn Computer Systems Fundamentals: Branch Prediction 11 October 2019

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.