InvisiSpec: Making Speculative Execution Invisible in the Cache - PowerPoint PPT Presentation

InvisiSpec: Making Speculative Execution Invisible in the Cache Hierarchy Mengjia Yan, Jiho Choi, Dimitrios Skarlatos, Adam Morrison, Christopher W. Fletcher, and Josep Torrellas University of Illinois at Urbana-Champaign Tel Aviv

InvisiSpec: Making Speculative Execution Invisible in the Cache Hierarchy Mengjia Yan, Jiho Choi, Dimitrios Skarlatos, Adam Morrison∗, Christopher W. Fletcher, and Josep Torrellas University of Illinois at Urbana-Champaign ∗Tel Aviv University The Blavatnik School of Computer Science The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University

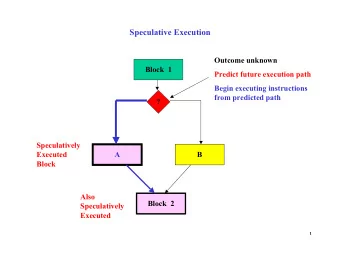

2 InvisiSpec: Making Speculative Execution Invisible in the Cache Hierarchy Speculative Execution Attacks o Exploit the side effects of instructions on incorrectly-speculated paths (instructions to be squashed) o Exploit a key feature of current ooo processors: speculative execution o Any meaningful defense needs hardware support o Defenses will be easier to implement in • Simple cores • Cores with “little legacy” The Blavatnik School of Computer Science The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University

3 InvisiSpec: Making Speculative Execution Invisible in the Cache Hierarchy Existing Speculative Execution Attacks o Exploit the side-effects of transient instructions (speculatively-executed instructions that are doomed to be squashed) Sources of Transient Existing Attack 1: if (x < array1_size) { Instructions Spectre Control-flow misprediction 2: val = array1[x] Meltdown 3: ld array2[val] Virtual memory exception L1 Terminal Fault 4: } Speculative Store Address alias between a load and Bypass an earlier store Transient Instructions The Blavatnik School of Computer Science The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University

4 InvisiSpec: Making Speculative Execution Invisible in the Cache Hierarchy Proposal: Comprehensive Speculative Attack Model o Any speculative load (i.e., load not at the head of ROB) is vulnerable Attack Model Sources of Transient Instructions Various events, such as: • Exceptions • Control-flow mispredictions Comprehensive • Address alias between a load and an earlier store • Address alias between two loads • Memory consistency model violations • Interrupts Spectre Control-flow misprediction o New speculative execution attacks may be found in the future The Blavatnik School of Computer Science The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University

5 InvisiSpec: Making Speculative Execution Invisible in the Cache Hierarchy Lifetime of a load instruction Load is issued Load reaches All prior branches to memory head of ROB are resolved • Exceptions • Control-flow Load is speculative mispredictions unsafe • Address alias safe Spectre attack model load and store • Address alias unsafe safe Comprehensive load and load attack model • Memory consistency model Visibility Point violations The load becomes • Interrupts unsquashable The Blavatnik School of Computer Science The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University

How do we Defend against Speculative Attacks? The Blavatnik School of Computer Science The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University

7 InvisiSpec: Making Speculative Execution Invisible in the Cache Hierarchy Trivial Approach o Delay issuing the load until its Visibility Point Load could be issued to Load reaches Visibility memory head of ROB Point Delay Issue the load Speculative loads are issued later than in a conventional processor To defend against the comprehensive attack model à the processor becomes an in-order processor The Blavatnik School of Computer Science The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University

8 InvisiSpec: Making Speculative Execution Invisible in the Cache Hierarchy Better Approach o The load probes the local L1/L2 o If hit, get the data and use it, but do not change the state (i.e., cache replacement bits) o Otherwise, delay until the Visibility Point Load could be issued to Load reaches Visibility memory head of ROB Point Change Probe L1/L2 and hit replacement bits Load reaches Visibility head of ROB Point Probe L1/L2 and miss: Delay Issue the load The Blavatnik School of Computer Science The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University

9 InvisiSpec: Making Speculative Execution Invisible in the Cache Hierarchy Advanced Approach The load probes the local L1/L2 o If hit, get the data and use it, but do not change the state o Otherwise o o Use Value Prediction to return a value to the pipeline o At the Visibility Point: Issue the load and compare the return value to the predicted one o Squash if they are different Load could be issued to Load reaches Visibility memory head of ROB Point Probe L1/L2. If miss, predict value Issue the load Compare The Blavatnik School of Computer Science The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University

10 InvisiSpec: Making Speculative Execution Invisible in the Cache Hierarchy More Advanced Approach o Speculative Taint Tracking: Smart delay-based Load could be issued to Load reaches Visibility memory head of ROB Point Untainted: Issue without delay Load reaches Visibility head of ROB Point Tainted: Delay until untainted Issue the load The Blavatnik School of Computer Science The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University

Super Advanced Approach: InvisiSpec: Issue the Load Invisibly The Blavatnik School of Computer Science The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University

12 InvisiSpec: Making Speculative Execution Invisible in the Cache Hierarchy InvisiSpec o Issue the load immediately, invisibly (i.e., no change to the cache hierarchy) o At the Visibility Point: HW re-issues the load and changes state of caches Load reaches Load is issued Visibility head of ROB to memory Point Issue an invisible Use the Make the load load request value visible in cache Speculative loads are issued as early as in a conventional machine and can pass data to dependent instructions immediately Add an “invisible transaction” that does not change the states of the caches The Blavatnik School of Computer Science The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University

InvisiSpec: Making Speculative Execution Invisible in the Cache Hierarchy 13 Making Unsafe Loads Invisible o Invisible load request • No modification to cache states, including core core • Cache occupancy • Replacement information • Coherence information L1 cache L1 cache SB SB • TLB state • Bring the data to Speculative Buffer (SB) (in addition to the register) LLC Invisible Returned data load request The Blavatnik School of Computer Science The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University

14 InvisiSpec: Making Speculative Execution Invisible in the Cache Hierarchy Risk of Making Loads Visible at Visibility Point memory consistency violations Load reaches Load is issued Visibility head of ROB to memory Point Issue an invisible Use the Make the load load request value visible in cache Window of Invisibility o Make the load visible: HW issues a normal request (which changes the caches) o While in the Window of Invisibility, processor does not receive invalidations The Blavatnik School of Computer Science The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University

15 InvisiSpec: Making Speculative Execution Invisible in the Cache Hierarchy An Example of Memory Consistency Violation P1 P1 sees the lock is Ld lock free, but has read Ld counter old counter. Ld Ld counter lock P1 does not P1 receive an invalidation! time caches Wr release counter lock The Blavatnik School of Computer Science The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University

16 InvisiSpec: Making Speculative Execution Invisible in the Cache Hierarchy How to Make Load Visible while Maintaining Consistency? At Visibility Point: HW issues the request that changes state of caches (“Validation”) Data goes into L1. Compare the incoming data and the one in the SB squash and If mismatch, squash the load as it violates memory consistency model retry Problem: validations may cause stall at ROB head o Visibility Visibility Ld Ld point point counter lock Ld counter Ld lock P1 time caches Wr release The Blavatnik School of Computer Science The Raymond and Beverly Sackler counter lock Faculty of Exact Sciences Tel Aviv University

17 InvisiSpec: Making Speculative Execution Invisible in the Cache Hierarchy How to Reduce the Cost of Validations? o For loads with no risk of consistency violation: Issue an Exposure, not a Validation • HW issues the request at the Visibility Point There are many cases where a load • Load does not need to wait for response to retire can use Exposures • Data goes into cache. No need to compare data o High performance: does not cause a stall Visibility point Ld X Ld X P1 time caches Wr X The Blavatnik School of Computer Science The Raymond and Beverly Sackler Faculty of Exact Sciences Tel Aviv University

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.