Introduction to Computer Science CSCI 109 Readings St. Amant, Ch. - PowerPoint PPT Presentation

Introduction to Computer Science CSCI 109 Readings St. Amant, Ch. 3 Andrew Goodney Fall 2019 Lecture 2: Architecture Sept. 9th, 2019 Reminders u Take the survey if you havent already u https://tinyurl.com/y2cot2r5 v Password:

Introduction to Computer Science CSCI 109 Readings St. Amant, Ch. 3 Andrew Goodney Fall 2019 Lecture 2: Architecture Sept. 9th, 2019

Reminders u Take the survey if you haven’t already u https://tinyurl.com/y2cot2r5 v Password: CS109Fall2019 u HW #1 out by EoD today. Due 9/23 u Quiz #1 is on 9/16. It will cover material taught on 8/26 and 9/9. 1

Schedule 2

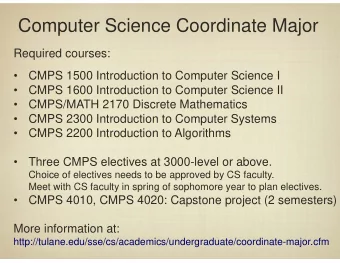

Computer Architecture u The von Neumann architecture u The Central Processing Unit (CPU) u Storage u Input and Output Reading: St. Amant Ch. 3 3

Motivation u What do computers do? v Math with binary numbers u So what do we need to build a computer? v Place to store binary numbers v Way to do math 4

“Memory” u Very generic term u ”Place to store a binary number” ENIAC ~660 bits Magnetic core memory Modern DRAM (<1 bit/ft^3) 1024 bits (10^16 bits/ft^3) (3.2 x 10^4 bits/ft^3) 5

Arithmetic/Logic u “math” we need to do with numbers in memory v ADD v SUBTRACT v MULTIPLY v DIVIDE v AND,OR,XOR,NOT v Etc… OP2 u Assume we can build a circuit that can do this u Takes numbers represented as digital (electrical) values, produces results as the same 6

Start building a circuit… bus 7

Instructing the CPU u Now we can make instructions… u Instructions are binary numbers that tell the circuit what to do u Select the 1 st operand, 2 nd operand, destination and function u With a series of such instructions the circuit can perform arbitrary computations 8

Where to get the instructions? u Instruction Memory ALU Controller 9

How to compute? u Fill instruction memory with desired program u Initialize data memory u Run an instruction (given by program counter) v Then increment program counter v Run next instruction, increment program counter… u Some early computers were pretty much just this 10

Toward the Von Neumann Architecture u Separate instruction and data memory is inefficient/inflexible u Von Neumann proposed combined data and instruction memory u Also want to support larger and heterogeneous memory outside the physical CPU 11

Simplified Von Neumann CPU u Controller + ALU + Registers = CPU I/O Bus Memory Bus 12

The Central Processing Unit (CPU) u Controller + ALU = Central Processing Unit (CPU) u CPU has a small amount of temporary memory within it v Registers v A special register called the program counter (PC) u CPU performs the following cycle repeatedly Fetch Decode Execute Instruction Instruction Instruction 13

Fetch-Decode-Excecute u Fetch v Get the next instruction from memory u Decode v Send the proper signals from the controller to the ALU and Registers u Execute v Let the ALU do its work to produce a result 14

Typical Controller Tasks u Read an instruction from memory u Direct ALU to do some arithmetic or logic operation u Transfer data from one place to another u Prepare for next instruction to be read u Send a directive to input or output device 15

Typical ALU Tasks u Perform an arithmetic operation on the contents of registers e.g., add R1 and R2 and put the result in R1 (R1 = R1 + R2) u Perform a logical operation on the contents of registers e.g., compare R1 and R2 (R1 < R2 ?) 16

Improving the CPU u Faster clock (~GHz on modern computers) u Specialized ALU (e.g., GPU) or more than one ALU u Multiprocessing (more than one CPU) u Streamlining Controller-ALU cooperation (pipelining) u More complex ALU instructions 17

Storage: Addressing and Random Access u How is storage organized ? u Linear ordering v Each stored item has a an address (which is a number) v To retrieve an item you have to know this number v Retrieval is by address 18

Storage: Modular and Hierarchical u Analogy with office files v Each (physical) file has a number v When a file is needed, you ask for it by number v In the office, files may be stored in shelves, on tables, in cabinets, etc. u Storage is modular : as long as the person who wants the file knows its number and as long as the storekeeper can find the file, doesn’t matter exactly how physical files are stored u Or where they are stored: Files may be stored in a basement – not easy to reach u So latency (time to access) differs 19

The Nature of Computer Storage u Only one item can be stored at one memory location u Random access – all locations in one type of memory are (on the average) equally slow (or fast) in terms of access speed u Storage is hierarchical – add new levels of memory 20

The Storage Hierarchy Cheaper & Faster Registers larger RAM (memory) Secondary Storage (Disk Space) 21

Trade-offs u An aside… u Identifying trade-offs is a fundamental engineering skill u Understanding and balancing trade-offs is part of design process u Not always easy to manage! u Conflicting interests u Speed vs. space is very common tradeoff in CS v So if you want faster execution you need more memory 22

Volatile Storage, Special Memory u Volatile: memory is erased when power turned off v Registers, RAM (often called primary storage) u Non-volatile: memory intact when power turned off v Secondary storage (disk) u Booting and ROM (read-only memory) u Cache: small, fast memory between registers and RAM 23

Cache u Small (but bigger than registers) u Volatile u Fast (not as fast as registers, but faster than RAM) u What to keep in the cache ? v Things that programs are likely to need in the future v Locality principle: u Look at what items in memory are being used u Keep items from nearby locations (spatial locality) u Keep items that were recently used (temporal locality) 24

Input and Output u Input: Interrupt-driven v e.g., Key strokes are slow, CPU treats them like special events u Output: Write to special memory (e.g., video memory) 25

Modern Computer Architecture diagram CPU Boot ROM Memory Controller L3 L2 Registers & I/O Controller DRAM Cache Program Counter Cache ALU I/O Devices On die, but not (USB, etc) part of "CPU" Disk controller Disk 26

Programming a CPU u How to compute? u Develop a series of low-level instructions v Using the registers and/or main memory for storage v Using only low-level operations made available by the particular CPU u ”Assembly language” v Or maybe even machine code (probably not, though) 27

Creating Assembly (Machine) Code u Adding four numbers in C is easy a = b + c + d + e u Equivalent assembly code add b, c, a OR add b, c, a add a, d, a add d, e, f add a, e, a add a, f, a u Which one is better ? Are the two equivalent ? 28

Programs at Different Abstraction Levels u C code a = b + c u Assembly code add b, c, a u Machine code 00000010001100100100000000100000 29

Programs at Different Abstraction Levels u C code a = b + c u Assembly code add b, c, a u Machine code 00000010001100100100000000100000 6 bits – opcode 5 bits: source register 1 5 bits: source register 2 5 bits: destination register 5 bits: shift amount 5 bits: functions 30

Typical Operations u ADD Ri Rj Rk Add contents of registers Ri and Rj and put result in register Rk u SUBTRACT Ri Rj Rk Subtract register Rj from register Ri and put result in register Rk u AND Ri Rj Rk Bitwise AND contents of registers Ri, Rj and put result in register Rk u NOT Ri Bitwise NOT the contents of register Ri u OR Ri Rj Rk Bitwise OR the contents of registers Ri, Rj and put result in register Rk u SET Ri value Set register Ri to given value u SHIFT-LEFT Ri Shift bits of register Ri left u SHIFT-RIGHT Ri Shift bits of register Ri right u MOVE Ri Rj Copy contents from register Ri to register Rj u LOAD Mi Ri Copy contents of memory location Mi to register Ri u WRITE Ri Mi Copy contents of register Ri to memory location Mi u GOTO Mi Jump to instruction stored in memory location Mi u COND_GOTO Ri Rj Mi If Ri > Rj, jump to instruction stored in memory location Mi 31

A Typical Day at PaniCorp u Central processing: Connie and Alun u The bus: Buster u Storage (Memory): Mr. Lager Read St. Amant Ch. 3 u Input and output Play out a typical instruction cycle with your friends 32

M100 LOAD M1 R1 M101 SET R2 0 M102 SET R3 1 M103 SET R6 0 M104 ADD R1 R2 R4 M105 SUB R1 R3 R5 M106 MOVE R5 R1 M107 MOVE R4 R2 M108 COND_GOTO R1 R6 104 M109 WRITE R2 M2 M110 END What does this program do?

M100 LOAD M1 R1 PC R1 R2 R3 R4 R5 R6 M1 M2 3 M101 SET R2 0 M102 SET R3 1 M103 SET R6 0 M104 ADD R1 R2 R4 M105 SUB R1 R3 R5 M106 MOVE R5 R1 M107 MOVE R4 R2 M108 COND_GOTO R1 R6 104 M109 WRITE R2 M2 M110 END

M100 LOAD M1 R1 PC R1 R2 R3 R4 R5 R6 M1 M2 3 M101 SET R2 0 M102 SET R3 1 M100 3 3 M103 SET R6 0 M104 ADD R1 R2 R4 M105 SUB R1 R3 R5 M106 MOVE R5 R1 M107 MOVE R4 R2 M108 COND_GOTO R1 R6 104 M109 WRITE R2 M2 M110 END

M100 LOAD M1 R1 PC R1 R2 R3 R4 R5 R6 M1 M2 3 M101 SET R2 0 M102 SET R3 1 M100 3 3 M103 SET R6 0 M101 3 0 3 M104 ADD R1 R2 R4 M105 SUB R1 R3 R5 M106 MOVE R5 R1 M107 MOVE R4 R2 M108 COND_GOTO R1 R6 104 M109 WRITE R2 M2 M110 END

M100 LOAD M1 R1 PC R1 R2 R3 R4 R5 R6 M1 M2 3 M101 SET R2 0 M102 SET R3 1 M100 3 3 M103 SET R6 0 M101 3 0 3 M102 3 0 1 3 M104 ADD R1 R2 R4 M105 SUB R1 R3 R5 M106 MOVE R5 R1 M107 MOVE R4 R2 M108 COND_GOTO R1 R6 104 M109 WRITE R2 M2 M110 END

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.