Hierarchical Exact Symbolic Analysis y y of Large Analog - PowerPoint PPT Presentation

Hierarchical Exact Symbolic Analysis y y of Large Analog Integrated Circuits By Symbolic Stamps Symbolic Stamps Hui Xu, Guoyong Shi and Xiaopeng Li School of Microelectronics, Shanghai Jiao Tong Univ. Shanghai, China Presentation at Asia

Hierarchical Exact Symbolic Analysis y y of Large Analog Integrated Circuits By Symbolic Stamps Symbolic Stamps Hui Xu, Guoyong Shi and Xiaopeng Li School of Microelectronics, Shanghai Jiao Tong Univ. Shanghai, China Presentation at Asia South-Pacific Design Automation Conference (ASPDAC), P t ti t A i S th P ifi D i A t ti C f (ASPDAC) Yokohama, Jan. 2010.

Contents Contents • Motivation and Background • The Idea of “Symbolic Stamp” The Idea of Symbolic Stamp • Implementation • Experimental Results • Conclusion • Conclusion 2011-11-25 2

Motivation

Small Case Small Case • Can be handled by existing exact symbolic analysis method VDD M8 M5 M7 Bias P In- In+ M1 M2 Out C L Rz Cc X Y M3 M4 M6 2011-11-25 4

Large Case Large Case • Cannot be handled by existing exact symbolic analysis method 2011-11-25 5

Possible Application Possible Application • Graphical Sensitivity Analysis [16] [16] D. Ma, G. Shi, and A. Lee, “A design platform for analog device size sensitivity analysis and visualization,” in Proc. Asia Pacific Conference on Circuits and Systems (APCCAS) , Malaysia, Dec. 2010 Date 2011-11-25 6

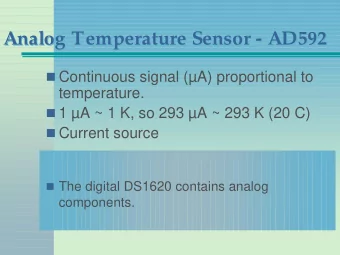

Motivation: Exact Analysis Motivation: Exact Analysis • Many circuit characteristics (sensitivity, poles, zeros) require an “exact” symbolic expression of H(s). • Exact symbolic analysis of large analog circuits (20 ~50 MOSFETs) is not easy. Sensitivity Symbolic Netlist Pole/Zero analysis y H(s; p 1 , p 2 , ...) engine Optimization Optimization 2011-11-25 7

Symbolic Analysis Symbolic Analysis Cons Pros 2011-11-25 8

Representative Methods Representative Methods • Algebraic Methods – Determinant Decision Diagram [15] 1 1 1 1 2 R R v 0 R 1 1 1 Data 0 v 0 to Matrix Algorithm C V s R R R R 2 s Struct St t i v 1 0 0 s s 0 • Graph-based Methods – Graph Pair Decision Diagram [16] Graph based Methods [16] G h P i D i i Di 1 2 + 1 2 1/R 2 R to Graph Algorithm Data C V s V o CS Vc Vs Struct - 0 0 [15] C.-J. Shi and X.-D. Tan, “Canonical symbolic analysis of large analog circuits with determinant decision diagrams,” IEEE Trans. on Computer-Aided Design , vol. 19, no. 1, pp. 1-18, Jan., 2000. [16] G. Shi, W. Chen and C.-J. Shi, “A Graph Reduction Approach to Symbolic Circuit Analysis,” in Proc. Asia and South-Pacific Design Automation Conference (ASPDAC), Yokohama, Japan, pp. 197-202, Jan., 2007. 9 2011-11-25

From Binary Tree to BDD From Binary Tree to BDD • Binary Tree f x x x ( , , ) x x x x x x x x x x x x 1 2 3 1 2 3 1 2 3 1 2 3 1 2 3 [14] R. E. Bryant, “Graph-based algorithms for Boolean function manipulation,” IEEE Trans. Comput., vol. C-37, pp. 677-691, Aug., 1986. 2011-11-25 10

Reduced Ordered BDD Reduced Ordered BDD Canonical and Compact! 0 1 Order: x1 > x2 > x3 1 1 0 0 0 0 1 1 1 1 0 1 0 1 0 0 f x x ( , , x ) x x x x x x x x x x x x f x x x ( , , ) x x x x x x x 1 2 3 1 2 3 1 2 2 3 1 2 3 1 2 3 1 2 3 1 2 3 1 2 3 [14] R. E. Bryant, “Graph-based algorithms for Boolean function manipulation,” IEEE Trans. Comput., vol. C-37, pp. 677-691, Aug., 1986. 2011-11-25 11

Determinant Decision Diagram Determinant Decision Diagram • R Represent a determinant by BDD d i b BDD • Treat Laplace Expansion as binary decisions 1 edge a 0 edge d d c c a b f g b c d e det( ) det( ) A A f g h j i e i j adgj adhi aefj bcgj cbih h 1 1 0 2011-11-25 12

Minor Sharing [25] Minor Sharing [25] a b c c d d e e f g h i j 0 b d d e e c c d d e e a f g h f g h i j i j d d c c g h b f g h i j f g b i j j j i e h 1 1 0 0 [25] G. Shi, “A simple implementation of determinant decision diagram,” in Proc. International Conf. on 2011-11-25 13 Computer-Aided Design (ICCAD) , San Jose, CA, USA, Nov. 2010.

Graph Pair Reduction Diagram Graph Pair Reduction Diagram • Represent the transfer function by BDD • Treat Spanning-Tree Enumeration as binary decisions x + + + 2 1 R R R + C + + V o V s C C - - 0 + 1 0 2011-11-25 14

Graph Pair Sharing [16] Graph Pair Sharing [16] R R 1 1 2 2 1 1 2 2 2 1 1/R 2 Vs C Vs C CS Vc Vs Vc 0 0 0 0 x x 0 2 2 + + R R C C 2 0 R R R R R R 0 0 R C + + + 0 1 2 2 C C - C C 0 0 + 1 0 [16] G. Shi, W. Chen, and C.-J. R. Shi, “A graph reduction approach to symbolic circuit analysis,” in Proc. Asia South-Pacific Design Automation Conference (ASPDAC) , Yokohama, Japan, Jan. 2007, pp. 197–202. 2011-11-25 15

Hash Mechanisms Hash Mechanisms • DDD – By Hashing Minors Minor 1 Minor 1 Minor 2 Minor 2 Minor 3 Minor 3 d e b g h f g h f g h i i j j i j i j • GPDD – By Hashing subgraphs • GPDD – By Hashing subgraphs Graph Pair 1 Graph Pair 2 Graph Pair 3 2 2 2 0 2 2 R R R C R C C C C 0 1 0 0 0 0 2011-11-25 16

Idea of “Symbolic Stamp”

Symbolic Stamp Symbolic Stamp VDD M8 M5 M7 Bias P In- In+ M1 M2 Out C L Rz Cc X Y M3 M3 M4 M4 M6 M6 All MOSFETs use the same small-signal All MOSFET th ll i l model! Circuits are naturally hierarchical! 2011-11-25 18

Assembling Symbolic Stamps Assembling Symbolic Stamps 1 3 4 A C p 1 p 2 p 2 p 1 n 1 n 2 n 3 n 4 A A n 1 y y 11 12 p 2 B B n 2 y y 11 12 B B C C C C n 3 3 y y 11 12 A B C A B C n 4 y y y y y y p 1 21 21 21 22 22 22 2 DDD Routine 2011-11-25 19

Procedure 2. Build symbolic stamp of each sub-block A multi-root GRDD containing the 4 y- parameters y y 1/ 1/ R R 1/ 1/ R R 11 12 GPDD y y 1/ R 1/ R 21 22 Date 2011-11-25

Symbolic R Stamp (y ) Symbolic R Stamp (y 11 ) i t 1 1 + + 1 Vs Vs R n V t n R R y 11 Cc Cc - 0 0 0 X 1 1 - + 0 0 R R 1 R 0 0 0 + + + + 0 1 1 1 0 0 0 0 0 Date 2011-11-25 Page 21

Symbolic R Stamp (y ) Symbolic R Stamp (y 12 ) i t + + R R 1 2 1 2 1 2 R V t Cc Cc Vs Vs y 12 y 12 0 0 0 - X R - 1 0 + 0 0 R 0 2 R 1 0 - + 0 0 0 0 0 1 1 0 0 0 0 Date 2011-11-25 Page 22

Symbolic Stamp Computation Symbolic Stamp Computation i 2 i 1 2 1 + + + y y G G G = 1/R 11 12 y V 1 V 2 y y G G 21 22 - - y 11 y 22 y 12 y 21 + + + + + + + + + + G G + + + - 1 0 Four-root GPDD for R symbolic stamp 2011-11-25 23

Why GPDD for symbolic stamp Why GPDD for symbolic stamp GPDD DDD n 1 n 2 n 3 n 4 A A n n 1 1 y y y y 11 11 12 12 i 2 i 1 B B n 2 y y + 11 12 C C G = 1/R n 3 y y 11 12 V 1 V 1 V 2 V 2 A B C A B C n 4 y y y y y y 21 21 21 22 22 22 - Dire Ind ect Link direct Link k G S 2011-11-25 24

Hierarchical Structure Hierarchical Structure H( ) H(s) freq HYBRIDSIM MNA Matrix Simulator (DDD) Sub-circuit 1 Sub-circuit 2 Sub-circuit 3 Symbolic Stamp Symbolic Stamp Symbolic Stamp (Multi-root GPDD) (Multi-root GPDD) (Multi-root GPDD) DEVICE DEVICE DEVICE DEVICE 2011-11-25 25

Experimental Results

Implementation Flow Implementation Flow Will be integrated into our program in the future .Op New New Netlist (Now use Netlist HSPICE) Small Signal Model Extraction Analog Design GUI Analog Design GUI H(s) Symbolic H s p H s p ( ; ) ( ; ) analysis analysis engine freq q 2011-11-25 27

Platform Environment Platform Environment • Programming Language and tools: – C++ • Test cases are running on an AMD Athlon64 Test cases are running on an AMD Athlon64 2.20GHz processor with 2GB memory • HSPICE 2007 is used for DC operating point analysis l i 2011-11-25 28

Benchmark 1 Benchmark 1 • A rail-to-rail Miller MOSFET amplifier containing 24 transistors 2011-11-25 29

Benchmark 2 Benchmark 2 • A MOSFET operational amplifier containing 44 transistors [26] [26] T McConaghy and G G E Gielen “Globally reliable variation aware sizing of analog integrated circuits via response surfaces and [26] T. McConaghy and G. G. E. Gielen, Globally reliable variation-aware sizing of analog integrated circuits via response surfaces and structural homotopy,” IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems , vol. 28, no. 11, pp. 1627–1640, Nov. 2009. 2011-11-25 30

MOSFET Small Signal Model MOSFET Small Signal Model • All MOSFETs share one symbolic stamp of the model the model 12 symbols 481 vertices in 481 vertices in the multi-root GRDD Date 2011-11-25 Page 31

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.