Graphics Hardware Hardware Overview of Pipeline Architecture - PDF document

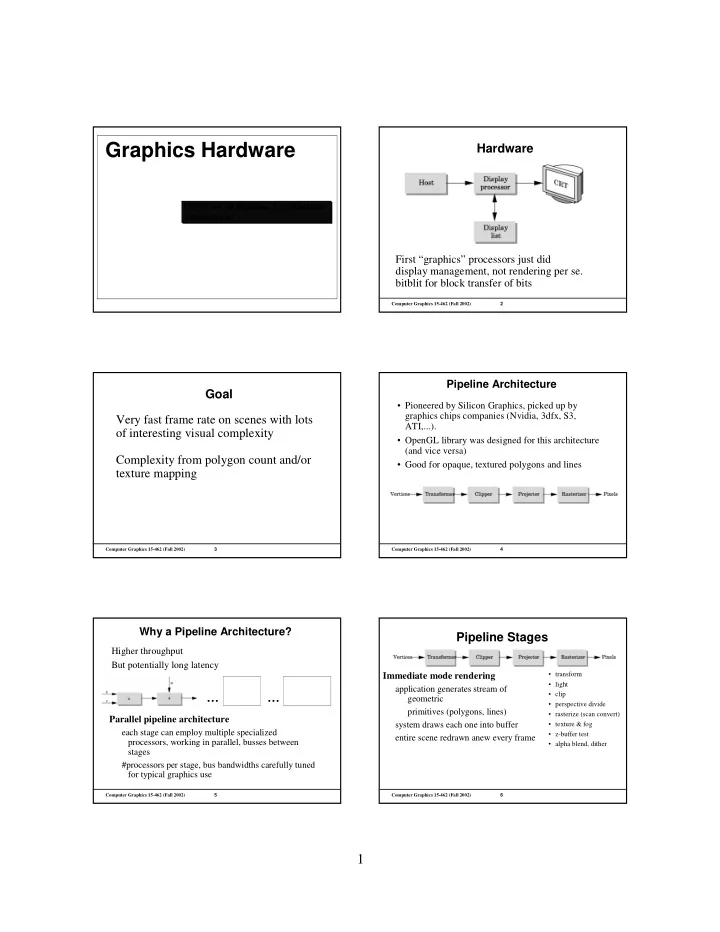

Graphics Hardware Hardware Overview of Pipeline Architecture Alternatives First graphics processors just did display management, not rendering per se. bitblit for block transfer of bits Computer Graphics 15-462 (Fall 2002) 2 Pipeline

Graphics Hardware Hardware Overview of Pipeline Architecture Alternatives First “graphics” processors just did display management, not rendering per se. bitblit for block transfer of bits Computer Graphics 15-462 (Fall 2002) 2 Pipeline Architecture Goal • Pioneered by Silicon Graphics, picked up by graphics chips companies (Nvidia, 3dfx, S3, Very fast frame rate on scenes with lots ATI,...). of interesting visual complexity • OpenGL library was designed for this architecture (and vice versa) Complexity from polygon count and/or • Good for opaque, textured polygons and lines texture mapping Computer Graphics 15-462 (Fall 2002) 3 Computer Graphics 15-462 (Fall 2002) 4 Why a Pipeline Architecture? Pipeline Stages Higher throughput But potentially long latency • transform Immediate mode rendering • light application generates stream of • clip … … geometric • perspective divide primitives (polygons, lines) • rasterize (scan convert) Parallel pipeline architecture system draws each one into buffer • texture & fog each stage can employ multiple specialized • z-buffer test entire scene redrawn anew every frame processors, working in parallel, busses between • alpha blend, dither stages #processors per stage, bus bandwidths carefully tuned for typical graphics use 5 6 Computer Graphics 15-462 (Fall 2002) Computer Graphics 15-462 (Fall 2002) 1

Implementing Algorithms in Hardware Implementing Algorithms in Hardware • Ray tracing Some work well, others are harder poor memory locality • Z-buffer computational cost difficult to predict (esp. if adaptive) computations are bounded, predictable SIMD (single instruction, multiple data) parallel approach keep copy of entire scene on each processor Computer Graphics 15-462 (Fall 2002) 7 Computer Graphics 15-462 (Fall 2002) 8 Current chip design may not be the Pixel Planes and Pixel Flow (UNC) long term answer http://www.cs.unc.edu/~pxfl/ • Observation: # triangles == # of pixels programmable processor per pixel • Could focus on interactivity good for programmable shading, image processing Latency becomes a problem can be used for rasterization • Could focus on animation Pixel-Planes 4: 512x512 processors with 72bits of memory Avoid repeating computations But most processors idle for most triangles Image-based rendering? Pixel-Planes 5: divide screen into ~20 tiles each with a bank of processors. Network is limit. 2Million tri/sec. Computer Graphics 15-462 (Fall 2002) 9 Computer Graphics 15-462 (Fall 2002) 10 Pixel Planes and Pixel Flow (UNC) Talisman (Microsoft) Pixel-Flow: Image composition. Subdivide geometry to http://research.microsoft.com/MSRSIGGRAPH/96/Talisman/ processors and recombine by depth using special hardware Observation: an image is usually much like the one Rendered on simulator and predicted to run in real that preceded it in an animation. time on physical hardware Goal: a $200-300 board image-based rendering cache images of rendered geometry re-use with affine image warping (sophisticated sprites) re-render only when necessary to reduce bandwidth and computational cost 11 12 Computer Graphics 15-462 (Fall 2002) Computer Graphics 15-462 (Fall 2002) 2

Current & Future Issues Assignment 1 • interaction • geometry compression • progressive transmission • alternative modeling schemes (not polygon soup) Height Fields parametric surfaces, implicit surfaces, subdivision surfaces generalized texture mapping: displacement mapping, light mapping programmable shaders • beyond just geometry: dynamics, collision detection, AI? Computer Graphics 15-462 (Fall 2002) 13 Height Fields Height Fields • Why? • What? Get started with OpenGL Some room for creativity • Where? Wean 5336 or your machine at your risk! • How? Cross-realm authentication via andrew Send problems to me or to the TA’s (soon) Make sure that you made directory with correct • When? -- Due midnight September 12th permissions—most common problem Computer Graphics 15-462 (Fall 2002) 15 Computer Graphics 15-462 (Fall 2002) 16 3

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.