Finite State Machines CS 3410 Computer System Organization & - PowerPoint PPT Presentation

Finite State Machines CS 3410 Computer System Organization & Programming [K. Bala, A. Bracy, E. Sirer, and H. Weatherspoon] Stateful Components Combinational logic Output computed directly from inputs System has no internal state

Finite State Machines CS 3410 Computer System Organization & Programming [K. Bala, A. Bracy, E. Sirer, and H. Weatherspoon]

Stateful Components Combinational logic Output computed directly from inputs • System has no internal state • Nothing depends on the past! • Combinational Inputs Outputs N circuit M Need: to record data • to build stateful circuits • a state-holding device • Enter: Sequential Logic & Finite State Machines 2

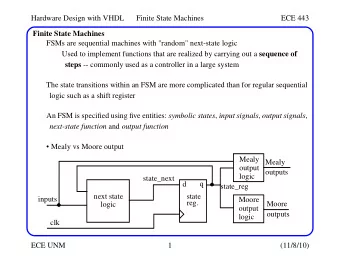

Finite State Machines An electronic machine which has ◦external inputs ◦externally visible outputs ◦internal state Output and next state depend on ◦inputs ◦current state 3

Automata Model Finite State Machine Current Output Registers State Comb. Logic Input Next State ◦inputs from external world ◦outputs to external world ◦internal state ◦combinational logic 4

FSM Example start input/output state 0/0 state state 0/0 1/0 B A Legend 1/1 Input: 1 or 0 Output: 1 or 0 What input pattern is States: A or B the FSM “looking for”? [Mealy Machine] 5

Mealy Machine General Case: Mealy Machine Current Output Registers State Comb. Logic Input Next State Outputs and next state depend on both current state and input 6

Moore Machine Outputs depend only on current state Current Comb. Output Registers Logic State Comb. Input Next State Logic 0 1 start input state 1 A B C 0 0 0 1 state state out out 0 Legend 1 7

xkcd 8

Why FSMs? They help us reason about complex behavior. Clicker Question: waits What kind of machine is wags this? barks tail gets petted (A) Mealy (B) Moore sees squirrel d e t t (C) Neither e p s t e g sits doesn’t give a crap about you ! r e v e t n e v e y n a https://learnyousomeerlang.com/finite-state-machines 9

Other FSMs Tennis http://blog.mikemccandless.com/201 4/08/scoring-tennis-using-finite- state.html 10 https://www.c-sharpcorner.com/article/understanding-state-design-pattern-by-implementing-finite-state/

Activity: Build a Circuit for a Serial Adder Add two infinite input bit streams ◦streams sent with least-significant-bit (lsb) first …10110 …00101 …01111 Clicker Question: How many states are needed to represent this FSM? (a) 0 (d) 3 (b) 1 (e) 4 (c) 2 11

Strategy for Building an FSM (1) Draw a state diagram (2) Write output and next-state tables (3) Encode states, inputs, and outputs as bits (4) Determine logic equations for next state and outputs (5) Draw the circuit 12

Step 1: State Diagram start input/output state state state S0 Legend …10110 …00101 …01111 States: Inputs: a and b (drawn as 2-bit input ab) Output: z 13

Strategy for Building an FSM (1) Draw a state diagram (2) Write output and next-state tables (3) Encode states, inputs, and outputs as bits (4) Determine logic equations for next state and outputs (5) Draw the circuit 15

Step 2: Output & Next State Tables Curr Next a b State z State s s’ 16

Strategy for Building an FSM (1) Draw a state diagram (2) Write output and next-state tables (3) Encode states, inputs, and outputs as bits (4) Determine logic equations for next state and outputs (5) Draw the circuit 18

Step 3: Create Bit Encoding Curr Next Encode states as bits a b State z State s’ s S0 = S1 = 2 states à 1-bit enough (1-hot also an option) Copy from previous Make a binary encoding instead of names 19

Strategy for Building an FSM (1) Draw a state diagram (2) Write output and next-state tables (3) Encode states, inputs, and outputs as bits (4) Determine logic equations for next state and outputs (5) Draw the circuit 21

Step 4: Create Logic Equations Determine logic equations for next state and outputs s’ = z = 22

Strategy for Building an FSM (1) Draw a state diagram (2) Write output and next-state tables (3) Encode states, inputs, and outputs as bits (4) Determine logic equations for next state and outputs (5) Draw the circuit: Simplify first! 24

Step 5: Draw the Circuit Output Next Current State State z s' s D Q a b s' 25

FSMs in a Processor? • multi-cycle (non-pipelined) processor 27

FSMs in a Processor? • multi-cycle (non-pipelined) processor • handling cache misses, branch mispredictions, interrupts • tracking the state of data in your cache (cache coherency) 28

Consider a finite state machine that takes two inputs, A and B, and generates a single output, Z. Inputs are unsigned binary numbers, entered into the FSM one digit at a time, beginning with the most significant digit. The output, Z, should be the larger of the two numbers. Example: A = 1000 and B = 0101, then Z = 1000 (the value of A). Draw the state transition diagram (states & arrows) that expresses this FSM. Use the notation AB for inputs (10 means A = 1 and B = 0). (1) Draw a state diagram (2) Write output and next-state tables (3) Encode states, inputs, and outputs as bits (4) Determine logic equations for next state and outputs (5) Draw the circuit 29

Clicker Question: How many states are needed to represent this FSM? (a) 0 (d) 3 (b) 1 (e) 4 (c) 2 30

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.