EE 457 Unit 1 Overview of Digital System Design 1.2 Credits These - PowerPoint PPT Presentation

1.1 EE 457 Unit 1 Overview of Digital System Design 1.2 Credits These slides were derived from Gandhi Puvvadas EE 457 Class Notes 1.3 TRI-STATE OUTPUTS & BUSES 1.4 Typical Logic Gate Gates can output two values: 0 & 1

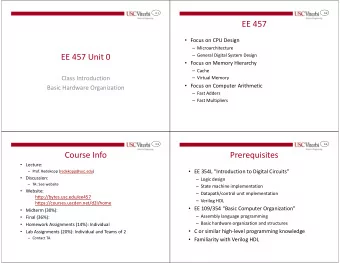

1.1 EE 457 Unit 1 Overview of Digital System Design

1.2 Credits • These slides were derived from Gandhi Puvvada’s EE 457 Class Notes

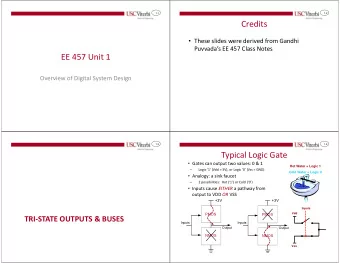

1.3 TRI-STATE OUTPUTS & BUSES

1.4 Typical Logic Gate • Gates can output two values: 0 & 1 Hot Water = Logic 1 – Logic ‘1’ ( Vdd = 3V), or Logic ‘0’ ( Vss = GND) Cold Water = Logic 0 • Analogy: a sink faucet – 2 possibilities: Hot (‘1’) or Cold (‘0’) • Inputs cause EITHER a pathway from output to VDD OR VSS +3V +3V Inputs Vdd PMOS PMOS Inputs Inputs Output Output NMOS NMOS Vss

1.5 Output Connections • Can we connect the output of two logic gates together? • No! Possible short circuit (static, low-resistance pathway from Vdd to GND) • We call this situation “bus contention” Inputs Vdd Src 1 Src 1 Vss Src 2 Inputs Vdd Src 2 Src 3 Vss

1.6 Tri-State Buffers +3V • Gates can output two values: 0 & 1 1. Logic 0 = 0 volts PMOS 2. Logic 1 = 5 volts Inputs Output • Tristate buffers can output a third Z (high value: impedance) NMOS 3. Z = High-Impedance (no connection to any voltage source) • Analogy: a sink faucet – 3 possibilities: 1.) Hot water, 2.) Cold water, 3.) NO water Hot Water = Logic 1 Cold Water = Logic 0 NO Water = Z (High-Impedance)

1.7 Tri-State Buffers • Tri-state buffers have Tri-State Buffer an extra enable input In Out • When disabled, output E is Z Enable • When enabled, normal buffer En In Out 0 x Z 1 0 0 1 1 1

1.8 Tri-State Buffers • We use tri-state buffers to share one output amongst several sources • Rule: Only 1 buffer enabled at a time Src 1 E EN1 Src 2 D Q E D-FF EN2 Q CLK Src 3 E EN3

1.9 Tri-State Buffers • We use tri-state buffers to share one output amongst several sources • Rule: Only 1 buffer enabled at a time • When 1 buffer enabled, its output overpowers the Z’s (no connection) from the other gates 0 0 output of 0 E Select source overpowers 1 to pass its 1 the Z data 0 1 Z D Q E D-FF 0 Q CLK 0 Z Disabled E buffers output ‘Z’ 0

1.10 Communication Connections • Multiple entities need to communicate • We could use – Point-to-point connections – A shared bus (set of wires) Separate point to point connections Shared Bus

1.11 Bidirectional Bus • 1 transmitter (otherwise bus contention) • N receivers • Each device can send (though 1 at a time) or receive 0 1 0 0

1.12 Tri-State Buffer / Bussing Summary • Provide a 3 rd output value: Z (high impedance) • Allows multiple outputs to be wired together • Only one bus driver can be enabled at a time

1.13 MICROARCHITECTURE EXAMPLE

1.14 Digital Design Goals • Digital systems seek to optimize a design along these three axes: Area – Area (size) Power – Speed – Power Consumption Speed • Can often only optimize one or two of these without sacrificing the other(s) – Just as in software design, there is a classic time/space trade-off – Microarchitecture can determine where a design falls in this trade space

1.15 Different Architectures Single Bus Two-Bus Three Bus R0 R0 R0 R1 R1 R1 Rn Rn Rn Y Reg. Y Reg. Y Reg. ALU ALU ALU Z Reg. Z Reg. Z Reg. Clock 1: Y = Rsrc1 Clock 1: Z = Rsrc1 + Rsrc2 Clock 1: Rdst = Rsrc1 + Rsrc2 Clock 2: Z = Rsrc2 + Y Clock 2: Rdst = Z Clock 3: Rdst = Z General Implications: Less Resources => More Clock Cycles (Time)

1.16 Clocking Strategies REGISTERS & DATA ENABLES

1.17 Registers Q0 D0 D Q • A Register is a group of D- FF’s CLR tied to a common clock and clear (reset) input D1 Q1 D Q – Clear can be asynchronous or CLR synchronous • Used to store multiple bit D Q Q2 D2 values on each clock cycle CLR D3 D Q Q3 CLK RST D i Q i * CLR 1,0 X X Q i ↑ 1 X 0 RST ↑ CLK 0 0 0 ↑ 0 1 1 4-bit Register

1.18 Example: Accumulator • Sum a time-based sequence of numbers • A register usually stores a single logic value (i.e. a number) time 9, 3, 2 Clock Y0 Z0 X0 A0 S0 D Q Reset X1 A1 CLR X2 A2 Y1 Z1 S1 D Q X3 A3 2 3 9 X 4-bit CLR Adder Y2 Z2 B0 S2 D Q B1 CLR 2 5 14 Y Y3 Z3 B2 S3 D Q B3 CLR Z 0 2 5 14 Clock Reset Register

1.19 Synchronous vs. Asynchronous • The set/preset and clear inputs can be built to be synchronous or asynchronous • These terms refer to when the initialization takes place – Asynchronous Reset (AR): Initialization of Q takes effect immediately regardless of the CLK – Synchronous Reset (SR): Initialization of Q takes effect only at an edge (clear must be active at the edge) Synchronous Asynchronous Clock Clock CLR CLR Q s Q s Synchronous SET or CLR Asynchronous SET or CLR means the signal must be means Q will initialize as soon active at a clock edge before as the SET or CLR signal is Q will initialize activated

1.20 Registers • Whatever the D value is at the clock edge is sampled and passed to the Q output until the next clock edge CLK RST D[3:0] 0011 0100 0010 0101 0110 0111 1000 1001 1010 Q[3:0] ? 0000 0011 0100 0101 0110 0111 1001 1000 4-bit Register – On clock edge, D is passed to Q

1.21 Selective Loading/Registering of Data • What if we only want a register D0 D Q Q0 to capture data on selective CLR clocks (and not on EVERY clock) Q1 D1 D Q – Clocks are indicated with a “LOAD” CLR signal D2 D Q Q2 CLR D3 D Q Q3 SYSCLK CLR LOAD RST CLK Want to load the register on the indicated clock cycles and have it retain its value in the 4-bit Register other cycles

1.22 Clocking Option 1 • Use Load as the clock signal • Doesn’t Work. Clocks too early D0 Q0 D Q CLR Q1 D1 D Q CLR Desired Load time D Q Q2 D2 SYSCLK CLR LOAD D3 D Q Q3 CLR RST Actual Load LOAD = CLK time

1.23 Clocking Option 2 • Use ~Load (inverted Load) as the D0 Q0 D Q clock signal CLR • Doesn’t Work…Glitches or Q1 D1 D Q successive loading cycles CLR Desired D Q Q2 D2 Load time CLR SYSCLK D Q Q3 D3 ~ LOAD CLR RST ~LOAD = CLK Actual Load time

1.24 Glitches • Temporary (transient) incorrect / toggling output values due to differing delay paths of the inputs – Eventually output settles to correct value – Unless a circuit is specially designed, glitches are possible on all circuits 1 ns delay F A 0 ns B A B F

1.25 Successive Loading Clocks • If load is held high on two successive clock cycles you may only see one edge SYSCLK LOAD

1.26 Option 3 Q0 D0 D Q • Gate the clock with the load CLR signal • Also susceptible to glitches D1 Q1 D Q CLR Q2 D2 D Q CLR D3 D Q Q3 CLR RST CLK 4-bit Register

1.27 Option 4: Feedback mux • Registers (D- FF’s) will sample the D bit every clock edge and pass it to Q 1 0 • Sometimes we may want to hold the SET D Q Q Y value of Q and ignore D even at a D 1 S CLR clock edge EN CLK • We can add an enable input and /AR some logic in front of the D-FF to FF with Data Enable accomplish this (Always clocks, but selectively chooses old value, Q, or new value D) CLK /AR EN D i Q i * X 0 X X 0 0,1 1 X X Q i ↑ 1 0 X Q i ↑ 1 1 0 0 ↑ 1 1 1 1

1.28 Option 4: Feedback mux • Registers (D- FF’s) will sample the D bit every clock edge and pass it to Q 0 Q Y D Q • Sometimes we may want to hold the D 1 S CLR value of Q and ignore D even at a EN clock edge CLK RST AR • We can add an enable input and some logic in front of the D-FF to FF with Data Enable accomplish this (Always clocks, but selectively chooses old value, Q, or new value D) CLK AR EN D i Q i * X 1 X X 0 0,1 0 X X Q i ↑ 0 0 X Q i ↑ 0 1 0 0 ↑ 0 1 1 1

1.29 Registers w/ Enables • When EN=0, Q value is Q 0 Q Q Y D Q 1 D passed back to the input S CLR 0 EN and thus Q will maintain its CLK RST value at the next clock edge When EN=0, Q is • When EN=1, D value is recycled back to the input passed to the input and thus Q will change at the 0 D Q Y D Q edge based on D D D 1 S CLR 1 EN CLK RST When EN=1, D input is passed to FF input

1.30 Registers w/ Enables • The D value is sampled at the clock edge only if the enable is active • Otherwise the current Q value is maintained CLK RST EN D[3:0] 0011 0100 0010 0101 0110 0111 1000 1001 1010 Q[3:0] 0000 0101 0111 1000

1.31 Register With or Without An Enable Free-Running Register Register with Load (Data) Enable 0 Q0 D0 Q0 Y D Q D Q D0 1 S CLR CLR 0 Q1 Y D Q D1 Q1 D Q D1 1 S CLR CLR 0 Y D Q Q2 D Q Q2 D2 1 D2 S CLR CLR 0 Y D Q Q3 D Q Q3 D3 1 D3 S CLR CLR EN RST RST CLK CLK When to use one vs. the other? • Free-running register: Do you want to update the stored value EVERY edge • Register w/ Enable: In all other cases…

1.32 Counters • Increment (Add 1 to Q) at each clock edge Adder (+) Q – Up Counter: Q* = Q + 1 Register 1 • Standard counter components RESET include other features CLK – Enables: Will not count at edge if EN=0 – Resets: Reset count to 0 – Parallel Load Inputs: Can initialize count to a value P (i.e. Q* = P rather than Q+1)

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.