EE 209 in Context Hardware / Software Systems EE 109L (Assembly - PowerPoint PPT Presentation

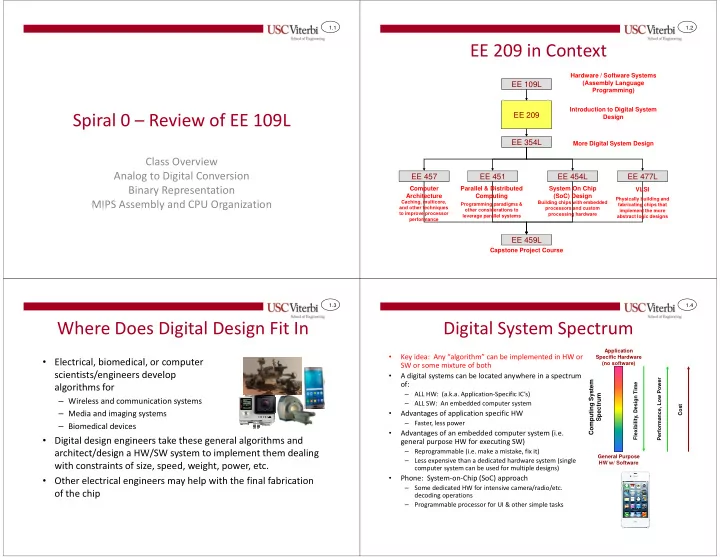

1.1 1.2 EE 209 in Context Hardware / Software Systems EE 109L (Assembly Language Programming) Introduction to Digital System Spiral 0 Review of EE 109L EE 209 Design EE 354L More Digital System Design Class Overview Analog to

1.1 1.2 EE 209 in Context Hardware / Software Systems EE 109L (Assembly Language Programming) Introduction to Digital System Spiral 0 – Review of EE 109L EE 209 Design EE 354L More Digital System Design Class Overview Analog to Digital Conversion EE 457 EE 451 EE 454L EE 477L Binary Representation Computer Parallel & Distributed System On Chip VLSI Architecture Computing (SoC) Design Physically building and MIPS Assembly and CPU Organization Caching, multicore, Building chips with embedded Programming paradigms & fabricating chips that and other techniques processors and custom other considerations to implement the more to improve processor processing hardware leverage parallel systems abstract logic designs performance EE 459L Capstone Project Course 1.3 1.4 Where Does Digital Design Fit In Digital System Spectrum Application • Key idea: Any “algorithm” can be implemented in HW or Specific Hardware • Electrical, biomedical, or computer SW or some mixture of both (no software) scientists/engineers develop • A digital systems can be located anywhere in a spectrum Computing System Performance, Low Power of: Flexibility, Design Time algorithms for – ALL HW: (a.k.a. Application-Specific IC’s) Spectrum – Wireless and communication systems – ALL SW: An embedded computer system Cost – Media and imaging systems • Advantages of application specific HW – Faster, less power – Biomedical devices • Advantages of an embedded computer system (i.e. • Digital design engineers take these general algorithms and general purpose HW for executing SW) – architect/design a HW/SW system to implement them dealing Reprogrammable (i.e. make a mistake, fix it) General Purpose – Less expensive than a dedicated hardware system (single HW w/ Software with constraints of size, speed, weight, power, etc. computer system can be used for multiple designs) • Phone: System-on-Chip (SoC) approach • Other electrical engineers may help with the final fabrication – Some dedicated HW for intensive camera/radio/etc. of the chip decoding operations – Programmable processor for UI & other simple tasks

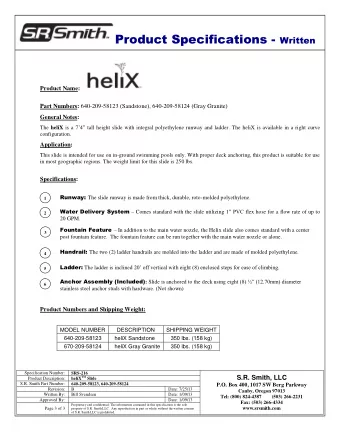

1.5 1.6 Processing Logic Approaches HW/SW Design Example • Suppose you need to design a JPEG encoder (converts raw pixels to JPG format…consisting of a preprocessing stage + encoding stage) for the camera on your mobile phone • Custom Logic X + • Your design considerations requirements – Logic that directly implements a Y Out – specific task 1 second max. latency (time) * – 200 mW max power – Example above may use separate A adders and a multiplier unit – Energy (Power * Time) as low as possible + • General Purpose Processor – Consider time to market (design time) and cost B • Options – Logic designed to execute SW Custom Logic Circuit instructions 1. Software only running on microcontroller/processor Implementation 2. Hardware preprocessor + Software encoder – Provides basic processing resources 3. Hardware preprocessor + Fixed-point software encoder that are reused by each instruction 4. Hardware preprocessor + encoder Data storage Instruc. • Design Decision: HW only or Store Option 1 Option 2 Option 3 Option 4 HW/SW ADD X,Y Performance (sec.) > 10 9.1 1.5 0.1 – HW only = faster + * ADD A,B Power (milliwatt) < 200 33 33 40 – HW/SW = much more flexible MUL X,A Size (gates) N/A 98,000 90,000 128,000 Energy (Joules=sec*watt) 0.3 0.05 0.004 GPP Implementation of (X+Y)*(A+B) Time to Market 3 months 6 months 8 months 12 months Taken from "Embedded System Design" by Vahid and Givargis, Wiley and Sons Publishing 2002. 1.7 1.8 Mobile Phone Block Diagram Integrated Solutions: Systems-On-Chip • Chips now combine general purpose processing, hardware Sensors Digital Outputs Processing accelerated engines for things Microprocessors Analog to Digital to like comm., video, security, etc., (Software for Analog Digital Analog Speaker, User Interface Inputs Conversion Conversion LCD Control) and integrated I/O peripherals Qualcomm Snapdragon TM (Radio, (ADC) (DAC) Display, Interconnect Interconnect WiFi, Antenna Clock sensors) • Some contain customizable Reset hardware resources (FPGAs) for Digital USB Custom Logic custom hardware processing Inputs (JPEG (USB, Encoding) engines Buttons) Xilinx Zynq MPSoC

1.9 1.10 Digital System Abstraction Levels if (x > 0) CMPR X,0 x = x + y - z; JLE SKIP a = b*x; Software ADD X,X,Y Code SUB X,X,Z SKIP MUL A,B,X Applications Chips C / C++ / Java SW 1110010101… (Processors) OS Libraries Assembly / Machine Code A S Functional Processor / Memory / I/O How are we going to go about this class + B Units Functional Units LEARNING (Registers, Adders, Muxes) x AND Logic F Our Focus in EE 209 y HW gate Logic Gates z - - - - Output Transistors (Drain ) - - - Controlling Transistors Input (Gate ) Voltage / Currents Source 1.11 1.12 Reflecting on Learning Concept Map SystemC SoC / Structural RTL Programmable (Gate) MPSoC Code Hardware VHDL Logic (FPGA) Level • Bjork's Presentation Description Standard Behavioral Languages Cell Layout vs. Cycle Verilog / ASIC Accurate System • Spiral Model (Interleaving) Target Design Verilog Custom or Implementation Entry Semi-Custom Technology • We need to be a team? Layout Schematic Process / Entry VLSI – I need you Digital HW Technology Design CMOS – You need me MOSFET Boolean Simulation • What do you want to learn? Algebra EDA (CAD) Constructs HW / SW Co- Combinational Tools – I will be your guide and try to build experiences Simulation Logic (Gates) Physical Design Adders (Layout & Sequential Synthesis Routing) Logic Power / Multiplexers Timing State Registers & High-Level Analysis Machines Counters Synthesis

1.13 1.14 Spiral Content Mapping Combinational Sequential System Level Implementation Spiral Theory Project Design Design Design and Tools • Performance • Decoders and • Structural Verilog 1 metrics (latency muxes • Edge-triggered HDL vs. throughput) • Synthesis with flip-flops • Encoded State • CMOS gate • • Boolean Algebra min/maxterms Registers (with machine design implementation • Canonical • Synthesis with enables) • Fabrication Representations Karnaugh Maps process • Synthesis with 2 • Bistables, • One-hot state • MOS Theory muxes & latches, and Flip- machine design • Capacitance, • Shannon's memory flops • Control and delay and sizing Theorem • Adder and • Counters datapath • Memory comparator • Memories decomposition constructs design 3 • HW/SW • Power and other REVIEW partitioning logic families • Bus interfacing • EDA design • Single-cycle CPU process 1.15 1.16 Analog to Digital Conversion ADC Conversion • Sampling converts continuous time scale to a discrete (finite) • 1 Analog signal can be converted to a set of digital set of voltage samples signals (0’s and 1’s) • Quantization converts continuous voltage scale to a discrete • 3 Step Process (finite) set of numbers – Sample • Each number is then output as bits – Quantize (Measure) – Digitize 255 11000 1 volts 0 1 Analog to 177=10110001 0 1 Digital 0 Converter 1 0 1 0 time time 000 ∆ t Analog Digital Sampled Signal Each sample is quantized

1.17 1.18 Interpreting Binary Strings Unsigned and Signed Variables • Given a string of 1’s and 0’s, you need to know the • Unsigned variables use unsigned binary (normal representation system being used, before you can power-of-2 place values) to represent numbers understand the value of those 1’s and 0’s. • Information (value) = Bits + Context (System) 1 0 0 1 0 0 1 1 = +147 128 64 32 16 8 4 2 1 01000001 = ? • Signed variables use the 2’s complement system Unsigned Binary system ASCII (Neg. MSB weight) to represent numbers system 1 0 0 1 0 0 1 1 = -109 65 10 ‘A’ ASCII -128 64 32 16 8 4 2 1 Signed System 1.19 1.20 2’s Complement System Zero and Sign Extension • Extension is the process of increasing the number of bits used • MSB has negative weight to represent a number without changing its value • MSB determines sign of the number – 1 = negative Unsigned = Zero Extension (Always add leading 0’s): – 0 = positive 111011 = 00111011 • Positive numbers retain same representation as unsigned – 0110 = +6 in unsigned and in 2's complement Increase a 6-bit number to 8-bit number by zero extending • To take the negative of a number requires taking the 2’s complement = Sign Extension (Replicate sign bit): complement pos. 011010 = 00011010 0111 x = +7 1001 x = -7 Sign bit is just repeated as many times as necessary neg. 110011 = 11110011 1000 Bit flip (1’s comp.) 0110 Bit flip (1’s comp.) + 1 Add 1 Add 1 + 1 1001 -x = -(+7) = -7 0111 -x = -(-7) = +7

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.