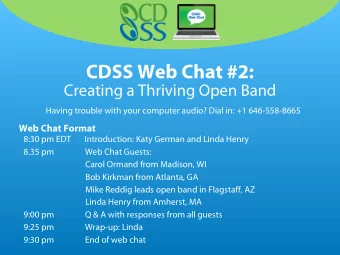

DSN02 Block Diagram. Use CORDIC IP Core. Counter limit n step - PowerPoint PPT Presentation

DSN02 Block Diagram. Use CORDIC IP Core. Counter limit n step wrap clock reset enable Counter Counter CORDIC 2 N limit n limit n Addr COS step wrap step wrap SIN 1 clock clock clock reset reset reset enable

DSN02 • Block Diagram. • Use CORDIC IP Core. Counter limit n step wrap clock reset enable Counter Counter CORDIC 2 N limit n limit n Addr COS step wrap step wrap SIN 1 clock clock clock reset reset reset enable enable enable

Example • CReSIS UWB Depth Sounder • Programmable bandwidth: 150 to 600 MHz. • 1.6-GSPS, 12-Bit Digitizer. • 24 Independent Channels. • Data Rate • Maximum • 24*1.6e9*12/8 = 57.6 GB/sec • Typically 8 hour flight • 8*3600 = 28800 sec • ~1.6 PB per flight • 6 weeks in the field (30 flight day) • ~50 PB of data • Need to rely on on-board processing in real-time to reduce the data rate level. to a manageable

Example: Wideband Operation Flow Diagram ADC I/F 1.6 GSPS

Example: Narrow band operation Flow Diagram Band Select ADC I/F I/Q 1.6 GSPS Down decimate Conversion 180-200 MHz

Example Flow Diagram ADC I/F I/Q 1.6 GSPS Down decimate ? Conversion 180-200 MHz Filter to Reduce noise

Example Flow Diagram Band Select ADC I/F I/Q Band Select 1.6 GSPS Down decimate BPF Conversion 180-200 MHz 180-200 MHz

Example Flow Diagram ADC I/F I/Q Band Select 1.6 GSPS Down decimate BPF Conversion 180-200 MHz 180-200 MHz can we make it more ADC I/F I/Q robust. 1.6 GSPS Down ... Conversion decimate

Example Flow Diagram ADC I/F I/Q Band Select 1.6 GSPS Down BPF Conversion 180-200 MHz 180-200 MHz ADC I/F I/Q 1.6 GSPS Down ? ... Conversion

Example Flow Diagram ADC I/F I/Q Band Select 1.6 GSPS Down BPF Conversion 180-200 MHz 180-200 MHz ADC I/F I/Q 1.6 GSPS Down LPF ... Conversion 800 MHz

Example Flow Diagram ADC I/F I/Q Band Select 1.6 GSPS Down BPF Conversion 180-200 MHz 180-200 MHz Band Select ADC I/F I/Q LPF 1.6 GSPS Down # of Taps? LPF ... Conversion # of filts 800 MHz

Example Flow Diagram ADC I/F I/Q LPF 1.6 GSPS Down # of Taps? LPF ... Conversion # of filts 800 MHz R R R

Digital Down Conversion • IF Sampling and faster GSPS ADCs enable fewer analog components and allow the received signal to be converted into the digital domain earlier in the receiver chain. • reduced noise and lower hardware complexity. • Puts an addition burden on the digital processor (in real time). • Digital Down Converters (DDC) are commonly used to mix the signal to baseband for subsequent processing.

Digital Down Conversion • Components • NCO to generate I and Q signals for quadrature mixer. • Quadrature mixer (multipliers). • y(n) = x(n)*cos(ωn) + j*x(n)*sin(ωn) • Since it is in the digital domain, don’t gain need to worry about I & Q phase and offsets. • What did we do to the data rate? • But what good is this? NCO DDS

Digital Down Conversion • D ecimate from 1.6 GSPS to 20 MSPS • Need to store complex values. • Data rate reduction • 1600/(2*20) reduced by a factor of 40. • 57.6 GB/sec to ~1 GB/sec. • Need a very good FIR to avoid aliasing of out-of-band noise (both analog and due to the digitizer) back into the pass-band prior to decimation.

Digital Down Conversion • With a LPF z -1 z -1 z -1 z -1 b 1 b 2 b 1 b 2 NCO DDS DC Offset b 1 b 2 b 1 b 2 can cause problems. z -1 z -1 z -1 z -1

Decimation and Interpolation • Decimation: Take every N th sample. R module decimate_3 ( input wire clock, input wire reset, Care must be taken to input wire enable, precondition the signal to input wire [15:0] in, avoid aliasing noise or other output reg [15:0] out, interference. output wire next); Usually some type of Nyquist counter ( band filtering is applied prior ... to decimation. .step(1), .limit(3), Wire “next” is exported from .wrap(next)); the module to be used as an enable for downstream operations. always@(posedge clock) begin if (reset) out <= 0; else if (enable & next) out <= in; end endmodule

Integrator Filter • Sample Domain Equation • 1 st order IIR filter with a0 = 1; y[n] = x[n] + y[n-1] • Z domain H(z) = 1/(1-z -1 ) • Pole at z = 1 (Critically Stable) z -1

Comb Filter • Sample Domain Equation • N th order FIR filter with b 0 =1 ,b N =-1. • All other terms are 0. y[n] = x[n] - y[n-N] • Z-domain H(z) = (1-z -N ) • N zeros equally spaced around the unit circle starting at z = 1. N=8 z -N

Cascade Integrator Comb (CIC) • The pole at z=1 and a pole at z=0 will be canceled. • All poles are now at zero, which is effectively a 7 th order FIR filter. • We have seen this pole zero diagram before? z -1 z -N

CIC N=8 As long as the integrator has • h = [1 1 1 1 1 1 1 1]; enough bits to accommodate the output it is ok if it • sum of 8 values overflows. z -1 z -N

CIC N=255 As long as the integrator has • sum of 256 values enough bits to accommodate the output it is ok if it overflows. z -N uses 255xWidth registers z -1 z -N

Cascade Integrator Comb (CIC) • Now we can decimate. • If R is an integer factor of N. R z -1 z -N

Cascade Integrator Comb (CIC) • Now we can decimate. • If R is an integer factor of N. • Running average of N values. R >>>3 z -1 z -N/R

Cascade Integrator Comb (CIC) • Now we can decimate. • If R is an integer factor of N. • Running average of N values. • Mean Removal R >>>k z -1 z -N/R N=2 k

muliple rate reduction filters • What does the net frequency response of multiple rate reduction filters? • Rather than using decimation, just use enables. • The result will hold the values for the decimation value • Consider a simple fir filter b = 2 3 2 • Cascade two and decimate in between by a factor of 2. FIR 2 FIR

muliple rate reduction filters b 1 = [2 3 2] b 2_eff = [2 2 3 3 2 2] b 1&2_eff = b 1 * b 2_eff b 1&2_eff = [4 10 16 19 19 16 10 4] b 3_eff = [2 2 2 2 3 3 3 3 2 2 2 2] b 1&2&3_eff = 19 effective terms but we only used 9. Effective number of taps for M-cascaded N-tap filters each followed by a decimation by R.

AD6676: IF Wideband Rec. Subsys. 2.0 to 3.2 GSPS ADC

AD6676

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.