CSSE132 Introduc0on to Computer Systems 20 : Memory - PowerPoint PPT Presentation

Adapted from Carnegie Mellon 15-213 CSSE132 Introduc0on to Computer Systems 20 : Memory hierarchy April 16, 2013 1 Today Storage technologies and trends

Adapted from Carnegie Mellon 15-213 CSSE132 ¡ Introduc0on ¡to ¡Computer ¡Systems ¡ 20 ¡: ¡Memory ¡hierarchy ¡ April ¡16, ¡2013 ¡ 1

Today ¡ ¢ Storage ¡technologies ¡and ¡trends ¡ ¢ Locality ¡of ¡reference ¡ ¢ Caching ¡in ¡the ¡memory ¡hierarchy ¡ 2

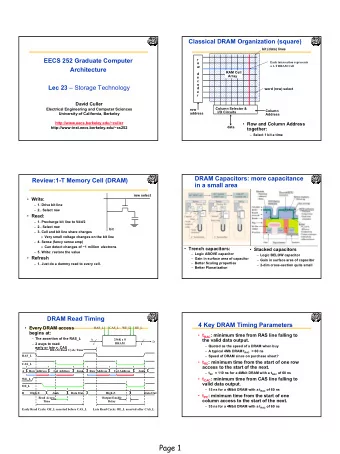

Random-‑Access ¡Memory ¡(RAM) ¡ ¢ Key ¡features ¡ § RAM ¡is ¡tradi:onally ¡packaged ¡as ¡a ¡chip. ¡ § Basic ¡storage ¡unit ¡is ¡normally ¡a ¡cell ¡(one ¡bit ¡per ¡cell). ¡ § Mul:ple ¡RAM ¡chips ¡form ¡a ¡memory. ¡ ¢ Sta0c ¡RAM ¡(SRAM) ¡ § Each ¡cell ¡stores ¡a ¡bit ¡with ¡a ¡four ¡or ¡six-‑transistor ¡circuit. ¡ § Retains ¡value ¡indefinitely, ¡as ¡long ¡as ¡it ¡is ¡kept ¡powered. ¡ § Rela:vely ¡insensi:ve ¡to ¡electrical ¡noise ¡(EMI), ¡radia:on, ¡etc. ¡ § Faster ¡and ¡more ¡expensive ¡than ¡DRAM. ¡ ¢ Dynamic ¡RAM ¡(DRAM) ¡ § Each ¡cell ¡stores ¡bit ¡with ¡a ¡capacitor. ¡One ¡transistor ¡is ¡used ¡for ¡access ¡ § Value ¡must ¡be ¡refreshed ¡every ¡10-‑100 ¡ms. ¡ § More ¡sensi:ve ¡to ¡disturbances ¡(EMI, ¡radia:on,…) ¡than ¡SRAM. ¡ § Slower ¡and ¡cheaper ¡than ¡SRAM. ¡ 3

SRAM ¡vs ¡DRAM ¡Summary ¡ Trans. Access Needs Needs per bit time refresh? EDC? Cost Applications SRAM 4 or 6 1X No Maybe 100x Cache memories DRAM 1 10X Yes Yes 1X Main memories, frame buffers 4

Conven0onal ¡DRAM ¡Organiza0on ¡ ¢ d ¡x ¡w ¡DRAM: ¡ § dw ¡total ¡bits ¡organized ¡as ¡d ¡supercells ¡of ¡size ¡w ¡bits ¡ ¢ Arranged ¡as ¡ ¡ 16 x 8 DRAM chip rows ¡x ¡columns ¡ cols 0 1 2 3 2 bits 0 / addr 1 rows Memory 2 supercell controller (2,1) (to/from CPU) 3 8 bits / data Internal row buffer 5

Reading ¡DRAM ¡Supercell ¡(2,1) ¡ Step ¡1(a): ¡Row ¡access ¡strobe ¡(RAS) ¡selects ¡row ¡2. ¡ Step ¡1(b): ¡Row ¡2 ¡copied ¡from ¡DRAM ¡array ¡to ¡row ¡buffer. ¡ ¡ 16 x 8 DRAM chip Cols 0 1 2 3 RAS = 2 2 0 / addr 1 Rows Memory 2 controller 3 8 / data Internal row buffer 6

Reading ¡DRAM ¡Supercell ¡(2,1) ¡ Step ¡2(a): ¡Column ¡access ¡strobe ¡(CAS) ¡selects ¡column ¡1. ¡ Step ¡2(b): ¡Supercell ¡(2,1) ¡copied ¡from ¡buffer ¡to ¡data ¡lines, ¡and ¡eventually ¡ back ¡to ¡the ¡CPU. ¡ ¡ 16 x 8 DRAM chip ¡ Cols 0 1 2 3 CAS = 1 2 0 / addr To CPU 1 Rows Memory 2 controller supercell 3 8 (2,1) / data supercell Internal row buffer (2,1) 7

Tradi0onal ¡Bus ¡Structure ¡Connec0ng ¡ ¡ CPU ¡and ¡Memory ¡ ¢ A ¡bus ¡is ¡a ¡collec0on ¡of ¡parallel ¡wires ¡that ¡carry ¡address, ¡ data, ¡and ¡control ¡signals. ¡ ¢ Buses ¡are ¡typically ¡shared ¡by ¡mul0ple ¡devices. ¡ CPU chip Register file ALU System bus Memory bus Main I/O Bus interface memory bridge 11

What’s ¡Inside ¡A ¡Disk ¡Drive? ¡ Spindle Arm Platters Actuator Electronics (including a processor SCSI and memory!) connector Image courtesy of Seagate Technology 18

Disk ¡Geometry ¡ ¢ Disks ¡consist ¡of ¡plaXers, ¡each ¡with ¡two ¡surfaces. ¡ ¢ Each ¡surface ¡consists ¡of ¡concentric ¡rings ¡called ¡tracks. ¡ ¢ Each ¡track ¡consists ¡of ¡sectors ¡separated ¡by ¡gaps. ¡ Tracks Surface Track k Gaps Spindle Sectors 19

Disk ¡Geometry ¡(Muliple-‑PlaXer ¡View) ¡ ¢ ¡Aligned ¡tracks ¡form ¡a ¡cylinder. ¡ Cylinder k Surface 0 Platter 0 Surface 1 Surface 2 Platter 1 Surface 3 Surface 4 Platter 2 Surface 5 Spindle 20

Disk ¡Opera0on ¡(Single-‑PlaXer ¡View) ¡ The disk surface The read/write head spins at a fixed is attached to the end rotational rate of the arm and flies over the disk surface on a thin cushion of air. spindle spindle spindle spindle spindle By moving radially, the arm can position the read/write head over any track. 23

Disk ¡Opera0on ¡(Mul0-‑PlaXer ¡View) ¡ Read/write heads move in unison from cylinder to cylinder Arm Spindle 24

Disk ¡Structure ¡-‑ ¡top ¡view ¡of ¡single ¡plaXer ¡ Surface organized into tracks Tracks divided into sectors 25

Disk ¡Access ¡ Head in position above a track 26

Disk ¡Access ¡ Rotation is counter-clockwise 27

Disk ¡Access ¡– ¡Read ¡ About to read blue sector 28

Disk ¡Access ¡– ¡Read ¡ After BLUE read After reading blue sector 29

Disk ¡Access ¡– ¡Read ¡ After BLUE read Red request scheduled next 30

Disk ¡Access ¡– ¡Seek ¡ After BLUE read Seek for RED Seek to red’s track 31

Disk ¡Access ¡– ¡Rota0onal ¡Latency ¡ After BLUE read Seek for RED Rotational latency Wait for red sector to rotate around 32

Disk ¡Access ¡– ¡Read ¡ After BLUE read Seek for RED Rotational latency After RED read Complete read of red 33

Disk ¡Access ¡– ¡Service ¡Time ¡Components ¡ After BLUE read Seek for RED Rotational latency After RED read Data ¡transfer ¡ Seek ¡ Rota0onal ¡ ¡ Data ¡transfer ¡ latency ¡ 34

Disk ¡Access ¡Time ¡ ¢ Average ¡0me ¡to ¡access ¡some ¡target ¡sector ¡approximated ¡by ¡: ¡ § Taccess ¡ ¡= ¡ ¡Tavg ¡seek ¡+ ¡ ¡Tavg ¡rota:on ¡+ ¡Tavg ¡transfer ¡ ¡ ¢ Seek ¡0me ¡(Tavg ¡seek) ¡ § Time ¡to ¡posi:on ¡heads ¡over ¡cylinder ¡containing ¡target ¡sector. ¡ § Typical ¡ ¡Tavg ¡seek ¡is ¡3—9 ¡ms ¡ ¢ Rota0onal ¡latency ¡(Tavg ¡rota0on) ¡ § Time ¡wai:ng ¡for ¡first ¡bit ¡of ¡target ¡sector ¡to ¡pass ¡under ¡r/w ¡head. ¡ § Tavg ¡rota:on ¡= ¡1/2 ¡x ¡1/RPMs ¡x ¡60 ¡sec/1 ¡min ¡ § Typical ¡Tavg ¡rota:on ¡= ¡7200 ¡RPMs ¡ ¢ Transfer ¡0me ¡(Tavg ¡transfer) ¡ ¡ § Time ¡to ¡read ¡the ¡bits ¡in ¡the ¡target ¡sector. ¡ § Tavg ¡transfer ¡= ¡1/RPM ¡x ¡1/(avg ¡# ¡sectors/track) ¡x ¡60 ¡secs/1 ¡min. ¡ 35

Disk ¡Access ¡Time ¡Example ¡ ¢ Given: ¡ § Rota:onal ¡rate ¡= ¡7,200 ¡RPM ¡ § Average ¡seek ¡:me ¡= ¡9 ¡ms. ¡ § Avg ¡# ¡sectors/track ¡= ¡400. ¡ ¢ Compute ¡average ¡access ¡0me ¡ 36

Disk ¡Access ¡Time ¡Example ¡ ¢ Given: ¡ § Rota:onal ¡rate ¡= ¡7,200 ¡RPM ¡ § Average ¡seek ¡:me ¡= ¡9 ¡ms. ¡ § Avg ¡# ¡sectors/track ¡= ¡400. ¡ ¢ Derived: ¡ § Tavg ¡rota:on ¡= ¡1/2 ¡x ¡(60 ¡secs/7200 ¡RPM) ¡x ¡1000 ¡ms/sec ¡= ¡4 ¡ms. ¡ § Tavg ¡transfer ¡= ¡60/7200 ¡RPM ¡x ¡1/400 ¡secs/track ¡x ¡1000 ¡ms/sec ¡= ¡0.02 ¡ms ¡ § Taccess ¡ ¡= ¡9 ¡ms ¡+ ¡4 ¡ms ¡+ ¡0.02 ¡ms ¡ ¢ Important ¡points: ¡ § Access ¡:me ¡dominated ¡by ¡seek ¡:me ¡and ¡rota:onal ¡latency. ¡ § First ¡bit ¡in ¡a ¡sector ¡is ¡the ¡most ¡expensive, ¡the ¡rest ¡are ¡free. ¡ § SRAM ¡access ¡:me ¡is ¡about ¡ ¡4 ¡ns/doubleword, ¡DRAM ¡about ¡ ¡60 ¡ns ¡ § Disk ¡is ¡about ¡40,000 ¡:mes ¡slower ¡than ¡SRAM, ¡ ¡ § 2,500 ¡:mes ¡slower ¡then ¡DRAM. ¡ 37

Logical ¡Disk ¡Blocks ¡ ¢ Modern ¡disks ¡present ¡a ¡simpler ¡abstract ¡view ¡of ¡the ¡ complex ¡sector ¡geometry: ¡ § The ¡set ¡of ¡available ¡sectors ¡is ¡modeled ¡as ¡a ¡sequence ¡of ¡b-‑sized ¡ logical ¡blocks ¡(0, ¡1, ¡2, ¡...) ¡ ¢ Mapping ¡between ¡logical ¡blocks ¡and ¡actual ¡(physical) ¡ sectors ¡ § Maintained ¡by ¡hardware/firmware ¡device ¡called ¡disk ¡controller. ¡ § Converts ¡requests ¡for ¡logical ¡blocks ¡into ¡(surface,track,sector) ¡ triples. ¡ ¢ Allows ¡controller ¡to ¡set ¡aside ¡spare ¡cylinders ¡for ¡each ¡ zone. ¡ § Accounts ¡for ¡the ¡difference ¡in ¡“formabed ¡capacity” ¡and ¡“maximum ¡ capacity”. ¡ ¡ 38

I/O ¡Bus ¡ CPU chip Register file ALU System bus Memory bus Main I/O Bus interface memory bridge I/O bus Expansion slots for other devices such as network adapters. USB Graphics Disk controller adapter controller Mouse Keyboard Monitor Disk 39

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.