CS137: Today Electronic Design Automation Topological Worst Case - PDF document

CS137: Today Electronic Design Automation Topological Worst Case not adequate (too conservative) Sensitization Conditions Day 6: October 10, 2005 Timed Calculus Static Timing Analysis Delay-justified paths and

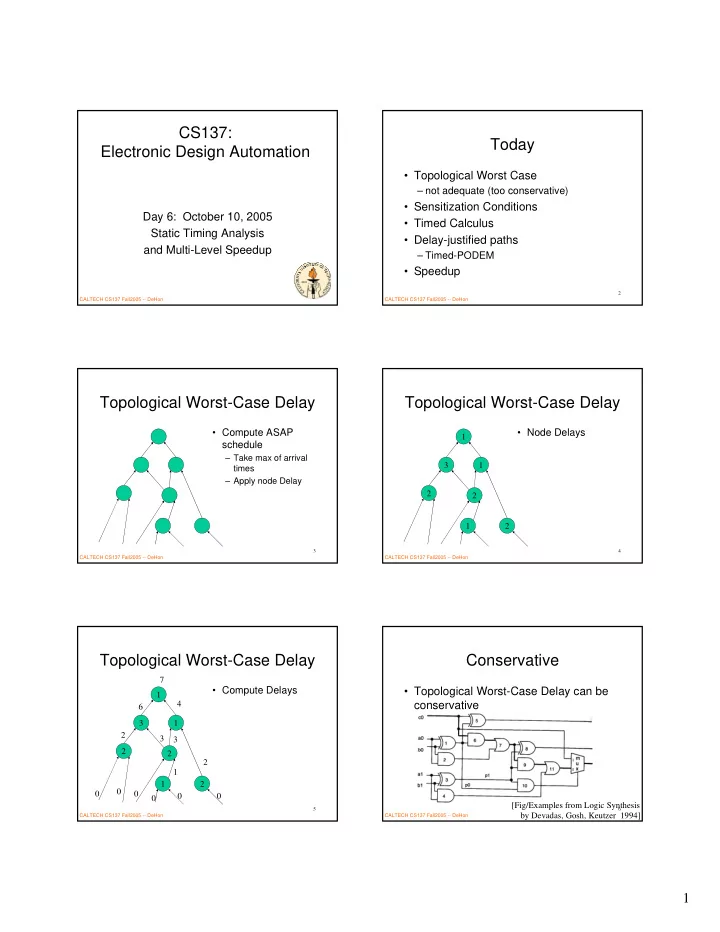

CS137: Today Electronic Design Automation • Topological Worst Case – not adequate (too conservative) • Sensitization Conditions Day 6: October 10, 2005 • Timed Calculus Static Timing Analysis • Delay-justified paths and Multi-Level Speedup – Timed-PODEM • Speedup 1 2 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon Topological Worst-Case Delay Topological Worst-Case Delay • Compute ASAP • Node Delays 1 schedule – Take max of arrival 3 1 times – Apply node Delay 2 2 1 2 3 4 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon Topological Worst-Case Delay Conservative 7 • Compute Delays • Topological Worst-Case Delay can be 1 4 conservative 6 3 1 2 3 3 2 2 2 1 1 2 0 0 0 0 0 0 [Fig/Examples from Logic Synthesis 5 6 by Devadas, Gosh, Keutzer 1994] CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon 1

Example Example • Is this path possible? • Assume each gate 1: •Out from mux 0 input •and10 = 0 •p0=0 or p1=0 •p1=0 1 → 6 → 7 not matter •p0=0 c0 not matter 6 delays in longest path 7 8 (5 if assume c0 latest arriving) •This path not feasible CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon False Paths What can we do? • Once consider logic for nodes • Need to assess what paths are real – There are logical constraints on data • Brute force values – for every pair of inputs • There are paths which cannot logically – compute delay in outputs from in1 → in2 occur input transition – Call them false paths – take worst case • Expensive: – 2 2n delay traces 9 10 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon Alternately Controlled Inputs • Look at single vector and determine • Controlled input to a gate: what controls delay of circuit – input whose value will determine gate output – I.e. look at values on path and determine path sensitized to change with input – e.g. • 0 on a AND gate • 1 on a OR gate 11 12 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon 2

Static Sensitization Statically Sensitized Path • A path is statically sensitized – if all the side (non-path) inputs are non- controlling – I.e. this path value flips with the input 13 14 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon Sufficiency …but not necessary • Static Sensitization is sufficient for a path to be a true path in circuit Paths of length 3 not statically sensitizable. But there is a true path of delay 3. 15 16 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon Static Co-sensitization Necessary • Each output with a controlled value • Static Co-sensitization is a necessary condition for a path to be true – has a controlling value as input on path – (and vice-versa for non-controlled) 17 18 May trace multiple edges CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon 3

…but not sufficient Combining • Combine these ideas into a timed- calculus for computing delays for an input vector Cosensitize path of length 6. Real delay is 5. 19 20 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon Computing Delays Rules • If gate output is at a controlling value, pick the minimum input and add gate delay • If gate output is at a non-controlling AND Timing value, pick the maximum input and add Calculus gate delay 21 22 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon Example (1) Example (2) 23 24 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon 4

Now... Better Approach • We know how to get the delay of a • Ask if can justify a delay greater than T single input condition • Search for satisfying vector • Could: – …or demonstration that none exists – find critical path • Binary search to find tightest delay – search for an input vector to sensitize – if fail, find next path – …until find longest true path • May be O(2 n ) 25 26 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon Delay Computation Search1 • Takes in list of nodes to satisfy • Modification of a testing routine • If all satisfied � done – used to justify an output value for a circuit • Backtrace to set next PI • PODEM • if inconsistent PI value – backtracking search to find a suitable input vector associated with some target output – try inverting this PI call Search2 – Simple a branching search with implication • else pruning – search to set next PI • Heuristic for smart variable ordering – if fail • try inverting and Search2 27 28 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon Search2 Backtrace • ;; same idea, but this one not flip bit • Follow back gates w/ unknown values • ;; because already tried inverted value – sometimes output dictate input must be • (AND needing 1 output; with one input already • If no conflict assigned 1) – search to set next PI – sometimes have to guess what to follow • otherwise • (OR with 1 output and no inputs set) • Uses heuristics to decide what to follow – pass back failure 29 30 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon 5

Example Example Try justify g=1 31 32 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon For Timed Justification Delay Calculation • Also want to compute delay – on incompletely specified values • Compute bounds on timing – upper bound, lower bound – Again, use our timed calculus • expanded to unknowns AND rules 33 34 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon Timed PODEM Example Justify 1(3) • Input: value to justify and delay T • Goal: find input vector which produces value and exceeds delay T • Algorithm – similar – implications check timing as well as logic 35 36 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon 6

Example Search • Less than 2 n – pruning due to implications – here saw a must be 0 • no need to search 1xx subtree Fail to justify 1(3) Justify 0(3) 37 38 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon Speed Up • Start with area optimized network Speed Up • Know target arrival times – Know delay from static analysis • Want to reduce delay of node (sketch flavor) 39 40 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon Basic Idea Speed Up • While (delay decreasing, timing not met) • Improve speed by: – Compute delay (slack) – Collapsing node(s) • Static timing analysis – Refactoring collapsed subgraph to reduce – Generate network close to critical path height – Weight nodes in network – Compute mincut of nodes on weighted network – Partial collapse and timing redecompose on cut nodes 41 42 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon 7

Weighted Cut Timing Decomposition • Want to minimize area expansion • Extract area saving kernels that do not include critical inputs to node • Want to maximize likely benefit • When decompose ( e.g. into nand2’s) – Prefer nodes with varying input times similarly balance with critical inputs – Prefer nodes with critical path on longer closest to output paths 43 44 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon Example Example 45 46 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon Example Admin New factor 47 48 CALTECH CS137 Fall2005 -- DeHon CALTECH CS137 Fall2005 -- DeHon 8

Big Ideas • Topological Worst-case delays are conservative – Once consider logical constraints – may have false paths • Necessary and sufficient conditions on true paths • Search for paths by delay – or demonstrate non existence • Search with implications • Iterative improvement 49 CALTECH CS137 Fall2005 -- DeHon 9

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.