Component-Based Synthesis by Solving Language Equations Tiziano - PowerPoint PPT Presentation

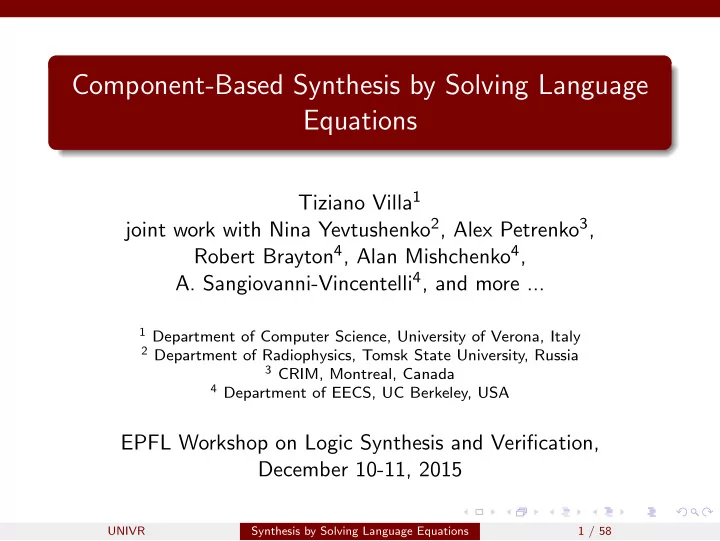

Component-Based Synthesis by Solving Language Equations Tiziano Villa 1 joint work with Nina Yevtushenko 2 , Alex Petrenko 3 , Robert Brayton 4 , Alan Mishchenko 4 , A. Sangiovanni-Vincentelli 4 , and more ... 1 Department of Computer Science,

Component-Based Synthesis by Solving Language Equations Tiziano Villa 1 joint work with Nina Yevtushenko 2 , Alex Petrenko 3 , Robert Brayton 4 , Alan Mishchenko 4 , A. Sangiovanni-Vincentelli 4 , and more ... 1 Department of Computer Science, University of Verona, Italy 2 Department of Radiophysics, Tomsk State University, Russia 3 CRIM, Montreal, Canada 4 Department of EECS, UC Berkeley, USA EPFL Workshop on Logic Synthesis and Verification, December 10-11, 2015 UNIVR Synthesis by Solving Language Equations 1 / 58

Outline Introduction 1 Some previous work 2 Composition operators 3 Synchronous operators Interleaving parallel operators Equations over languages 4 BALM–II 5 Examples 6 Example with finite automata Example with FSMs Conclusions 7 UNIVR Synthesis by Solving Language Equations 2 / 58

Introduction The problem of synthesizing an unknown component Problem: finding the unknown component Design a component that combined with a known part of a system (called the context or plant ) conforms to a given specification . UNIVR Synthesis by Solving Language Equations 3 / 58

Introduction The problem of synthesizing an unknown component Problem: finding the unknown component Design a component that combined with a known part of a system (called the context or plant ) conforms to a given specification . I 1 O 1 M A I 1 , I 2 O 1 , O 2 ≡ V U M C I 2 O 2 M X UNIVR Synthesis by Solving Language Equations 3 / 58

Introduction How to formalize the problem How to model the system and its components Associate languages to systems and components: traces of events over alphabets of internal and external signals. UNIVR Synthesis by Solving Language Equations 4 / 58

Introduction How to formalize the problem How to model the system and its components Associate languages to systems and components: traces of events over alphabets of internal and external signals. How to model composition Interleaving parallel composition (a.k.a.: parallel composition, synchronous parallel composition, asynchronous composition) Synchronous composition UNIVR Synthesis by Solving Language Equations 4 / 58

Introduction How to formalize the problem How to model the system and its components Associate languages to systems and components: traces of events over alphabets of internal and external signals. How to model composition Interleaving parallel composition (a.k.a.: parallel composition, synchronous parallel composition, asynchronous composition) Synchronous composition How to model conformance Language containment Simulation/Bisimulation relation UNIVR Synthesis by Solving Language Equations 4 / 58

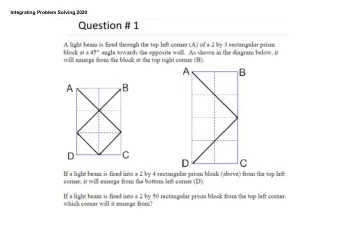

Introduction Composition topologies I 1 O 1 I 1 M A M A V U V U I 2 O 2 O 2 M B M B ( a ) ( b ) (a) General topology I 1 I 1 O 1 (b) 2-way cascade topology M A M A (c) 1-way cascade topology U V U (d) Rectification topology O 2 M B M B (e) Supervisory control topology ( c ) ( d ) (f) Variant of general topology I 1 O 1 M A M A I 3 V U = O 1 V U I 2 O 2 M B M B I 2 ( e ) ( f ) UNIVR Synthesis by Solving Language Equations 5 / 58

Introduction The unknown component problem Problem: finding the unknown component Design a component that combined with a known part of a system (called the context or plant ) conforms to a given specification . UNIVR Synthesis by Solving Language Equations 6 / 58

Introduction The unknown component problem Problem: finding the unknown component Design a component that combined with a known part of a system (called the context or plant ) conforms to a given specification . Solution: solving an equation over languages Reduce the problem to solving abstract equations over languages under synchronous and interleaving parallel composition. UNIVR Synthesis by Solving Language Equations 6 / 58

Some previous work Introduction 1 Some previous work 2 Composition operators 3 Synchronous operators Interleaving parallel operators Equations over languages 4 BALM–II 5 Examples 6 Example with finite automata Example with FSMs Conclusions 7 UNIVR Synthesis by Solving Language Equations 7 / 58

Some previous work Sequential synthesis Synthesis and resynthesis of a hardware component Kim-Newborn Yevtushenko et al. H.-Y. Wang-Brayton Watanabe-Brayton UNIVR Synthesis by Solving Language Equations 8 / 58

Some previous work Sequential synthesis Synthesis and resynthesis of a hardware component Kim-Newborn Yevtushenko et al. H.-Y. Wang-Brayton Watanabe-Brayton WS1S B¨ uchi Thatcher-Wright A. Aziz-Brayton et al. UNIVR Synthesis by Solving Language Equations 8 / 58

Some previous work Synthesis of discrete controllers Supervisory control Wonham-Ramadge Overkamp Kumar et al. UNIVR Synthesis by Solving Language Equations 9 / 58

Some previous work Synthesis of discrete controllers Supervisory control Wonham-Ramadge Overkamp Kumar et al. Model matching of finite state machines Khatri-Brayton-Sangiovanni Vincentelli et al. Di Benedetto-Sangiovanni Vincentelli et al. Lafortune et al. UNIVR Synthesis by Solving Language Equations 9 / 58

Some previous work Synthesis of automata and process algebras Submodule specification for communication protocols Bochmann et al. Petrenko-Yevtushenko Haghverdi-Ural Drissi UNIVR Synthesis by Solving Language Equations 10 / 58

Some previous work Synthesis of automata and process algebras Submodule specification for communication protocols Bochmann et al. Petrenko-Yevtushenko Haghverdi-Ural Drissi Process algebra Qin-Lewis Negulescu UNIVR Synthesis by Solving Language Equations 10 / 58

Some previous work Series topology: input don’t care sequences 1/1 1/1 0/0 0/0 0/0 0/1 2 2 1 1 0/0 0/0 1/0 1/0 1/1 1/1 3 3 (a) (b) 1/1 0/0 0/1 22 11 0/0 −/− 1/1 33 3T 1/− (c) (a) Head FSM; (b) Tail FSM; (c) Flexibility at tail FSM Solved by Kim-Newborn UNIVR Synthesis by Solving Language Equations 11 / 58

Some previous work Series topology: output don’t care sequences 1/1 1/1 0/0 0/0 0/0 0/1 2 2 1 1 0/1 0/1 1/0 1/0 1/1 1/1 3 3 (a) (b) 1/1 0/0 −/0 2b 1a 0/1 1/0 −/1 3b (c) (a) Head FSM; (b) Tail FSM; (c) Flexibility at head FSM Solved by Yevtushenko UNIVR Synthesis by Solving Language Equations 12 / 58

Some previous work WS1S and regular languages Weak Second-Order Logic of 1 Successor (WS1S) is a logic with the same expressive power as regular languages. It is possible to represent in WS1S any regular language L by encoding with a formula in WS1S the finite automaton A that recognizes the regular language L . Theorem (Thatcher-Wright, 1968) L ⊆ ( { 0 , 1 } k ) ⋆ is regular iff there exists a WS1S formula φ with X 1 , . . . , X k as free variables and L ( φ ) = L . The WS1S formalism allows to write down formulas that express the permissible behaviours at a node of a network of FSMs. UNIVR Synthesis by Solving Language Equations 13 / 58

Some previous work Synthesis with WS1S 1-Way Cascade (a) - case (c) ∗ ( I 1 , U ) = ( ∀ O 2 )[ φ M B ( U , O 2 ) → φ M C ( I 1 , O 2 )] . φ M A The machine M ∗ A is the one produced by the construction of Kim and Newborn. 1-Way Cascade (b) - case (c) ∗ ( U , O 2 ) = ( ∀ I 1 )[ φ M A ( I 1 , U ) → φ M C ( I 1 , O 2 )] . φ M B Supervisory Control - case (e) ∗ ( I 2 , O 1 , V ) = φ M A ( V , O 1 ) → φ M C ( I 2 , O 1 ) . φ M B 2-Way Cascade (a) - case (b) ∗ ( I 1 , V , U ) = ( ∀ O 2 )[ φ M B ( U , V , O 2 ) → φ M C ( I 1 , O 2 )] . φ M A 2-Way Cascade (b) - case (b) ∗ ( U , V , O 2 ) = ( ∀ I 1 )[ φ M A ( I 1 , V , U ) → φ M C ( I 1 , O 2 )] . φ M B Rectification (a) - case (d) ∗ ( U , V ) = ( ∀ I 1 , O 1 )[ φ M A ( I 1 , V , U , O 1 ) → φ M C ( I 1 , O 1 )] . φ M B Rectification (b) - case (d) ∗ ( I 1 , V , U , O 1 ) = φ M B ( U , V ) → φ M C ( I 1 , O 1 ) . φ M A UNIVR Synthesis by Solving Language Equations 14 / 58

Composition operators Introduction 1 Some previous work 2 Composition operators 3 Synchronous operators Interleaving parallel operators Equations over languages 4 BALM–II 5 Examples 6 Example with finite automata Example with FSMs Conclusions 7 UNIVR Synthesis by Solving Language Equations 15 / 58

Composition operators Synchronous and interleaving parallel composition Synchronous composition Synchronous composition ( • ) corresponds to instantaneous communication of systems. UNIVR Synthesis by Solving Language Equations 16 / 58

Composition operators Synchronous and interleaving parallel composition Synchronous composition Synchronous composition ( • ) corresponds to instantaneous communication of systems. Interleaving parallel composition Interleaving parallel composition ( ⋄ ) corresponds to asynchronous communication allowing arbitrary delay between communication events. A slow environment is assumed, i.e., no external input is applied to the composition until it produces an external output to the previous external input. UNIVR Synthesis by Solving Language Equations 16 / 58

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.