Chapter 4 Basic Concepts in VHDL 1 benyamin@mehr.sharif.edu - PowerPoint PPT Presentation

Chapter 4 Basic Concepts in VHDL 1 benyamin@mehr.sharif.edu Characterizing Hardware Languages Timing a x a:=x; a<=x AFTER 10 ns; b Concurrency Adder R.F Ctrl 2 benyamin@mehr.sharif.edu Concurrency in VHDL VHDL

Chapter 4 Basic Concepts in VHDL 1 benyamin@mehr.sharif.edu

Characterizing Hardware Languages • Timing a x a:=x; a<=x AFTER 10 ns; b • Concurrency Adder R.F Ctrl 2 benyamin@mehr.sharif.edu

Concurrency in VHDL • VHDL concurrent body ARCHITECTURE concurrent OF x IS … BEGIN signal assignment component instantiation assertion statement process statement END; 3 benyamin@mehr.sharif.edu

Concurrency in VHDL • VHDL sequential body ARCHITECTURE concurrent OF x IS … BEGIN process begin if statement Concurrent Statement while statement variable assignment end process; END; 4 benyamin@mehr.sharif.edu

Concurrency and Timing Example a (1->0) x g 2 b=1 g1 z Reacting g g2 Reacting 4 w g3 Reacting g 1 g g4 Reacting Reacting 3 y c=1 0 12 24 36 Delay of each gate=12 ns 5 benyamin@mehr.sharif.edu

Concurrency and Timing Example a (1->0) x a g b 2 b=1 c z w g 4 x w y g 1 g z 3 y c=1 0 12 24 36 Delay of each gate=12 ns 6 benyamin@mehr.sharif.edu

Signal Declaration •Signals must be declared in declaration area of architecture body SIGNAL ID{,ID} : type := init_val ; SIGNAL a : BIT :=‘1’; SIGNAL x,y,z : std_logic :=‘U’; 7 benyamin@mehr.sharif.edu

Signal Assignment • Target1<=waveform AFTER 5 ns ; Transport Delay AFTER Clause • Target1<=TRANSPORT waveform AFTER 5 ns ; • Target1<=REJECT 3 ns INERTIAL wvfrm AFTER 4 ns ; Inertial Delay 8 benyamin@mehr.sharif.edu

Transport Delay 3 A A C B = 1 2 3 C Delay = 2 C<= TRANSPORT A AND B AFTER 2 ns; 9 benyamin@mehr.sharif.edu

Inertial Delay R C 10 benyamin@mehr.sharif.edu

Input Inertial Delay 3 A A C dI=4 C B = 1 2 3 dI=2 C C<= REJECT 4 ns INERTIAL A AND B AFTER 2 ns; C<= REJECT 2 ns INERTIAL A AND B AFTER 2 ns; 11 benyamin@mehr.sharif.edu

Output Inertial Delay A A Delay=3 C C B B 2 A A 2 B B 2 1 3 3 2 C C 3 12 benyamin@mehr.sharif.edu

Concurrent Assignments ENTITY example IS Signal PORT(a,b,c:IN BIT; z:OUT BIT); Declaration END; ARCHITECTURE concurrent OF example IS Signal w,x,y:BIT:=‘0’; a x BEGIN w<=NOT a AFTER 12 ns; b z z x<=a AND b AFTER 12 ns; y<=c AND w AFTER 12 ns; w z<=x OR y AFTER 12 ns; y c END; 13 benyamin@mehr.sharif.edu

Signal Driver …. t3 t2 t1 now Signal v0 Driving value …. v3 v2 v1 14 benyamin@mehr.sharif.edu

Multiple Signal Assignment Resolution …. t3 t2 t1 Function now v0 Driving …. v3 v2 v1 value1 a Signal …. t’3 t’2 t’1 Value now v’0 Driving …. v’3 v’2 v’1 value2 a<= waveform1; a<=waveform2; 15 benyamin@mehr.sharif.edu

Events and Transactions • Event: when a waveform causes the value of the target signal to change, an event is said to have occurred on the target signal. • Transaction: when a value is scheduled to be assigned to a target signal after a given time, a transaction is said to have been placed on the driver of the target signal. • Transaction may cause an event or not. 16 benyamin@mehr.sharif.edu

Transaction and Event in Signal Driver Event …. t3 t2 t1 now Signal v0 Driving value …. v3 v2 v1 Transaction 17 benyamin@mehr.sharif.edu

Event and Transaction Example ARCHITECTURE demo OF example IS SIGNAL a,b,c:BIT:=‘0’; BEGIN a<=‘1’ AFTER 15 ns; b<= NOT a AFTER 5 ns; c<= a AFTER 10 ns; END; a b c 0 5 10 15 20 25 30 18 benyamin@mehr.sharif.edu

Transaction Placement and Expiration (1,15) a (1,5) b (1,5) b (0,10) c (0,10) c 0 5 10 15 20 25 ns a c c b b 0 5 10 15 20 25 ns 19 benyamin@mehr.sharif.edu

Delta Delay • VHDL defines a simulation cycle as an internal delay, referred to as δ delay. • It is used to model hardware concurrency. • Each concurrent statement in VHDL, consumes 1 δ delay to execute. 20 benyamin@mehr.sharif.edu

δ Delay Demonstration ARCHITECTURE delta OF timing IS SIGNAL a,b,c:BIT:=‘0’; a BEGIN a<=‘1’; b b<= NOT a; c<= NOT b; END; c 0 1 2 3 4 5 δ 21 benyamin@mehr.sharif.edu

δ Delay Demonstration ARCHITECTURE delta OF timing IS a SIGNAL a,b,c:BIT:=‘0’; BEGIN b a<=‘1’ AFTER 5 NS; b<= NOT a; c<= NOT b AFTER 5 NS; END; c 0 1 δ 5 1 δ 10 c(1,5) is removed by c(0,5) 22 benyamin@mehr.sharif.edu

δ Delay x Entity deltadelay is y End ; Architecture one of deltadelay is Signal y:bit:=‘1’; Signal x:bit:=‘0’; Begin x x<=y; y<=not x; y End ; 0 1 2 3 4 5 23 benyamin@mehr.sharif.edu

Sequential Placement of Transactions begin Architecture a of b is Process begin Begin x<=v1,v2 after t1; x<=v1 after t1; z<=x after t2; x<=v2 after t2; End; End process; End; Concurrent Body Sequential Body 24 benyamin@mehr.sharif.edu

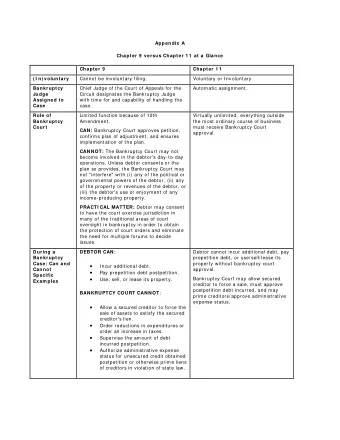

Sequential Placement of Transactions Transport Inertial t new <=t exist Overwrite Overwrite Append V new = V exist V new /= V exist Append t new> t exist Append t new -t exist >reject V new /= V exist Overwrite t new -t exist <=reject 25 benyamin@mehr.sharif.edu

Sequential Placement - Discarding ARCHITECTURE seq OF delay IS SIGNAL x:std_logic := ‘Z’; 0 BEGIN PROCESS Z BEGIN x<=‘1’ AFTER 5 ns; 0 1 2 3 4 5 6 7 8 ns x<=TRANSPORT ‘0’ AFTER 3 ns; WAIT; END PROCESS; END; 26 benyamin@mehr.sharif.edu

Sequential Placement - Appending ARCHITECTURE seq OF delay IS SIGNAL x:std_logic := ‘Z’; BEGIN PROCESS Z BEGIN x<=‘1’ AFTER 5 ns; 0 1 2 3 4 5 6 7 8 9 10ns x<=TRANSPORT ‘0’ AFTER 8 ns; WAIT; END PROCESS; END; 27 benyamin@mehr.sharif.edu

Sequential Placement - Appending ARCHITECTURE seq OF delay IS SIGNAL x:std_logic := ‘Z’; BEGIN PROCESS Z BEGIN x<=‘1’ AFTER 5 ns; 0 1 2 3 4 5 6 7 8 9 10ns x<=REJECT 2 ns ‘0’ AFTER 8 ns; WAIT; END PROCESS; END; 28 benyamin@mehr.sharif.edu

Sequential Placement - Discarding ARCHITECTURE seq OF delay IS SIGNAL x:std_logic := ‘Z’; BEGIN PROCESS Z BEGIN x<=‘1’ AFTER 5 ns; 0 1 2 3 4 5 6 7 8 9 10ns x<=REJECT 4 ns ‘0’ AFTER 8 ns; WAIT; END PROCESS; END; 29 benyamin@mehr.sharif.edu

Pulse Rejection a<=‘0’ , ‘1’ after 5 ns ,’0’ after 20 ns,’1’ after 40 ns,’0’ after 45 ns; 15 5 x<= a after 10 ns; a x x<= REJECT 10 ns INERTIAL a after 10 ns; 30 benyamin@mehr.sharif.edu

Chapter 5 Structural Specification of Hardware 31 benyamin@mehr.sharif.edu

Structural Level • Components of the system are listed and interconnections between them are specified (netlist) 32 benyamin@mehr.sharif.edu

VHDL Language 1. Selection of component from a certain package or library 2. Binding or association the usage of a component to an available library 3. Wiring mechanism 4. Construction for specification of repetitive hardware 33 benyamin@mehr.sharif.edu

Parts Library - Inverter Model Entity inv IS PORT(i1:IN BIT;o1:OUT BIT); Inverter Symbol END inv; ARCHITECTURE single_delay OF inv IS Inv i1 o1 BEGIN o1<=NOT i1 AFTER 4 NS; Inverter aspect notation END; 34 benyamin@mehr.sharif.edu

Elements of Aspect Notation entity_name Interface Aspect Input output Bidirectional Buffer port port port port 35 benyamin@mehr.sharif.edu

Details of The Entity ENTITY inv IS PORT ( i1: IN BIT Interface signal declaration port Entity ; clause declaration o1:OUT BIT Interface signal declaration ) ; END inv; 36 benyamin@mehr.sharif.edu

Parts Library - Nand2 Gate Model Entity nand2 IS PORT(i1,i2:IN BIT; o1:OUT BIT); End; ARCHITECTURE single_delay OF nand2 IS Nand2 BEGIN o1<=i1 NAND i2 AFTER 5 ns; END; 37 benyamin@mehr.sharif.edu

Details of The Entity ENTITY nand2 IS PORT ( i1 , i2 Identifier list : mode IN port Entity type BIT clause declaration ; o1:OUT BIT Interface signal declaration ) ; END; 38 benyamin@mehr.sharif.edu

Parts Library - Nand3 Gate Model Entity nand3 IS PORT(i1,i2,i3:IN BIT; o1:OUT BIT); End; ARCHITECTURE single_delay OF nand3 IS Nand2 BEGIN o1<=NOT(i1 AND i2 AND i3) AFTER 6 ns; END; 39 benyamin@mehr.sharif.edu

Wiring of Primitives – Comparator Design A A>B a_gt_b= a.gt+b’gt+a.b’ B a_eq_b=a.b.eq+a’.b’.eq A=B > a_lt_b=a’.lt+b.lt+a’.b = A<B < 40 benyamin@mehr.sharif.edu

Comparator Design – Karnaugh Table a b 00 01 11 10 a b 00 01 11 10 > = 0 0 0 0 1 0 0 0 0 0 1 1 0 1 1 1 1 0 1 0 a b 00 01 11 10 < 0 0 1 0 0 1 1 1 1 0 41 benyamin@mehr.sharif.edu

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.