Chapter 3-7 2, find the corresponding domino gate using a PDN net - PowerPoint PPT Presentation

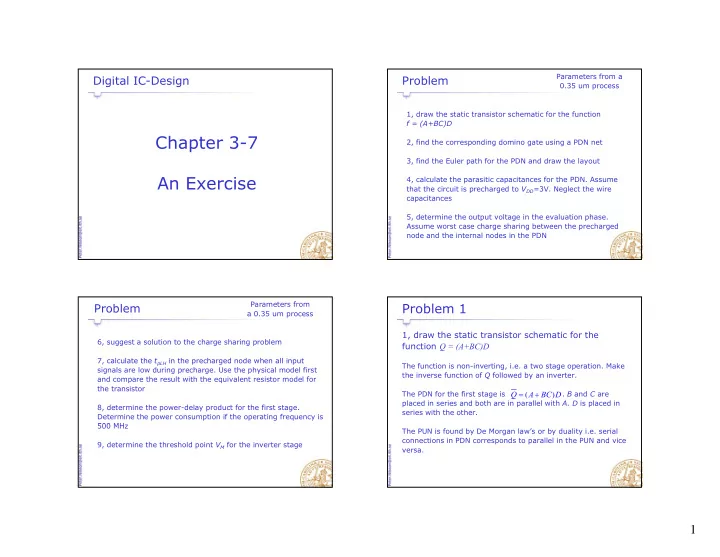

Parameters from a Digital IC-Design Problem 0.35 um process 1, draw the static transistor schematic for the function f = (A+BC)D Chapter 3-7 2, find the corresponding domino gate using a PDN net 3, find the Euler path for the PDN and draw

Parameters from a Digital IC-Design Problem 0.35 um process 1, draw the static transistor schematic for the function f = (A+BC)D Chapter 3-7 2, find the corresponding domino gate using a PDN net 3, find the Euler path for the PDN and draw the layout An Exercise 4, calculate the parasitic capacitances for the PDN. Assume that the circuit is precharged to V DD =3V. Neglect the wire capacitances it 5, determine the output voltage in the evaluation phase. Assume worst case charge sharing between the precharged node and the internal nodes in the PDN Parameters from Problem 1 Problem a 0.35 um process 1, draw the static transistor schematic for the 6, suggest a solution to the charge sharing problem function Q = (A+BC)D 7 calculate the t 7, calculate the t pLH in the precharged node when all input in the precharged node when all input The function is non-inverting, i.e. a two stage operation. Make signals are low during precharge. Use the physical model first the inverse function of Q followed by an inverter. and compare the result with the equivalent resistor model for the transistor = + The PDN for the first stage is . B and C are Q A BC D ( ) placed in series and both are in parallel with A . D is placed in 8, determine the power-delay product for the first stage. series with the other. Determine the power consumption if the operating frequency is 500 MH 500 MHz The PUN is found by De Morgan law’s or by duality i.e. serial connections in PDN corresponds to parallel in the PUN and vice 9, determine the threshold point V M for the inverter stage versa. 1

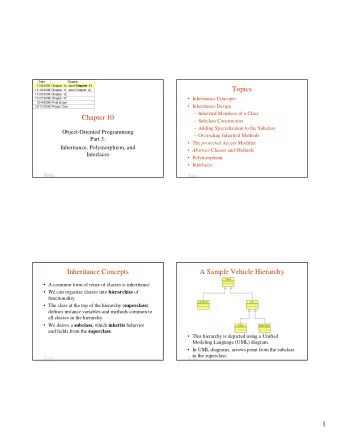

Static Gate Domino Logic 1, draw the static transistor schematic for the function Q = (A+BC)D 2, find the corresponding domino gate using a PDN net B B C C φ A D f (A+BC)D B PDN A C φ D Domino Logic Euler Path 2, find the corresponding domino gate using a PDN net 3, find the Euler path for the PDN and draw the layout V DD V DD φ φ V DD f (A+BC)D f (A+BC)D B C B B A D f (A+BC)D A A B A C C C D D D Static gate φ φ 2

Euler Path and Layout Parasitic Capacitances 3, find the Euler path for the PDN and draw the layout 4, calculate the parasitic capacitances in the PDN. Assume that the circuit is precharged to V DD = 3V. Neglect the wire capacitances. V DD Euler Path φ 3V f (A+BC)D V DD B V DD V A DD φ C 1 C f (A+BC)D C 1 B D f C 3 A φ 0V C 2 f C C 2 D D φ C 4 =C 3 Note: the path A B C GND φ goes through the D φ C 3 ground A B C GND 4, calculate the parasitic C 1 Capacitance Overlap Capacitance capacitances in the PDN. Gate Source Drain C 1 consists of: Overlap C in the A, B, p , , V DD L L W W and Φ p -transistor C GD = C o × W C 1 Diffusion C in n - and p - f C GS C GD C GS = C o × W drain areas C GC Channel & Overlap C in Channel & Overlap C in D φ φ A B C C 0 is a constant per unit length GND the inverter C 0 in fF/um 2 Wire C is neglected 3

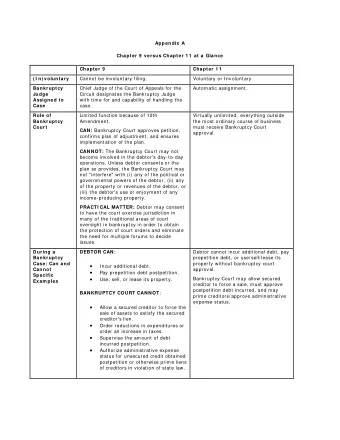

Parameters – 0.35um The Miller Effect Electrical Parameters Capacitances If C gd is modeled from V out to GND, k n ’ 175 mA/V 2 C ox 4.6 fF/mm 2 the value shall be doubled the value shall be doubled V Tn C 0 (C d C C 0 (C gd0 C gs0 ) ) 0.5 V 0.21 0 21 fF/mm fF/mm Tn L (0.35mm) 0.3 mm C j0n fF/mm 2 0.93 W (0.6mm) 0.55 mm C j0p C gd fF/mm 2 1.42 γ n V 1/2 0.58 C jsw0n Δ V Δ V 0.28 fF/mm λ n 0.05 1/V C jsw0p Δ Δ 0.38 fF/mm V V k p ’ -60 mA/V 2 2C gd 2C d V V Tp -0.6 0 6 V V Velocity Saturation L (0.35mm) 0.38 mm V DSATn 0.82 V W (0.6mm) 0.55 mm V DSATp -1.3 V C gd = 2 C 0 W γ p V 1/2 -0.5 λ p -0.15 1/V 4, calculate the parasitic Overlap Cap. C gd Junction Capacitance capacitances in the PDN. Drain/Source Diffusion GND -> V DD /2 or V DD -> V DD /2 transition is assumed (to 50% point) C Diff =C Bot +C SW C Diff C Bot +C SW Bottom Bottom V DD = × × × = C C W 2 3 ( ) C GD gd 0 e Don’t count the wall t fF a G = × μ = m towards the channel 6(0.21 1.0 ) μ C 1 m s d r f a w l e o n = 1.26 fF fF T T n n 1 26 a a h C W Side D φ A B C Wall GND L s 4

4, calculate the parasitic Junction Capacitance Determine K eq : Example capacitances in the PDN. High-to-low transition (–V DD to –V DD /2) = × + × C K AD C K PD C DBn eqn n j eqswn n jsw 0 0 NMOS, Bottom plate Determine K eq (see eq 5.14) = φ = = − = − m V V C DBp 0.5; 0.9 V; 3 V; 1.5 V High Low 0 ( ) V DD − − − φ m φ − m − φ − m V 1 V 1 ( ) ( ) ( ) High Low = 0 0 0 K − φ m φ − − m − φ − − m V V 1 1 ( ) ( ) eq − − V V m High Low = 0 0 0 = ( )(1 ) K High Low eq − − V V V V m m ( ( )(1 )(1 ) ) High Hi h Low L f f ( ) − − − + − + Transition to 50% point 0.5 1 0.5 1 0.5 0.9 (0.9 3) (0.9 1.5) = = Note: Reverse biased voltages − + − ( 3 1.5)(1 0.5) (diodes) i.e. negative voltages D φ = A B C 0.54 GND C DBn 4, calculate the parasitic Determine K eq Junction Capacitance capacitances in the PDN. NMOS NMOS, 0.35 um technology, V DD =3 V If high-to-low transition: High-to-low g Bottom plate p K eqn =0.54 eqn High-to-low Sidewall K eqswn =0.58 = × + × = C K AD C K PD C Low-to-high Bottom plate K eqn =0.76 DBn eqn n j n eqswn n jsw n 0 0 = × × × + × × × = V DD 0.54 1 1 0.93 0.58 2 1 0.28 Low-to-high Sidewall K eqswn =0.78 C j fF 0.83 PMOS, 0.35 um technology, V DD =3 V C 1 1 f f Area 1um 2 High-to-low Bottom plate K eqp =0.77 Sidewall 2um High-to-low Sidewall K eqswp =0.84 Low-to-high Bottom plate K eqp =0.55 D φ Low-to-high Sidewall K eqswp =0.67 A B C GND 5

4, calculate the parasitic Junction Capacitance Channel Capacitance Gate capacitances in the PDN. Source Drain PMOS If high-to-low transition: L W C GC can be: C GC can be: A Area 1um 2 1 2 Sidewall 3um = × + × = C K AD C K PD C C GCB = Gate cap. to bulk DBp eqp n j p eqswp p jsw p 0 0 C GS C GD = × × × + × × × = V DD C GCD = Gate cap. to drain 0.77 1 1 1.42 0.84 3 1 0.38 C GC C j fF 2.01 C GCS = Gate cap. to source C 1 1 f f Dependent on oxide capacitance and area C OX (F/ μ m 2 ) LW ( μ m 2 ) D φ A B C GND Channel Capacitance Gate-Channel Capacitance (Table 3-4) To Bulk To Source To Drain Total Gate Cap. Cut off Linear C GCB C GCS C GCD C G Cutoff C OX W L C OX W L + 2 C 0 W 0 0 n + n + n + n + Resistive (1/2) C OX W L (1/2) C OX W L C OX W L + 2 C 0 W 0 Saturation (2/3) C OX W L (2/3) C OX W L + 2 C 0 W 0 0 C Saturation Cut off: No channel ⇒ C GC = C GCB GCB Resistive: Channel ⇒ Divide C GC in two parts C C GCS GCD n + n + Saturation: ≈ 2/3 of Channel to source 6

4, calculate the parasitic 4, calculate the parasitic Total Gate Cap. C Gn Total Gate Cap. C Gp capacitances in the PDN. capacitances in the PDN. 2 = + + = × + × × = C C C C C W C W L 2 Gn GS GD GC OX = + + = × + × × = 0 C C C C C W C W L 3 2 C Gp Gp GS GD GC OX 0 2 2 = × × + × × = = × × + × × = 2 0.21 1 4.6 1.0 0.38 2 0.21 1 4.6 1.0 0.3 C Gn V DD V DD 3 = 2.17 fF = 1.34 fF 1.0 um C 1 C 1 f f High-to-low High-to-low transition => transition => 1.0 um C Gn is in Saturation C Gp is in Cutoff D φ D φ and is closing and is opening A B C A B C GND GND 4, calculate the parasitic 4, calculate the parasitic C 1 Capacitance C 2 capacitances in the PDN. capacitances in the PDN. = + = C C C Total Cap in node C 1 GD GS DBn 2 / V DD = × × × + C W = + + + + + + + + + + = C C C C C C C C C C C C 2 3 0 0 G GD DBn DBp Gn G Gp G 1 1 + × + K AD C C 1 = + + + + = 1.26 0.83 2.01 1.34 2.17 eqn n j n 0 f V DD + × = K PD C = C 2 fF 7.61 eqswn n jsw n 0 C 1 = × × × + 2 3 0.21 1 f D φ D φ + × + × × × × × × × + + A A B B C C 2 0 54 1 1 0 93 2 0.54 1 1 0.93 G GND + × × × 0.58 5 1 0.28 D φ = 3.08 fF A B C GND 7

4, calculate the parasitic C 3 Charge Sharing capacitances in the PDN. 5, calculate the output voltage in the evaluation phase. Assume worst case = + = C C C charge sharing between the precharged node and the internal nodes in the GD GS DBn 3 / V DD PDN = × × × × × × + + C C W W 2 2 2 2 V V DD 0 0 Q = tot V V DD + × + φ C 1 K AD C out C tot eqn n j n 0 f V A Q = C V + C V f NAND C 2 + × = K PD C tot L DD A A C A C L = + C C C eqswn n jsw n A->1 C L 0 tot L A = × × × + 2 2 0.21 1 B=0 C A D φ D φ + C V C V = A A B B C C V V L DD A A + × × + φ GND G 0.54 0.7 0.93 out + C C V out L A + × × C 3 0.58 1.4 0.28 << V V Area 0.7um 2 C A C L A DD = 1.42 fF C Sidewall 1.4um = V L V out + DD C C L A Charge Sharing Charge Sharing Worst case when D-transistor off and when the C2 and C3 nodes are uncharged 5, calculate the output voltage in the evaluation phase. Assume worst case 6, suggest a solution to the charge sharing problem charge sharing between the precharged node and the internal nodes in the PDN = C C fF fF 7 61 7.61 3V V DD V DD 1 V DD φ φ φ = Weak C fF 3.08 φ C 1 2 f (A+BC)D f (A+BC)D = f (A+BC)D C fF B B 1.42 3 A A B C 3 C C A C 0V C 2 V = V = C 1 C + + + + DD 1 C C C C C C D D 1 2 3 D φ φ 7.61 φ = × = 3 1.89 V + + 7.61 3.08 1.42 63 % of V DD 8

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.