Binary Addition Goals DEF: A binary adder with input length n is a - PowerPoint PPT Presentation

Binary Addition Goals DEF: A binary adder with input length n is a combinational circuit specified as follows. Binary addition - definition Input: A [ n 1 : 0] , B [ n 1 : 0] { 0 , 1 } n , and C [0] { 0 , 1 } . Chapter 6:

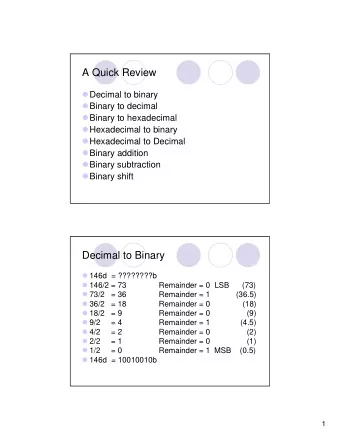

Binary Addition Goals DEF: A binary adder with input length n is a combinational circuit specified as follows. Binary addition - definition Input: A [ n − 1 : 0] , B [ n − 1 : 0] ∈ { 0 , 1 } n , and C [0] ∈ { 0 , 1 } . Chapter 6: Addition Ripple Carry Adder - definition, correctness, cost, delay Output: S [ n − 1 : 0] ∈ { 0 , 1 } n and C [ n ] ∈ { 0 , 1 } . Carry bits - definition, properties Computer Structure - Spring 2004 Functionality: (*) Conditional Sum Adder - definition, correctness, � Dr. Guy Even c cost, delay S � + 2 n · C [ n ] = � � � � A � + � � B � + C [0] (*) Compound Adder - definition, correctness, cost, Tel-Aviv Univ. A, � � delay B - binary representations of the addends. C [0] - the carry-in bit. � S - binary representation of the sum. C [ n ] - the carry-out bit. Question: is the functionality of ADDER ( n ) is well defined? – p.1 – p.2 – p.3 Ripple Carry Adder - RCA ( n ) Lower bounds Full Adder Prove that for every ADDER ( n ) : A Full-Adder is a combinational circuit with 3 inputs B [ n − 1] A [ n − 1] B [ n − 2] A [ n − 2] B [1] A [1] B [0] A [0] x, y, z ∈ { 0 , 1 } and 2 outputs c, s ∈ { 0 , 1 } that satisfies: C [0] c ( ADDER ( n )) = Ω( n ) fa n − 1 fa n − 2 c fa 1 c fa 0 c s c s s s 2 c + s = x + y + z. d ( ADDER ( n )) = Ω(log n ) C [ n ] S [ n − 1] C [ n − 1] S [ n − 2] C [ n − 2] C [2] S [1] C [1] S [0] A Full Adder computes a binary representation of the sum of 3 bits. carry-out output of FA i is denoted by c [ i + 1] . s - called the sum output. weight of every signal is two to the power of its index. c - called the carry-out output. RCA ( n ) - algorithm that we use for adding numbers by hand. We denote a Full-Adder by FA . – p.4 – p.5 – p.6

Correctness proof Induction Step Correctness - cont. To facilitate the proof, we use an equivalent recursive The proof is by induction on n . The induction hypothesis, for n − 1 , is definition of RCA ( n ) . (1) � A [ n − 2 : 0] � + � B [ n − 2 : 0] � + C [0] = The induction basis, for n = 1 , follows directly from the defi- The recursive definition is as follows. 2 n − 1 · C [ n − 1] + � S [ n − 2 : 0] � . nition of a Full-Adder. Basis: an RCA (1) is simply a Full-Adder. Full-Adder definition Step: B [ n − 1] A [ n − 1] B [ n − 2 : 0] A [ n − 2 : 0] (2) A [ n − 1] + B [ n − 1] + C [ n − 1] = 2 · C [ n ] + S [ n − 1] . n-1 n-1 Multiply (2) by 2 n − 1 to obtain C [0] rca ( n − 1) fa n − 1 c s 2 n − 1 · A [ n − 1] + 2 n − 1 · B [ n − 1] + 2 n − 1 · C [ n − 1] = (3) n-1 2 n · C [ n ] + 2 n − 1 · S [ n − 1] . C [ n ] S [ n − 1] C [ n − 1] S [ n − 2 : 0] – p.7 – p.8 – p.9 Is RCA ( n ) good enough? Cost & Delay Analysis � A [ n − 2 : 0] � + � B [ n − 2 : 0] � + C [0] = (1) 2 n − 1 · C [ n − 1] + � S [ n − 2 : 0] � . Clock rate = 1 GHz = 10 9 Hz The cost of an RCA ( n ) satisfies: ⇒ clock period = 10 − 9 sec = 1 ns . c ( RCA ( n )) = n · c ( FA ) = Θ( n ) . 2 n − 1 · A [ n − 1] + 2 n − 1 · B [ n − 1] + 2 n − 1 · C [ n − 1] = (3) Delay of gate ≈ 100 ps = 0 . 1 ns . 2 n · C [ n ] + 2 n − 1 · S [ n − 1] . The delay of an RCA ( n ) satisfies d ( FA ) ≈ 2 · d ( gate ) ≈ 0 . 2 ns . ⇒ Within a clock period we can only add 5 -bit d ( RCA ( n )) = n · d ( FA ) = Θ( n ) . Note that 2 n − 1 · A [ n − 1] + � A [ n − 2 : 0] � = � A [ n − 1 : 0] � . numbers... (1) + (3) = ⇒ Question: How are > 100 bits added in one clock cycle? 2 n − 1 · C [ n − 1] + � A [ n − 1 : 0] � + � B [ n − 1 : 0] � + C [0] = 2 n · C [ n ] + 2 n − 1 · C [ n − 1] + � S [ n − 1 : 0] � . Cancel out 2 n − 1 · C [ n − 1] . QED. – p.10 – p.11 – p.12

Carry bits remark 1: redundant & non-redundant representations remark 1 - cont Functionality of an adder: DEF: The carry bits associated with an addition Functionality of an adder: � A [ n − 1 : 0] � + � B [ n − 1 : 0] � + C [0] = 2 n · C [ n ] + � S [ n − 1 : 0] � . � � A � + � � B � + C [0] are the signals C [ n : 0] in an RCA ( n ) . � A [ n − 1 : 0] � + � B [ n − 1 : 0] � + C [0] = 2 n · C [ n ] + � S [ n − 1 : 0] � . x = � A [ n − 1 : 0] � + � B [ n − 1 : 0] � + C [0] . B [ n − 1] A [ n − 1] B [ n − 2] A [ n − 2] B [1] A [1] B [0] A [0] Let x = � � A � + � � many possible combinations of � � A � , � � B � + C [0] . B � and C [0] . For C [0] example: 8 = 4 + 3 + 1 , and also 8 = 5 + 3 + 0 . fa n − 1 fa n − 2 c fa 1 c fa 0 x admits two representations (left-hand side, right-hand c s c s s s → redundant representation. side) C [ n ] S [ n − 1] C [ n − 1] S [ n − 2] C [ n − 2] C [2] S [1] C [1] S [0] in redundant representation: C [ n ] · S [ n − 1 : 0] - binary representation of x . Binary representation is non-redundant: X � = Y � = ⇒ value(X) � = value ( Y ) . Every value has a unique representation. ⇒ in redundant representation: comparison is � � X � = � � Y � ⇐ ⇒ X = Y . complicated. ADDER ( n ) - translates a redundant representation to a non-redundant binary representation. – p.13 – p.14 – p.15 remark 2: cones remark 3 remark 4: reductions sum-bits ← → carry-bits The correctness of RCA ( n ) implies that, for every 0 ≤ i ≤ n − 1 , The correctness proof of RCA ( n ) implies that, for every � A [ i : 0] � + � B [ i : 0] � + C [0] = 2 i +1 · C [ i + 1] + � S [ i : 0] � . 0 ≤ i ≤ n − 1 , S [ i ] = XOR ( A [ i ] , B [ i ] , C [ i ]) . � A [ i : 0] � + � B [ i : 0] � + C [0] = 2 i +1 · C [ i + 1] + � S [ i : 0] � . = ⇒ for every 0 ≤ i ≤ n − 1 , = ⇒ for every 0 ≤ i ≤ n − 1 , This equality means that: � S [ i : 0] � = mod ( � A [ i : 0] � + � B [ i : 0] � + C [0] , 2 i +1 ) . C [ i ] = XOR ( A [ i ] , B [ i ] , S [ i ]) . � � cone ( C [ i + 1]) , cone ( S [ i : 0]) ⊆ A [ i : 0] B [ i : 0] C [0] . ⇒ constant-time linear-cost reductions: = S [ n − 1 : 0] �− → C [ n − 1 : 0] Question: Prove that C [ n − 1 : 0] �− → S [ n − 1 : 0] � � cone ( S [ i ]) , cone ( C [ i + 1]) = A [ i : 0] B [ i : 0] C [0] . = ⇒ if Circuit computes C [ n − 1 : 0] with O ( n ) cost and (log n ) delay, then we know how to add with same asymptotic cost & delay. – p.16 – p.17 – p.18

Goals reminder: reduction sum-bits �− → carry-bits The correctness of RCA ( n ) implies that, for every 0 ≤ i ≤ n − 1 , Design an adder with O (log n ) delay and O ( n ) cost. Chapter 7: Fast Addition: parallel S [ i ] = XOR ( A [ i ] , B [ i ] , C [ i ]) . Learn some interesting methods along the way... prefix computation ⇒ constant-time linear-cost reduction: = Computer Structure - Spring 2004 S [ n − 1 : 0] �− → C [ n − 1 : 0] � Dr. Guy Even c = ⇒ if Circuit computes C [ n − 1 : 0] with O ( n ) cost and O (log n ) Tel-Aviv Univ. delay, then we know how to add asymptotically optimally. – p.40 – p.41 – p.42 Computing the carry bits - preliminary definition of σ [ n − 1 : − 1] example with σ [ n − 1 : − 1] � 2 · C [0] if i = − 1 Functionality of Full-Adder ( i th FA in RCA ( n ) ): DEF: for i = − 1 , 0 , . . . , n − 1 △ σ [ i ] = A [ i ] + B [ i ] if i ∈ [0 , n − 1] . � � 2 · C [0] if i = − 1 0 if A [ i ] + B [ i ] + C [ i ] ≤ 1 △ σ [ i ] = C [ i + 1] = Claim: for every − 1 ≤ i ≤ n − 1 , A [ i ] + B [ i ] if i ∈ [0 , n − 1] . 1 if A [ i ] + B [ i ] + C [ i ] ≥ 2 . ∃ j ≤ i : σ [ i : j ] = 1 i − j · 2 . C [ i + 1] = 1 ⇐ ⇒ Claim: Note that σ [ i ] ∈ { 0 , 1 , 2 } . ⇒ A [ i ] + B [ i ] = 0 = C [ i + 1] = 0 Claim: for every − 1 ≤ i ≤ n − 1 , Example: A [3 : 0] = 0110 , B [3 : 0] = 0011 , C [0] = 0 . A [ i ] + B [ i ] = 2 = ⇒ C [ i + 1] = 1 ∃ j ≤ i : σ [ i : j ] = 1 i − j · 2 . position 4 3 2 1 0 -1 ⇐ ⇒ C [ i + 1] = 1 A [ i ] + B [ i ] = 1 = ⇒ C [ i + 1] = C [ i ] A 0 1 1 0 B 0 0 1 1 = ⇒ S 1 0 0 1 if A [ i ] + B [ i ] ∈ { 0 , 2 } , then easy to compute C [ i + 1] . C 0 1 1 0 0 if A [ i ] + B [ i ] = 1 , then “ripple effect” of carry. σ 0 1 2 1 0 – p.43 – p.44 – p.45

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.