Belle II (KEK ) 1 - PowerPoint PPT Presentation

Belle II (KEK ) 1 @ 2017.10.2 1. Belle II 2. DAQ

Belle II 実験データ収集システム 山田悟 (KEK 素核研 ) 1 計測システム研究会 @ 函館アリーナ 2017.10.2

イントロダクション 1. Belle II データ読み出しシステム 2. DAQ システムのパフォーマンス 3. 外層検出器の宇宙線試験 4. Belle II 読み出し系のアップグレード計画 5. 2 計測システム研究会 @ 函館アリーナ 2017.10.2

Belle II 実験 ➢ Search for new physics beyond the Standard Model(SM) via high precision measurement with high statistics samples of B/D/tau decays. ➢ SuperKEKB accelerator ➢ Designed luminosity: 40times as large as KEKB ➢ 50 ab -1 in 10 years (cf. 1ab -1 @ Belle experiment) Belle II collaboration : ~ 750 collaborators from 24 countries x2 luminosity Increa rease e of beam current ent x20 x40 Smaller r bea eam size Improved 3 計測システム研究会 @ 函館アリーナ 2017.10.2

SuperKEKB のルミノシティ ( 予測 ) Phase I : (2016 Feb.-Jun.) ➢ Accelerator commissioning w/o final focusing magnets ➢ w/o the Belle II detector ➢ First turns of SuperKEKB ➢ Vacuum scrubbing Phase II : (2018Feb.-Jul) ➢ Accelerator commissioning and physics run ➢ with the Belle II detector We are here except for vertex sub- detectors Phase III : (around the end of 2018-) ➢ Physics run with the full Belle II detector 4 計測システム研究会 @ 函館アリーナ 2017.10.2

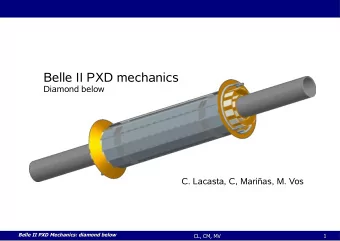

各 detector のインストール状況 ECL( 電磁カロリメー KLM(Klong muon 検出器 ) タ ) -> install 済み -> install 済み ARICH( エアロジェルリング 崩壊点検出器 イメージングチェレンコフカ (PXD,SVD) ウンタ ) 完全な install は 2018 年 実験ホールで組立作業 2017 年に install TOP(Time of Propagation) CDC( 中央飛跡検出器 ) カウンタ 実験ホールに仮設置 -> install 済み 10 月に Belle II 検出器に install 5 計測 システム 研究会 @ 函館 アリーナ 2017.10.2

測定器設置、コミッショニング等のスケジュール 現在 2018 2017 Jan. Feb. Mar. Apr. May Jun. Jul. Aug. Sep. Oct. Nov. Dec. Jan. Feb. Mar. 2016 測定器作製、組み立て作業 測定器 PXD 測定器設置 の一部 Phase II 用測 を組み 定器組み立 込む て作業 SVD 測定器組み立て作業 磁場中 測定器 CDC 設置 統合 宇宙線 Belle II 測定器ロールイン TOP 測定器 試験 設置 統合 / 独立 Phase II beam での 測定器設置 run 測定器組み立て、試験 宇宙線試 ARICH (2018 験など July まで ) 測定器 ECL 磁場中 設置 (barrel 部 ) 統合 宇宙線 KLM 測定器 試験 設置 6 計測システム研究会 @ 函館アリーナ 2017.10.2

イントロダクション 1. Belle II データ読み出しシステム 2. DAQ システムのパフォーマンス 3. 外層検出器の宇宙線試験 4. Belle II 読み出し系のアップグレード計画 5. 7 計測システム研究会 @ 函館アリーナ 2017.10.2

Belle II データ収集システム ( 今回は読み出しシステムの話を主に ) FEE との interface は各検出器共通 (PXD 以外 ) - HLT による rate reduction + Region of Interest による PXD の event size reduction - Level1 trigger ~ 30kHz (max. value for DAQ development ) Trigger and Timing distribution Data-reduction w/ ROI for PXD 内層 ( 崩壊点 ) Common readout-system Event-building 検出器 for sub-detectors And storage (Phase III から ) Event-building Software 外層検出器 Event- (phase II から ) reduction X210 X40 1GbE/10GbE x10 High Level Trigger+storage unit readout Readout switch 8 HLT: ( 20nodes x 16cores )/ unit 計測システム研究会 @ 函館アリーナ 2017.10.2 boards PCs

フロントエンド検出器とバックエンド DAQ との接続 ➢ 2 つのインターフェイスが必要 ➢ FEE とトリガータイミング分配システム : Backend DAQ Backend-DAQ ➢ FEE とバックエンド DAQ ( データフロー ) (DAQ gr.) ➢ データフローについては各検出器に共通の 通信用 firmware (Rocket I/O ベース ) を使用 → belle2link Trigger/clock FEE board COPPER FIFO FPGA on Front-end electronics board 9 計測システム研究会 @ 函館アリーナ 2017.10.2

フロントエンド電子回路からのデータ読み出し Belle2Link : (D. Sun et. all, hysics Procedia Volume 37, 2012, pp. 1933-1939 ) Unified high speed link which connects Front-End Electronics (FEE) and DAQ system for signal with data transmission based on Rocket I/O FEE side : Functions for I/F with FEE and Trigger Timing Distribution on FPGA DAQ side : High Speed Link Board(HSLB) as a data receiver COPPER : data readout board Front-end electronics Belle2Link FPGA COPPER I/F Line rate : 3.125Gbps GTP link HSLB FEE I/F A/D data data (Virtex5) data conver sion configutaion HSLB by register access HSLB HSLB board HSLB Developed by IHEP 10 計測システム研究会 @ 函館アリーナ 2017.10.2

読み出しボードでのデータ処理 ➢ Readout board : COPPER ( COmmon Pipelined. Platform for Electronics Readout ) ➢ Versatile DAQ board developed at KEK -> basically same functionality in the previous Belle experiment ➢ can be equipped with various I/O cards and CPU card -> new daughter-boards for Belle II are used • CPU: Intel Atom 1.6GHz Z530P • DDR2 SDRAM 512MB • PXE boot from ROPC PrPMC on COPPER • Gigabit Ethernet x1 Ethernet COPPER board COPPER CPU (PrPMC) Readout Onboard Device Driver Process Send Read PC FIFO data data Data PMC HSLB processor Belle2link HSLB ➢ Data processing on COPPER CPU ➢ Data formatting (Add header and trailer HSLB to raw data) ➢ Plain data check Trigger/clock ➢ Event incrementation, check magic HSLB word etc. ➢ Add XOR checksum GbE port x2(onboard and PrPMC) ➢ Report data-flow status to slow control 11 計測システム研究会 @ 函館アリーナ 2017.10.2

読み出し PC 上でのデータ処理 I. data check by data-handler process I. Calculate CRC16 and compare CRC value attached by FEE II. XOR checksum calculated by software on COPPER II. Data size reduction merging redundant header/trailer attached by b2link and COPPER ) Reduction by 15MB/s/ROPC at 30kHz trigger rate( <- 5COPPERs/ROPC, 4HSLB/COPPER ) III. Collect data from several COPPERs and do partial event-building and send data to High level trigger unit. ROPC( Readout PC) Data handler COPPER Gigabit Ethernet Gigabit Ethernet Gigabit Ethernet High level trigger Network switch Network switch 10GbE Partial Event Event builder/ COPPER builder Data handler … … Data handler COPPER Other ROPCs 12 計測システム研究会 @ 函館アリーナ 2017.10.2

イントロダクション 1. Belle II データ読み出しシステム 2. DAQ システムのパフォーマンス 3. 外層検出器の宇宙線試験 4. Belle II 読み出し系のアップグレード計画 5. 13 計測システム研究会 @ 函館アリーナ 2017.10.2

各検出器での Belle II のイベントサイズ見積もり Add header/footer, Fill data in raw-data format More detailed data size estimation for some sub-detectors MC result Packer Raw (ROOT with MC data to consider assignment of readout boards. data software objects) 1input / COPPER 4inputs / COPPER SVD CDC ➢ Difference of event size is handled by the number of receiver cards on COPPER ➢ SVD : 1HSLBs/COPPER ➢ ECL : 2HSLBs/COPPER ➢ CDC/TOP/ARICH/KLM : TOP 4HSLBs/COPPER 4inputs / COPPER ARICH 4inputs / COPPER 14 計測システム研究会 @ 函館アリーナ 2017.10.2

パフォーマンス測定 (1) : FEE と COPPER CPU Detec COPP HLT/st FEE ROPC tor ER orage Tested here ➢ Test setup Dummy trigger source Readout PC Belle2link CDC HSLB PrPMC FEE nc > /dev/null Belle2link CDC HSLB FEE CDC HSLB FEE CDC FEE HSLB COPPER We can test ➢ data-transfer performance of belle 2link ➢ CPU usage on COPPER PrPMC 15 計測システム研究会 @ 函館アリーナ 2017.10.2

結果: CPU usage on COPPER PrPMC Input trigger rate = 30kHz Throughput from COPPER Input trigger rate = 30kHz others SVD ECL PrPMC PrPMC PrPMC HSLB HSLB HSLB HSLB HSLB ➢ 30kHz operation was achieved. HSLB ➢ CPU usage will be the bottleneck when the HSLB COPPER COPPER COPPER event size becomes larger than expected. CDC ECL SVD TOP ➢ Throughput in Belle2link and Gigabit Ethernet to ARICH a readout PC has still enough remaining room. KLM 16 計測システム研究会 @ 函館アリーナ 2017.10.2

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.