Automatic MOSFET Sizing to Maximize the Lifetime Yield of Analog - PowerPoint PPT Presentation

Technische Universitt Mnchen Automatic MOSFET Sizing to Maximize the Lifetime Yield of Analog Circuits Husni Habal Technical University of Munich Department of Electrical Engineering and Information Technology The Institute for Electronic

Technische Universität München Automatic MOSFET Sizing to Maximize the Lifetime Yield of Analog Circuits Husni Habal Technical University of Munich Department of Electrical Engineering and Information Technology The Institute for Electronic Design Automation

Technische Universität München Contents Overview of the circuit sizing flow Degradation modeling in analog circuits – Problems and workarounds – Circuit example Lifetime yield analysis Design centering – Circuit example Conclusion 2

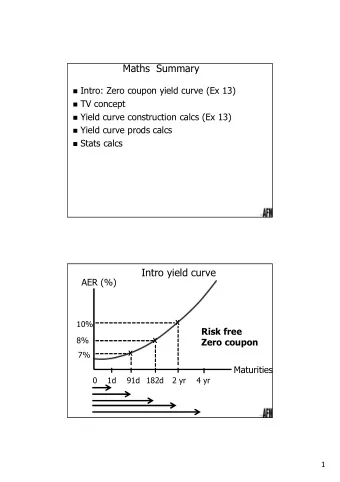

Technische Universität München Overview of circuit sizing Design centering algorithm Components of the design framework Design centering Lifetime yield analysis Lifetime yield analysis Performance simulation Degradation modeling Degradation modeling , Performance simulation Design parameters MOSFET width (W), length (L) Operating parameters Temperature (T), Supply (Vdd) Statistical process parameters Threshold voltage (Vth), Toxe Operating time Hours, days, years Parameter degradation , Performances slew rate, gain, power Parametric yield 3

Technische Universität München Contents Design centering algorithm Overview of the circuit sizing flow Degradation modeling in analog circuits Lifetime yield analysis – Problems and workarounds – Circuit example Degradation modeling , Performance simulation Lifetime yield analysis Constrained design centering – Circuit example Conclusion 4

Technische Universität München Degradation modeling s g _ + d 5

Technische Universität München Degradation modeling – analog implementation Differential input stage with cyclostationary analog input signal period = 10 µs stress+recovery period = 2 hours Vin S + - S S R R “Lifetime” = 10 days Problem: The bias point is not fixed – – are the node voltages, is the circuit state equation, is an incidence matrix – is periodic with a signal period – the vector of change in all circuit devices 6

Technische Universität München Degradation modeling – analog implementation Differential input stage with cyclostationary analog input signal period = 10 µs stress+recovery period = 2 hours Vin S + - S S R R “Lifetime” = 10 days Solution: – At small timescales when , (fixed) – Average the Fermi-level dependency over the input period – Recalculate at large time steps to accommodate changes in – Computational cost: a transient simulation for each recalculation 7

Technische Universität München Degradation modeling – analog implementation Differential input stage with realistic cyclostationary analog input Vin + - Cost: 5 transient simulations 8

Technische Universität München Degradation modeling – performance simulation Simulate the effect of degradation on circuit performances – is the duration needed for calculation of – Performance simulation: Design centering algorithm Lifetime yield analysis Degradation modeling , Performance simulation 9

Technische Universität München Degradation modeling – performance simulation Simulate the effect of degradation on circuit performances – is the duration needed for calculation of – Performance simulation: Example: simulate step response to calculate settling time Vin + - 10

Technische Universität München Degradation modeling – performance simulation Simulate the effect of degradation on circuit performances – is the duration needed for calculation of – Performance simulation: Problem: need to model degradation during performance simulation ( ) Vin + - 11

Technische Universität München Degradation modeling – performance simulation Simulate the effect of degradation on circuit performances – is the duration needed for calculation of – Performance simulation: Problem: need to model degradation during performance simulation ( ) Solution: if , then ; ; the flow becomes [Habal and Graeb, ICICDT2013] Design centering algorithm Lifetime yield analysis Performance simulation Degradation modeling 12

Technische Universität München Contents Overview of the circuit sizing flow Degradation modeling in analog circuits – Problems and workarounds – Circuit example Lifetime yield analysis Design centering algorithm Design centering – Circuit example Lifetime yield analysis Conclusion Performance simulation Degradation modeling 13

Technische Universität München Circuit example 45 nm tech [pdk.cadence.com] 39 process parameters 33 design parameters NBTI and HCI modeled Operating parameter ranges Sized without considering degradation 14

Technische Universität München Circuit example 15

Technische Universität München Circuit example 16

Technische Universität München Circuit example Operating parameter dependency – – Need to consider the worst-case operating corner for degradation: Open loop Gain 17

Technische Universität München Contents Overview of the circuit sizing flow Degradation modeling in analog circuits – Problems and workarounds – Circuit example Lifetime yield analysis Design centering algorithm Design centering – Circuit example Lifetime yield analysis Conclusion Performance simulation Degradation modeling 18

Technische Universität München Fresh yield analysis [Graeb 2007] Gaussian distribution of statistical parameters with mean and covariance 19

Technische Universität München Fresh yield analysis [Graeb 2007] Vdd T Gaussian distribution of statistical parameters with mean and covariance Tolerance box for the operating parameters 20

Technische Universität München Fresh yield analysis [Graeb 2007] Vdd T Fresh yield analysis: Bijective mapping bwtween and yield: -1 0 1 2 3 4 15.9% 50% 84.1% 97.7% 99.9% 99.99% 21

Technische Universität München Lifetime yield analysis Extend the domain of operating parameters with a circuit lifetime Operating domain Lifetime yield analysis becomes Incremental cost is the cost of an additional operating parameter 22

Technische Universität München Contents Overview of the circuit sizing flow Degradation modeling in analog circuits – Problems and workarounds – Circuit example Lifetime yield analysis Design centering algorithm Design centering – Circuit example Lifetime yield analysis Conclusion Performance simulation Degradation modeling 23

Technische Universität München Design centering 1 iteration is a function of the design parameters Design centering formulation Terminate when yield is satisfactory or no new step is possible 24

Technische Universität München Design centering – circuit example 39 process parameters 33 design parameters Operating parameter ranges 25

Technische Universität München Design centering – circuit example 39 process parameters 33 design parameters Operating parameter ranges Specifications 60 dB < CMRR 80 dB < Gain 1.5 mV < IOV < 1.5 mV 5 V/us < Slew rate 60 dB < PSRR 26 7 MHz < UGBW

Technische Universität München Design centering – circuit example 39 process parameters Fresh yield Lifetime yield 33 design parameters optimization optimization Operating parameter ranges Performance 1.6 3.7 simulation Cost in CPU time (hours) Degradation N/A 15.1 For lifetime yield analysis: modeling ~ 1000 Performance simulations ~ 3000 Degradation simulations 27

Technische Universität München Design centering – circuit example 39 process parameters 33 design parameters Operating parameter ranges Multi-objective optimization – Yield versus circuit area 20 40 60 80 (%) none <400 <360 <320 <300 <280 (um2) 28

Technische Universität München Conclusion NBI degradation model suitable for analog circuit design Decoupling of degradation and performance simulation [ICICDT 2013] Simple extension to calculate lifetime yield analysis Demonstration on a circuit example Future work New circuit examples 29

Technische Universität München Backup slides Husni Habal Technical University of Munich Department of Electrical Engineering and Information Technology The Institute for Electronic Design Automation 30

Technische Universität München Significance of lifetime sizing rules Define the feasible region of operation Aid optimization and reduce cost Typically sharp changes in the performance functions will be avoided 31

Technische Universität München Background 32

Technische Universität München Problems + - 33

Technische Universität München Problems 34

Technische Universität München New solutions 35

Technische Universität München New solutions 36

Technische Universität München New solutions 37

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![TDR Assumptions for Pulsed Neutron Yield [/keV] Neutron Yield [/keV] 2500 2000 2000 2500](https://c.sambuz.com/892356/tdr-assumptions-for-pulsed-s.webp)