Automatic Generation of 100 Gbps Packet Parsers from P4 Description - PowerPoint PPT Presentation

Automatic Generation of 100 Gbps Packet Parsers from P4 Description cek 1 s 1 a 2 Pavel Ben a Viktor Pu Hana Kub atov 1 Liberouter CESNET 2 Faculty of Information Technology Czech Technical University in Prague H 2 RC Workshop,

Automatic Generation of 100 Gbps Packet Parsers from P4 Description cek 1 s 1 a 2 Pavel Ben´ aˇ Viktor Puˇ Hana Kub´ atov´ 1 Liberouter CESNET 2 Faculty of Information Technology Czech Technical University in Prague H 2 RC Workshop, November 2015 H 2 RC 2015 Ben´ aˇ cek, Puˇ s, Kub´ atov´ a 100 Gbps Packet Parser from P4 1 / 12

Introduction OpenFlow is a very popular protocol for realization of SDN ( S oftware D efined N etworking) Pros and Cons: ◮ + Allows us to decouple control and data plane ◮ + Provides a way to fill match tables of switches at runtime ◮ - Not possible to change set of supported protocols (parsers are fixed) Researchers are looking for a solution of this disadvantage ◮ P4 language is the next step in the SDN concept realization Our paper introduces a generator which transforms P4 source to the FPGA parser’s architecture H 2 RC 2015 Ben´ aˇ cek, Puˇ s, Kub´ atov´ a 100 Gbps Packet Parser from P4 2 / 12

P4 P rogramming P rotocol-independent P acket P rocessors Language with relatively simple syntax Provides a way to define packet processing functionality of network devices Defines following aspects of packet processing: Header Formats 1 packet parser definition Packet Parser 2 Table Specification 3 match to action mapping Control Program 4 Action Specification 5 H 2 RC 2015 Ben´ aˇ cek, Puˇ s, Kub´ atov´ a 100 Gbps Packet Parser from P4 3 / 12

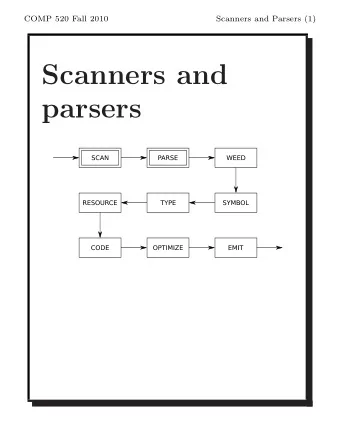

Parser structure Two basic types of modules are connected to pipeline Protocol Analyzer - understands one protocol from the protocol stack 1 ⋆ Data extraction ⋆ Computes the next protocol type in the stack ⋆ Computes the next protocol starting offset Pipeline - used to tune the final frequency and latency 2 Unified interface for easy connection of modules P P P P I I I I P P P P Input IP TCP/UDP Ethernet E E E E Analyzer Analyzer Analyzer . . . . Eth IP TCP Ethernet Frame 0 1 2 3 IP TCP Eth H 2 RC 2015 Ben´ aˇ cek, Puˇ s, Kub´ atov´ a 100 Gbps Packet Parser from P4 4 / 12

Transformation Algorithm Structure of protocol analyzer is generated from the P4’s Header Format Parser’s structure is inferred from P4’s Packet Parser Basic idea of parser’s structure identification We have to identify the latest usage of the protocol in the parser. Algorithm for the identification of the latest usage: DFS (Depth First Search) This can be done in P arser G raph R epresentation (PGR) ◮ Directed acyclic graph ◮ Represents relations between protocols ◮ Created from P4 description H 2 RC 2015 Ben´ aˇ cek, Puˇ s, Kub´ atov´ a 100 Gbps Packet Parser from P4 5 / 12

Transformation Algorithm - Example ICMPv6 3 Unknown IPv6 2 TCP 3 VLAN Logical model (PGR) 1 Unknown Eth UDP 0 3 IPv4 2 Unknown ICMP 3 Unknown Physical model H 2 RC 2015 Ben´ aˇ cek, Puˇ s, Kub´ atov´ a 100 Gbps Packet Parser from P4 6 / 12

Results We have tested two protocol stacks: ◮ Simple L2 - Ethernet, IPv4/IPv6, TCP/UDP, ICMP/ICMPv6 ◮ Full - Ethernet, 2x VLAN, 2x MPLS, IPv4/IPv6, TCP/UDP, ICMP/ICMPv6 Possible optimizations: ◮ Automatic - Optimizations of internal parser’s structure ⋆ O1 - Offset bus optimization ⋆ O2 - Multiplexer optimization ◮ Manual - Tweaked P4 program (O3) We performed synthesis for our implementation platform: ◮ Equipped with Xilinx Virtex 7 FPGA ◮ Suports 100 Gbps H 2 RC 2015 Ben´ aˇ cek, Puˇ s, Kub´ atov´ a 100 Gbps Packet Parser from P4 7 / 12

Results - Latency 70 hand,pareto,simple L2 P4,O2,pareto,simple L2 hand,pareto,full 60 P4,O2,pareto,full 50 40 Latency [ns] 30 20 10 0 0 50 100 150 Throughput [Gbps] H 2 RC 2015 Ben´ aˇ cek, Puˇ s, Kub´ atov´ a 100 Gbps Packet Parser from P4 8 / 12

Results - Resources 14000 hand,pareto,simple L2 P4,O2,pareto,simple L2 hand,pareto,full 12000 P4,O2,pareto,full 10000 Slice LUT [-] 8000 6000 4000 2000 0 0 50 100 150 Throughput [Gbps] H 2 RC 2015 Ben´ aˇ cek, Puˇ s, Kub´ atov´ a 100 Gbps Packet Parser from P4 9 / 12

Conclusion We implemented and evaluated our generator of parsers Parsers are capable to process 100 Gbps From presented work we can infer following important results: Ability to generate parsers with equal functionality in shorter time 1 Generated parsers aren’t significantly worse than hand optimized versions created by a 2 professional with many years of experience in HDL coding Future work: ◮ Deparser - construction of packets ◮ Match+Action tables - general processing of extracted data H 2 RC 2015 Ben´ aˇ cek, Puˇ s, Kub´ atov´ a 100 Gbps Packet Parser from P4 10 / 12

Thank you for your attention Pavel Ben´ aˇ cek www.liberouter.org @liberouter Visit our business partner in booth #3011 H 2 RC 2015 Ben´ aˇ cek, Puˇ s, Kub´ atov´ a 100 Gbps Packet Parser from P4 11 / 12

Protol Analyzer Protocol Analyzer (3) Input Protocol Next Data (6) Output Protocol Protocol Extractor Decoder (4) Extracted Data Data (1) Input Data Extractor (2) Input O ✁ set (5) Output O ✁ set + Data Extractor Length Gen. H 2 RC 2015 Ben´ aˇ cek, Puˇ s, Kub´ atov´ a 100 Gbps Packet Parser from P4 12 / 12

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.