Anne Bracy CS 3410 Computer Science Cornell University The - PowerPoint PPT Presentation

Anne Bracy CS 3410 Computer Science Cornell University The slides are the product of many rounds of teaching CS 3410 by Professors Weatherspoon, Bala, Bracy, and Sirer. See P&H

Anne ¡Bracy CS ¡3410 Computer ¡Science Cornell ¡University The ¡slides ¡are ¡the ¡product ¡of ¡many ¡rounds ¡of ¡teaching ¡CS ¡3410 ¡by ¡ Professors ¡ Weatherspoon, ¡Bala, ¡Bracy, ¡and ¡Sirer. See ¡P&H ¡Appendix ¡B.8 ¡(register ¡files) ¡and ¡B.9 ¡

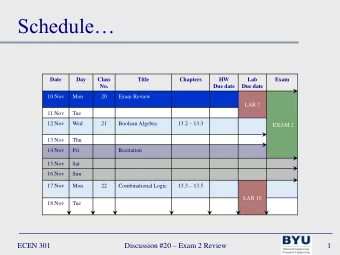

Homework1 ¡is ¡out Due ¡Friday, ¡September ¡25 th (Prelim ¡#1 ¡is ¡Tuesday, ¡September ¡29 th) Work ¡on ¡problems ¡incrementally, ¡as ¡we ¡cover ¡them ¡in ¡lecture ¡(i.e. ¡part ¡1) Office ¡Hours ¡for ¡help Make ¡sure ¡to ¡go ¡to ¡ your Lab ¡Section ¡this ¡week Completed ¡Lab1 ¡due ¡Friday, ¡September ¡18 Note, ¡a ¡ Design ¡Document ¡ is ¡due ¡when ¡you ¡submit ¡Lab1 ¡final ¡circuit Work ¡ alone Save ¡your ¡work! • Save ¡often . ¡ ¡Verify ¡file ¡is ¡non-‑zero. ¡ ¡Periodically ¡save ¡to ¡Dropbox, ¡email. • Beware ¡of ¡MacOSX 10.5 ¡(leopard) ¡ and ¡10.6 ¡(snow-‑leopard) Work ¡alone, BUT use ¡your ¡resources • Lab ¡Section, ¡Piazza.com, ¡Office ¡Hours • Class ¡notes, ¡book, ¡Sections, ¡CSUGLab

inst memory register alu file +4 +4 addr =? PC d in d out control cmp offset memory target new ¡ imm pc extend A ¡Single ¡cycle ¡processor

Memory • Register ¡Files • Tri-‑state ¡devices • SRAM ¡(Static ¡RAM—random ¡access ¡memory) • DRAM ¡(Dynamic ¡RAM)

inst memory register alu file +4 +4 addr =? PC d in d out control cmp offset memory target new ¡ imm pc extend A ¡Single ¡cycle ¡processor

Register ¡File • N ¡read/write ¡registers Q A 32 D W Dual-‑Read-‑Port • Indexed ¡by ¡ 32 Single-‑Write-‑Port register ¡number Q B 32 32 ¡x ¡32 ¡ Register ¡File W R W R A R B 1 5 5 5

Recall: ¡Register D0 • D ¡flip-‑flops ¡in ¡parallel ¡ • shared ¡clock D1 • extra ¡clocked ¡inputs: write_enable, ¡reset, ¡… D2 D3 4-‑bit 4 4 reg clk clk

Recall: ¡Register D0 • D ¡flip-‑flops ¡in ¡parallel ¡ • shared ¡clock D1 • extra ¡clocked ¡inputs: write_enable, ¡reset, ¡… D2 D3 32-‑bit 32 32 reg clk clk

Register ¡File D32 Reg 0 • N ¡read/write ¡registers Reg 1 …. • Indexed ¡by ¡ 5-‑to-‑32 register ¡number decoder Reg 30 Reg 31 5R W W How ¡to ¡write ¡to ¡ one register ¡in ¡the ¡register ¡file? • Need ¡a ¡decoder

Register ¡File D32 Reg 0 • N ¡read/write ¡registers Reg 1 …. • Indexed ¡by ¡ 5-‑to-‑32 register ¡number decoder Reg 30 Reg 31 5R W W How ¡to ¡write ¡to ¡ one register ¡in ¡the ¡register ¡file? • Need ¡a ¡decoder

Register ¡File 32 Reg 0 • N ¡read/write ¡registers Reg 1 32Q A M …. …. • Indexed ¡by ¡ U X register ¡number Reg 30 Reg 31 M 32Q B …. U X How ¡to ¡read ¡from ¡two ¡registers? • Need ¡a ¡multiplexor 5 5 R A R B

Register ¡File D32 32 Reg 0 • N ¡read/write ¡registers Reg 1 32Q A M …. …. • Indexed ¡by ¡ U 5-‑to-‑32 X register ¡number decoder Reg 30 Reg 31 M Implementation: 32Q B …. U X • D ¡flip ¡flops ¡to ¡store ¡bits • Decoder ¡for ¡each ¡write ¡port • Mux for ¡each read ¡port 5 5 5 R A W R W R B

Register ¡File • N ¡read/write ¡registers Q A 32 D W Dual-‑Read-‑Port • Indexed ¡by ¡ 32 Single-‑Write-‑Port register ¡number Q B 32 32 ¡x ¡32 ¡ Register ¡File W R W R A R B Implementation: 1 5 5 5 • D ¡flip ¡flops ¡to ¡store ¡bits • Decoder ¡for ¡each ¡write ¡port • Mux for ¡each read ¡port

Register ¡File What ¡happens ¡if ¡same ¡ • N ¡read/write ¡registers register ¡read ¡and ¡written ¡ • Indexed ¡by ¡ during ¡same ¡clock ¡cycle? register ¡number Implementation: • D ¡flip ¡flops ¡to ¡store ¡bits • Decoder for ¡each ¡write ¡port • Mux for ¡each read ¡port

8-‑to-‑1 ¡mux a Register ¡File ¡tradeoffs b + Very ¡fast ¡(a ¡few ¡gate ¡delays ¡for ¡ c both ¡read ¡and ¡write) d + Adding ¡extra ¡ports ¡is ¡ straightforward e – Doesn’t ¡scale f e.g. ¡32Mb ¡register ¡file ¡with ¡ g 32 ¡bit ¡registers h Need ¡32x ¡1M-‑to-‑1 ¡multiplexor ¡ and ¡32x ¡20-‑to-‑1M ¡decoder How ¡many ¡logic ¡gates/transistors? s 2 s 1 s 0

Register ¡files ¡are ¡very ¡fast ¡storage ¡(only ¡a ¡few ¡gate ¡ delays), ¡but ¡does ¡not ¡scale ¡to ¡large ¡memory ¡sizes.

Memory • CPU: ¡Register ¡Files ¡(i.e. ¡Memory ¡w/in ¡the ¡CPU) • Scaling ¡Memory: ¡Tri-‑state ¡devices • Cache: ¡SRAM ¡(Static ¡RAM—random ¡access ¡memory) • Memory: ¡DRAM ¡(Dynamic ¡RAM)

How ¡do ¡we ¡scale/build ¡larger ¡memories?

Need ¡a ¡shared ¡bus (or ¡shared ¡bit ¡line) • Many ¡FlipFlops/outputs/etc. ¡connected ¡to ¡single ¡wire • Only ¡one ¡output ¡ drives the ¡bus ¡at ¡a ¡time D 0 S 0 D 1 S 1 D 2 S 2 D 3 S 3 D 1023 S 1023 shared ¡line • How ¡do ¡we ¡build ¡such ¡a ¡device?

Tri-‑State ¡Buffers If ¡enabled ¡(E=1), ¡then ¡Q ¡= ¡D • Otherwise, ¡Q ¡is ¡not ¡connected ¡(z ¡= ¡high ¡impedance) ¡ • E D Q E D Q 0 0 z z 0 ¡ 1 1 0 0 1 1 1

D 0 S 0 D 1 S 1 D 2 S 2 D 3 S 3 D 1023 S 1023 shared ¡line

Register ¡files ¡are ¡very ¡fast ¡storage ¡(only ¡a ¡few ¡gate ¡ delays), ¡but ¡does ¡not ¡scale ¡to ¡large ¡memory ¡sizes. Tri-‑state ¡Buffers ¡allow ¡scaling ¡since ¡multiple ¡ registers ¡can ¡be ¡connected ¡to ¡a ¡single ¡output, ¡while ¡ only ¡one ¡register ¡actually ¡drives ¡the ¡output.

Memory • CPU: ¡Register ¡Files ¡(i.e. ¡Memory ¡w/in ¡the ¡CPU) • Scaling ¡Memory: ¡Tri-‑state ¡devices • Cache: ¡SRAM ¡(Static ¡RAM—random ¡access ¡memory) • Memory: ¡DRAM ¡(Dynamic ¡RAM)

How ¡do ¡we ¡build ¡large ¡memories? Use ¡similar ¡designs ¡as ¡Tri-‑state ¡Buffers ¡to ¡connect ¡ multiple ¡registers ¡to ¡output ¡line. ¡ ¡Only ¡one ¡register ¡ will ¡drive ¡output ¡line.

• Storage ¡Cells ¡+ ¡plus ¡Tri-‑State ¡Buffers • Inputs: ¡Address, ¡Data ¡(for ¡writes) • Outputs: ¡Data ¡(for ¡reads) • Also ¡need ¡R/W ¡signal ¡(not ¡shown) 22 Address 8 Data

• Storage ¡Cells ¡+ ¡plus ¡Tri-‑State ¡Buffers • A ¡decoder ¡selects ¡which ¡line ¡of ¡memory ¡to ¡access ¡ (i.e. ¡word ¡line) Data • A ¡R/W ¡selector determines ¡the ¡ type ¡of ¡access • That ¡line ¡is ¡then ¡coupled ¡to ¡ the ¡data ¡lines Address Decoder

D in [1] D in [2] E.g. ¡How ¡do ¡we ¡design ¡ D Q D Q a ¡4 ¡x ¡2 ¡Memory ¡Module? enable enable 0 (i.e. ¡4 ¡word ¡lines ¡that ¡are D Q 2-‑to-‑4 D Q decoder each ¡2 ¡bits ¡wide)? enable enable 1 2 4 ¡x ¡2 ¡Memory D Q Address D Q enable enable 2 D Q D Q enable enable 3 Write ¡Enable Output ¡Enable D out [1] D out [2]

D in [1] D in [2] E.g. ¡How ¡do ¡we ¡design ¡ a ¡4 ¡x ¡2 ¡Memory ¡Module? enable enable 0 (i.e. ¡4 ¡word ¡lines ¡that ¡are 2-‑to-‑4 decoder each ¡2 ¡bits ¡wide)? enable enable 1 2 Address enable enable 2 enable enable 3 Write ¡Enable Output ¡Enable D out [1] D out [2]

D in [1] D in [2] E.g. ¡How ¡do ¡we ¡design ¡ a ¡4 ¡x ¡2 ¡Memory ¡Module? enable enable 0 (i.e. ¡4 ¡word ¡lines ¡that ¡are 2-‑to-‑4 decoder each ¡2 ¡bits ¡wide)? enable enable 1 2 Address enable enable 2 Bit ¡lines enable enable 3 Write ¡Enable Output ¡Enable D out [1] D out [2]

D in [1] D in [2] E.g. ¡How ¡do ¡we ¡design ¡ a ¡4 ¡x ¡2 ¡Memory ¡Module? enable enable 0 (i.e. ¡4 ¡word ¡lines ¡that ¡are 2-‑to-‑4 decoder each ¡2 ¡bits ¡wide)? enable enable 1 2 Address enable enable 2 Word ¡lines enable enable 3 Write ¡Enable Output ¡Enable D out [1] D out [2]

Typical ¡SRAM ¡Cell bit ¡line Pass-‑Through Transistors word ¡line " B B Each ¡cell ¡stores ¡one ¡bit, ¡and ¡requires ¡4 ¡– 8 ¡transistors ¡(6 ¡is ¡typical)

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.