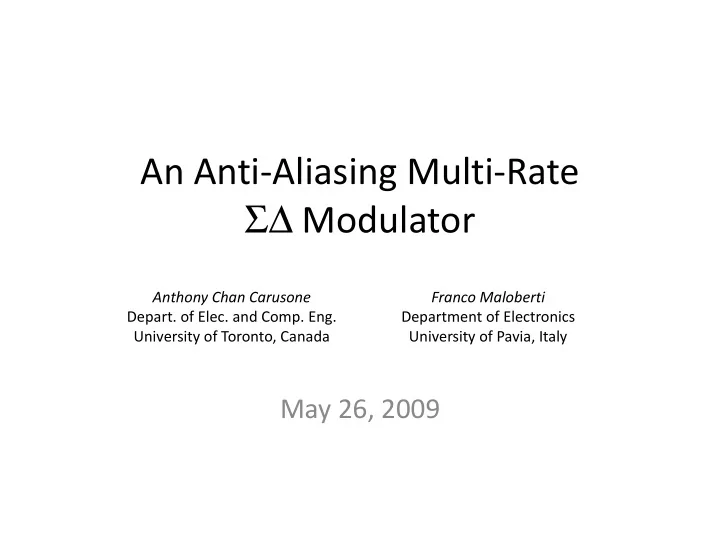

An Anti-Aliasing Multi-Rate Modulator Anthony Chan Carusone Franco - PowerPoint PPT Presentation

An Anti-Aliasing Multi-Rate Modulator Anthony Chan Carusone Franco Maloberti Depart. of Elec. and Comp. Eng. Department of Electronics University of Toronto, Canada University of Pavia, Italy May 26, 2009 Outline Motivation and

An Anti-Aliasing Multi-Rate Σ∆ Modulator Anthony Chan Carusone Franco Maloberti Depart. of Elec. and Comp. Eng. Department of Electronics University of Toronto, Canada University of Pavia, Italy May 26, 2009

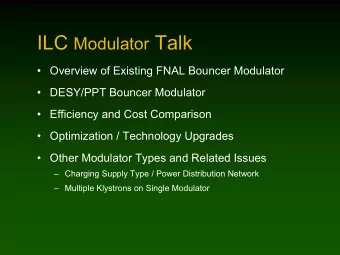

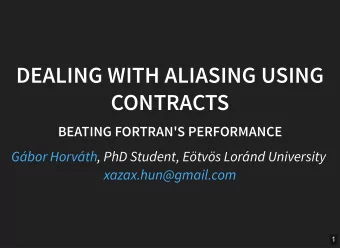

Outline • Motivation and background • Anti-aliasing multi-rate modulator front-end • Practical considerations – Mismatch – Mismatch – Clocking – Opamp settling requirements • Simulation results • Conclusions 2

Aliasing in Discrete-Time Σ∆ Modulators Desired signal Alias … … … … f f s f s 0 2f s 2OSR 3

Anti-Aliasing in Discrete-Time Σ∆ Modulators Desired signal Desired signal Alias Alias … … … … f f f s f s 0 0 f s f s 2f s 2f s 0 0 f s f s 2f s 2f s s s 2OSR 2OSR Σ∆ DSP AAF f s AAF may be either a continuous-time filter or a discrete-time filter operating at a higher sampling rate [6,7], Mf s 4

Discrete-Time Σ∆ Modulator with Discrete-Time Anti-Aliasing Filter Σ∆ L(z) M Mf s f s Basic idea is to incorporate L(z) into the front- end of the Σ∆ modulator with minimal circuit overhead 5

“Hybrid” Σ∆ Modulators from DAC to C i modulator in There are several examples of modulators incorporating a continuous-time front-end to provide an anti-aliasing STF [1-5], but these are still susceptible to clock jitter, like all CT modulators. 6

Conventional Σ∆ Modulator Front-end from DAC C φ 1 φ i C i in to φ 1 φ i modulator ⁄ C C i in - - - - - - - - - - - - - - - - – 1 1 – z to modulator from DAC 7

Σ∆ Modulator with Anti-Aliasing Front-end Sampler from SC-DAC C 1 C i in φ 1 1 φ 2 , f s φ 2 φ 1 1 , to modulator from DAC C 2 φ 2 φ 1 2 , C C φ φ 1 φ i φ C i C i in φ 2 φ 1 2 , φ 1 1 , to φ 1 φ i φ 1 2 modulator , φ 2 1 φ 1 , φ 2 φ 1 φ 2 1 φ 2 1 , , φ 2 2 φ 2 2 φ 1 , , φ 1 φ 2 2 φ 1 , 8

Σ∆ Modulator with Anti-Aliasing Front-end Sampler from SC-DAC C 1 C i in φ 1 1 φ 2 , f s φ 2 φ 1 1 , to modulator C 2 φ 2 φ 1 2 , Mf s φ 2 φ 1 2 f s , φ 1 1 , M in – k ) z 1 – ( ⁄ C k C C i z φ 1 2 ∑ - -- -- -- -- -- -- -- -- -- -- -- -- , - - - - - - M z 1 – φ 2 1 φ 1 C 1 – to , k = 1 φ 2 modulator φ 1 φ 2 1 from DAC φ 2 1 , , φ 2 2 φ 2 2 φ 1 , , φ 1 φ 2 2 φ 1 , 9

Σ∆ Modulator with Anti-Aliasing Front-end Sampler Σ∆ L(z) M Similar approach has been applied to Mf s Mf s f s f s integrate anti- integrate anti- aliasing into the front-end of a Mf s f s discrete-time filter [8,9] and M in – k ) z 1 – ( ⁄ C k C C i z ∑ - -- -- -- -- -- -- -- -- -- -- -- -- SAR ADC [10] - - - - - - M z 1 – C 1 – to k = 1 modulator from DAC 10

Other “Multi-Rate” Σ∆ Modulators f s e.g. [11]: Mf s ∫ ∫ ↑ M H ( z ) 2 ↓ M 11

Other “Multi-Rate” Σ∆ Modulators f s e.g. [11]: Mf s ∫ ∫ ↑ M H ( z ) 2 ↓ M Multi-bit quantizer is replaced by a single-bit modulator + decimator operating at increased sampling rate 12

Choice of capacitor values, C k Zeros of L ( z ) with M = 5 : 1 1 C k chosen to maximize C k = ( C / M ) anti-aliasing around f s 13

Choice of capacitor values, C k C k “optimized” C k = ( C / M ) Increased width of the anti-aliasing notch is particularly important in low-OSR modulators 14

Capacitor Mismatch Alias frequency band for OSR = 24 C k = ( C / M ) C k “optimized” 100 Monte-Carlo frequency responses with capacitor value standard deviation of 0.2% 15

from SC-DAC Clocking C 1 C i in φ 1 1 φ 2 , f s φ 2 φ 1 1 , to • This scheme requires the modulator generation of multiple C 2 φ 2 φ 1 2 clock phases [2] , • Faster settling of the φ 2 φ 1 2 , φ 1 1 sampling capacitors , necessitates larger φ φ 1 2 , switches and, hence, φ 2 1 φ 1 some overhead in the , φ 2 clock distribution φ 1 φ 2 1 φ 2 1 , , • Skew between the clock φ 2 2 phases results in harmonic φ 2 2 φ 1 , , at f s ± f in , which will be filtered by the following φ 1 φ 2 2 φ 1 , digital decimation filter 16

Opamp Settling Time Conventional Σ∆ Σ∆ Σ∆ modulator front-end Σ∆ Anti-aliasing multi-rate Σ∆ Σ∆ modulator Σ∆ Σ∆ during the integration phase: front-end during the integration phase: ≈ ⁄ C 2 C i C i C C in C in Since only ½ of the total sampling capacitance is integrated at any time, the feedback factor in the integration phase is increased, thus permitting the use of an opamp with lower GBW. 17

Aliased tone (a) Simulation Results SNDR = 28.5 dB • 3 rd -oder modulator • OSR = 24 (b) • Two-tone input: SNDR = 62.3 dB – -2 dBFS in-band – -30 dBFS at 0.98 f s s a) Conventional front-end b) Anti-aliasing multi-rate front-end with M = 5 (c) and C k = C / M SNDR = 84.3 dB c) Anti-aliasing multi-rate front-end with M = 5 and optimized C k 18

Simulation Results 35 dB 30 dB 19

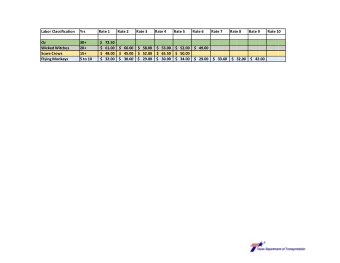

Conclusions • Splitting the input sampling capacitor in a discrete-time Σ∆ modulator into multiple parallel branches sampled at increased rate enables the STF to be shaped by an FIR transfer function, here used for anti-aliasing used for anti-aliasing • Example 3 rd -order modulator with OSR=24 and M=5 demonstrates: – 35 dB of anti-aliasing is provided by a uniformly segmented input sampling capacitor, C k = C /5 – An additional 30 dB of anti-aliasing is provided when the values of C k are optimized for a total of 65 dB of anti-aliasing 20

EXTRAS 21

Simulation Model 22

Table of optimized capacitor values 23

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.