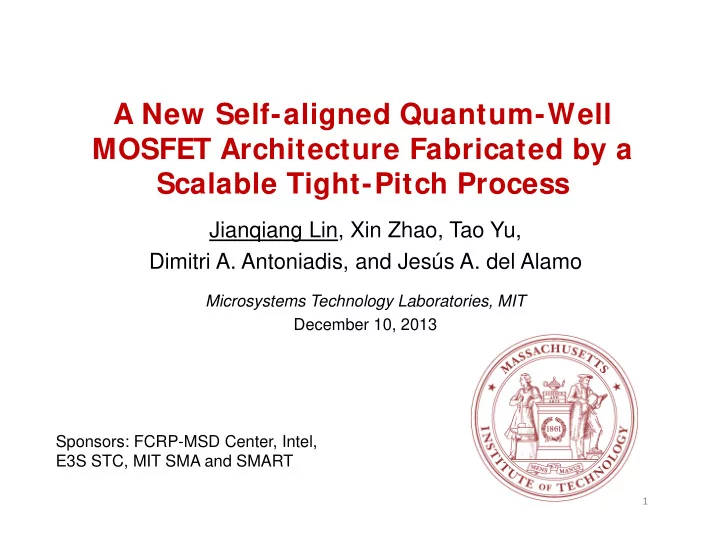

A New Self-aligned Quantum-Well MOSFET Architecture Fabricated by a - PowerPoint PPT Presentation

A New Self-aligned Quantum-Well MOSFET Architecture Fabricated by a Scalable Tight-Pitch Process Jianqiang Lin, Xin Zhao, Tao Yu, Dimitri A. Antoniadis, and Jess A. del Alamo Microsystems Technology Laboratories, MIT December 10, 2013

A New Self-aligned Quantum-Well MOSFET Architecture Fabricated by a Scalable Tight-Pitch Process Jianqiang Lin, Xin Zhao, Tao Yu, Dimitri A. Antoniadis, and Jesús A. del Alamo Microsystems Technology Laboratories, MIT December 10, 2013 Sponsors: FCRP-MSD Center, Intel, E3S STC, MIT SMA and SMART 1

Motivation • Superior electron transport properties in InAs channel [J. del Alamo, Nature 2011] InAs HEMTs Strained Si V DS =0.5 V Si V DS =1.1-1.3 V 2 2

InGaAs MOSFET evolution Performance (Kim, IEDM 2012) [del Alamo, ESSDERC 2013] Fabrication and Scaling 3

InGaAs MOSFET evolution Performance (This work) (Kim, IEDM 2012) [del Alamo, ESSDERC 2013] Fabrication and Scaling 4

New InGaAs MOSFET with self-aligned LEDGE • Bottleneck to ON current is R sd • Introduction of highly conductive “LEDGE” – n + region linking metal contact and channel 5

Process integration Key features: Wet-etch free / Lift-off free / Au free Gate opening 3-step gate recess Ohmic/Oxide deposition* Gate metal ALD deposition Pad formation 6

Composite W/Mo contact • Without W: Long undercut of Mo due to oxidation – Limits S/D metal spacing • With W: No Mo oxidation Air void s This work [Lin, IEDM 2012] 7

3-step gate recess process Digital etch*: CF 4 +O 2 RIE * Cl-based RIE O 2 plasma + H 2 SO 4 *[Waldron, IEDM 2007] *[Lin, EDL submitted] Process enables precise control of: t ch / L ledge / t ledge L g L ledge t ledge t ch 8

Semiconductor surface after recess Only wet cleaning Additional cap dry etch (~ 20 (no etching) nm) + 4 cycle digital etch 5 nm RMS = 0.12 nm RMS = 0.21 nm Scanning area: 2x2 m 2 9

Structure design: Ledge Short Ledge Long Ledge 10

Structure design: Ledge Short Ledge Long Ledge • Surface channel: In 0.7 Ga 0.3 As / InAs / In 0.7 Ga 0.3 As = 1/2/5 nm 11 • High-k: HfO 2 , thickness =2.5 nm (EOT~0.5 nm)

Output and g m characteristics for L g = 70 nm V gs -V t = 0 to 0.5 V in 0.1 V step 1.0 3.0 L ledge =5 nm, L ledge = 5 nm 2.5 2.7 mS/ m 0.8 L ledge = 70 nm I d (mA/ m) g m (mS/ m) 2.0 L ledge =70 nm, 0.6 1.9 mS/ m 1.5 0.4 1.0 0.2 0.5 V ds = 0.5 V 0.0 0.0 0.0 0.1 0.2 0.3 0.4 0.5 -0.4 -0.2 0.0 0.2 0.4 V ds (V) V gs (V) • R on = 220 m for L ledge = 5 nm • Record g m,max = 2.7 mS/ m at V ds = 0.5 V for L ledge = 5 nm 12

Subthreshold characteristics L ledge =70 nm L ledge =5 nm -3 -3 V ds =0.5 V 10 10 V ds =0.5 V S min =138 mV/dec S min =94 mV/dec -5 -5 I d (A/ m) 10 10 I d (A/ m) V ds =0.05 V V ds =0.05 V S min =90 mV/dec S min =108 mV/dec -7 -7 10 10 DIBL=249 mV/V DIBL=130 mV/V -9 -9 10 10 -0.4 -0.2 0.0 0.2 -0.2 0.0 0.2 0.4 V gs (V) V gs (V) • I g < 10 pA/µm over entire voltage range – Further EOT scaling possible 13

Subthreshold characteristics L ledge =70 nm L ledge =5 nm -3 -3 V ds =0.5 V 10 10 V ds =0.5 V S min =138 mV/dec Flattening S min =94 mV/dec tail at high -5 -5 I d (A/ m) 10 10 I d (A/ m) V ds V ds =0.05 V V ds =0.05 V S min =90 mV/dec S min =108 mV/dec -7 -7 10 10 DIBL=249 mV/V DIBL=130 mV/V -9 -9 10 10 -0.4 -0.2 0.0 0.2 -0.2 0.0 0.2 0.4 V gs (V) V gs (V) • I g < 10 pA/µm over entire voltage range – Further EOT scaling possible 14

L g = 20 nm InAs QW-MOSFET with L ledge = 5 nm V gs -V t = 0.5 V 1.0 L g =20 nm R on =224 m 0.8 I d (mA/ m) 0.4 V 0.6 0.4 0.2 0.0 0.0 0.1 0.2 0.3 0.4 0.5 V ds (V) • Smallest functional III-V MOSFET with tight contact spacing 15

Parasitic resistance analysis R probe = 5 m L ledge =70 nm, R sd =302 m R metal = 5 m R cont = 50 m 500 R ledge ~ 1 m/nm Pad R on ( m) R bar = 40 m 400 W/Mo Gate 300 L ledge =5 nm, n+ Cap R sd =206 m Channel 200 0 200 400 Buffer L g (nm) • For short ledge devices, major R sd contribution from R cont and R bar 16

Benchmark: I on InGaAs FETs 500 Planar Trigate 400 I on ( A/ m) MIT HEMT MIT MOSFET 2012 300 This work( L ledge =70 nm) This work( L ledge =5 nm) 200 I off =100 nA/ m, V dd =0.5 V * 100 0 50 100 150 200 L g (nm) * [Kim and del Alamo, T-ED 2008] • Record I on = 410 A/ m at L g =70 nm for L ledge =70 nm 17

Benchmark: g m,max vs. S 3.0 InGaAs FETs 2.5 Planar g m-max (mS/ m) Trigate 2.0 MIT HEMT Teledyne/MIT HEMT 1.5 MIT MOSFET 2012 This work( L ledge =70nm) 1.0 V ds = 0.5 V This work( L ledge =5 nm) 0.5 L g 70 nm 0.0 0 100 200 300 400 S min (mV/dec) • Short ledge MOSFETs show record g m,max • Long ledge MOSFETs match record S [Radosavljevic, IEDM 2011] 18

Impact of ledge on off-state leakage (Long MOSFETs) L g = 200 nm, L ledge = 70 nm L g = 500 nm, L ledge = 5 nm -4 -4 10 10 Flattening I d I d I d or I g (A/ m) -6 -6 tail at high 10 10 V ds -8 -8 10 10 V ds =0.1 to 0.6 V V ds =0.1 to 0.6 V -10 -10 I g 10 10 I g -12 -12 10 10 -14 -14 10 10 -0.4 -0.2 0.0 0.2 -0.2 0.0 0.2 0.4 V gs (V) V gs (V) • Short ledge leads to high I off • Strong V ds dependence 19

Off-state leakage: Temperature dependence L g = 500 nm, L ledge = 5 nm 300K 77K 150K -4 10 -4 -4 10 10 I d I d I d or I g (A/ m) I d -6 -6 -6 10 10 10 -8 -8 -8 10 10 10 V ds =0.1 to 0.6 V -10 I g -10 -10 10 10 10 I g I g -12 -12 -12 10 10 10 -14 -14 -14 10 10 10 -0.4 -0.2 0.0 0.2 -0.4 -0.2 0.0 0.2 -0.4 -0.2 0.0 0.2 V gs (V) V gs (V) V gs (V) • GIDL (gate-induced drain leakage) signature 20

Off-state leakage follows BTBT signature � � � � ���� ~ exp� � � � � �� -8 V ds =0.6 V 10 |I s | ( A/ m) V gs = -0.4 V -8 |I s | (A/ m) 10 V ds = 0.6 V -10 10 V ds = 0.5 V 300K -9 150K V ds = 0.4 V 10 77K T=77 K -12 10 0.44 0.48 0.52 1.0 1.2 1.4 -1 (V -1 ) 3/2 ( eV 3/2 ) V dg E g • I s follows BTBT dependence on V dg and E g 21

GIDL simulations TCAD simulation of BTBT rate based on nonlocal path BTBT model: n+ contact Gate InP Oxide InGaAs InAs S D InGaAs G InAlAs 2 nm E c BTBT E v 22

Conclusions • Novel self-aligned III-V QW-MOSFETs: – Lift-off free, wet-etch free, and Au free in front end process – Design and fabrication of critical S/D ledge – Tight metal contact spacing – Scaled channel thickness, barrier thickness and gate length • Record results demonstrated: – g m,max = 2.7 mS/ m in L ledge = 5 nm – I on = 410 A/ m in L ledge = 70 nm • Characteristic GIDL signature observed 23

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.