A mixed-signal ic for managing power in 5G applications IPSOC 2018 - PowerPoint PPT Presentation

A mixed-signal ic for managing power in 5G applications IPSOC 2018 Introduction Architecture of mixed-signal ics in handsets IPSOC 2018 2 MODEM architecture Protocol stack (RTOS) Transceiver soup letter TDMA, OFDM, CDMA

A mixed-signal ic for managing power in 5G applications IPSOC 2018

Introduction • Architecture of mixed-signal ic’s in handsets IPSOC 2018 2

MODEM architecture • Protocol stack (RTOS) • Transceiver soup letter TDMA, OFDM, CDMA IPSOC 2018 3

OFDM subcarriers interference Frequency Time IPSOC 2018 4

Power amplifier • “Unreasonable” requirements on RF transistor • Large Peak to Average Power ratio • Hard to predict subcarrier interference IPSOC 2018 5

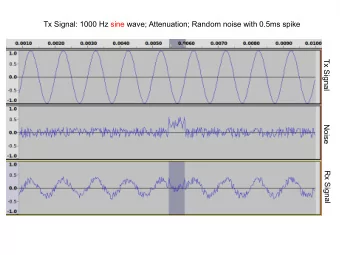

OFDM subcarriers interference • Temptation to use math (from dsplog.com) • PAPR is the maximum full scale signal power divided by the expected (average) power – PAPR of a single sine tone = 2 – PAPR of a single complex sinusoidal tone = 1 – Maximum expected PAPR from OFDM waveform with k subcarriers = k • Important result IPSOC 2018 6

PAPR mitigation approaches • Do nothing • Allow for worst-case high peak power • Drive signal saturation probability IPSOC 2018 7

Ideal high PAPR solution IPSOC 2018 8

Mixed-signal circuit to the rescue • Many approaches to PAPR mitigation include “detectors” • Power supply compliance has to be just 10% • Lead us not into temptation… Carrier frequency is GHz! IPSOC 2018 9

Open loop drive (Elastic Backoff™) IPSOC 2018 10

Charge-pump circuit (Dickson) • Each stage boosted by switching voltage • Simulation typically overestimates efficiency – 50% with integrated capacitors – > 80% with external capacitors IPSOC 2018 11

Actual charge-pump circuit IPSOC 2018 12

Charge-pump behavior I(Vdda) 4mA 2mA 0mA -2mA -4mA -6mA -8mA -10mA -12mA -14mA V(out) 7.0V 6.5V 6.0V 5.5V 5.0V 4.5V 4.0V 3.5V 3.0V 2.5V 2.0V V(charge-pump:phia_n) V(charge-pump:phib_n) 3.6V 3.2V 2.8V 2.4V 2.0V 1.6V 1.2V 0.8V 0.4V 0.0V -0.4V V(phia) V(phib) 4.0V 3.6V 3.2V 2.8V 2.4V 2.0V 1.6V 1.2V 0.8V 0.4V 0.0V 0ns 4ns 8ns 12ns 16ns 20ns 24ns 28ns 32ns 36ns IPSOC 2018 13

Load-line • Charge-pump is able to supply any current at a fixed voltage (up to the load maximum) • This is a “voltage” source • Linear regulation with a switching behavior IPSOC 2018 14

Conclusions • Complex analog/mixed-signal integration, but PV circuit blocks • Saves 30% power consumption with easy to integrate components • Semiconductor does not know if it’s analog or digital!!! IPSOC 2018 15

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.