1 SA-C Image Processing Support Cameron Project Objective Data - PowerPoint PPT Presentation

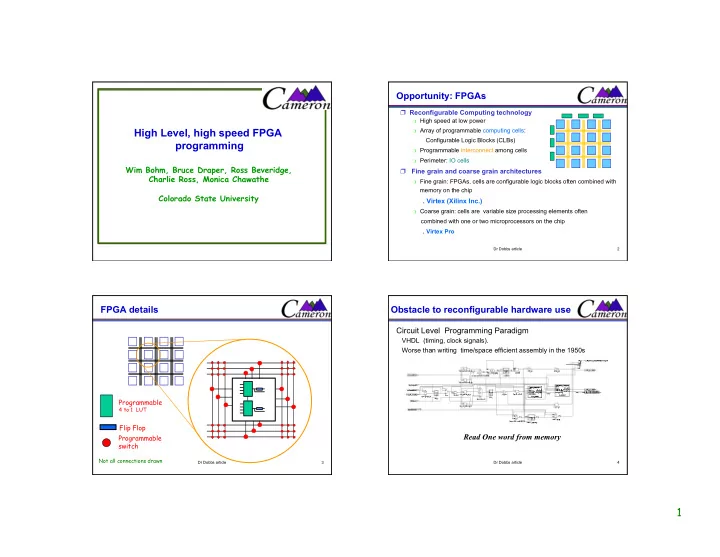

Opportunity: FPGAs Reconfigurable Computing technology High speed at low power High Level, high speed FPGA Array of programmable computing cells: Configurable Logic Blocks (CLBs) programming Programmable interconnect among cells

Opportunity: FPGAs Reconfigurable Computing technology High speed at low power High Level, high speed FPGA Array of programmable computing cells: Configurable Logic Blocks (CLBs) programming Programmable interconnect among cells Perimeter: IO cells Wim Bohm, Bruce Draper, Ross Beveridge, Fine grain and coarse grain architectures Charlie Ross, Monica Chawathe Fine grain: FPGAs, cells are configurable logic blocks often combined with memory on the chip Colorado State University . Virtex (Xilinx Inc.) Coarse grain: cells are variable size processing elements often combined with one or two microprocessors on the chip . Virtex Pro Dr Dobbs article 2 FPGA details Obstacle to reconfigurable hardware use Circuit Level Programming Paradigm VHDL (timing, clock signals). Worse than writing time/space efficient assembly in the 1950s Programmable 4 to 1 LUT Flip Flop Read One word from memory Programmable switch Not all connections drawn Dr Dobbs article 3 Dr Dobbs article 4 1

SA-C Image Processing Support Cameron Project Objective Data parallelism through tight coupling of loops and n-D arrays Provide a path from algorithms (not circuits) to FPGA hardware Loop header: structured parallel access of n-D array Via an algorithmic language: SA-C an extended subset of C for all elements • data flow graphs as intermediate representation for all slices (lower dimensional sub-arrays) • language support for Image Processing Approach or all windows (same dimensional sub-arrays) One Step Compilation to host and FPGA configuration codes Loop body: single assignment Automatic generation of host-board interface Easily detectable fine grain parallelism Compiler optimizations to improve traffic, circuit speed and area • loop/function body = data f;owgtraph If needed, optimizations are controlled by user pragmas Loop return: reduction or array construction Application Domain Image and Signal Processing Logic/arithmetic reductions: sum, product, and, or, max, min Concatenation and tiling Dr Dobbs article 5 Dr Dobbs article 6 SA-C Hardware Support Example: Prewitt int2 V[3,3] = {{-1, -1, -1}, Fine grain parallelism through Single Assignment { 0, 0, 0}, Function or Loop body is (equivalent to) a Data Flow Graph { 1, 1, 1}}; Loop header fetches data from local memory and fires it into loop body Image int2 H[3,3] = {{-1, 0, 1}, H W V Loop return collects data from body and writes it to local memory {-1, 0, 1}, {-1, 0, 1}}; Automatically pipelined for window W[3,3] in Image { Variable bit precision int16 x, int16 y = Integers: uint4, int5, int81 for h in H dot w in W dot v in V Fixed-points: fix16.4, fix80.30 return(sum(h*w), sum(v*w)); Automatically narrowed int8 mag = sqrt(x*x + y*y); Lookup tables (user pragma) } return( array(mag) ); Function as a look up table • automatically unfolded Array as a look up table Dr Dobbs article 7 Dr Dobbs article 8 2

Application performance summary Compiler Optimizations Summary of SA-C Applications Objectives Eliminate unnecessary computations Application WildStar Pentium III (800 Speed-up (Virtex2000E) MHZ) Re-use previous computations Reduce storage area on FPGA Probing 0.08 sec 65 sec (VC++) ~800x Reduce number of reconfigurations Prewitt Edge .0019 sec .1580 sec (Assm) ~80x Exploit locality of data: reduce data traffic Canny Edge .006 sec .135 (Assm) ~20x Improve clock rate .850 sec (VC++) ~120x CDF Wavelet .0020 sec .0770 sec (VC++) ~35x Standard optimizations ARAGTAP .0031 sec .067 sec (VC++) ~20x constant folding, operator strength reduction, dead code elimination, AddS (IPL) .00067 sec .00595 (Assm) ~8x invariant code motion, common sub-expression elimination. Dr Dobbs article 9 Dr Dobbs article 10 Initial optimizations Temporal CSE Size inference CSE eliminates redundancies by identifying spatially Propagate constant size information of arrays and loops down up,and sideways (dot products). common sub-expressions. Temporal CSE identifies common Full loop unrolling sub-expressions between loop iterations and replaces the Replace loop with fully unrolled, replicated loop bodies. Loop and array indices become constants. result by delay lines (registers). Reduces space. Array Value and constant Propagation Array references with constant indices are replaced by the array elements, and by constants if the array is constant. Loop fusion Even of loops with different extents F F F R R F Iterative (transitive closure) application of these optimizations replaces run-time execution with compile-time evaluation G G a lot like partial evaluation or symbolic execution Dr Dobbs article 11 Dr Dobbs article 12 3

Window Narrowing Window Compaction Another way of setting the stage for window narrowing, by After Temporal CSE, left columns of the window may not be moving window references rightward and using register delay referenced. Narrowing the window further reduces space. lines to move the inputs to the correct iteration. R R F R R F G F R G F G G Dr Dobbs article 13 Dr Dobbs article 14 Low level optimizations Application: Probing A probe is a point pair in a window of an image Array + Function Lookup Table conversion through Pragmas A probe set defines one silhouette of a vehicle Array Lookup conversion treats a SA-C array like a lookup table (automatically generated from a 3D model) Function Lookup conversion replaces an expression by a table lookup A vehicle is represented by 81 probe sets Bit-width narrowing (27 angles in an X,Y plane) x (3 angles in Z plane) Exploits the user defined bit-widths of variables to minimize We have 12 bit LADAR images of three vehicles: m60 Tank operator bit-widths. Used to save space. m113 Armored Personnel Carrier Pipelining m901 Armored Personnel Carrier + Missile Launcher Estimates the propagation delay of nodes and breaks A hit occurs when the pair straddles an edge: up the critical path in a user defined number of stages by one point is inside the object, the other is outside it inserting pipeline register bars. Used in all codes to increase Probing finds the best matching probe set in each window. frequency. The best match has largest ratio: count / probe-set-size. Dr Dobbs article 15 Dr Dobbs article 16 4

Still life with m113 Probing code structure Color image for each window in Image //return best score and its probe-set-index score, probe-set-index = for all probe-sets hit-count = for all probes in probe-set LADAR image return(sum(hit)) score = hit-count / probe-set-size return(max(score),probe-set-index) return(array(score),array(probe-set-index) Dr Dobbs article 17 Dr Dobbs article 18 Probing program flow Probing: the challenge Window Generator Thresholds Sum Trees & Ratios Max Trees Since every silhouette of every target needs its own probe set, Loop Body probing leads to a massive number of simple operations. Write Results In our test set, there are 243 probe sets, containing a total of 7573 probes. How do we optimize this for real-time operation on FPGAs? Dr Dobbs article 19 Dr Dobbs article 20 5

Spatial CSE in probing Probing and Optimizations for each window in Image Identify common probes across different probe sets and merge. for all probe-sets PS for all probes P in PS Probeset 1 compute score = (sum of hit(P)) / size(PS) identify P with maximum score The two inner for loops are fully unrolled, which turns them into a giant loop body (from 7573 inner loop bodies). This allows for: Probeset 2 Merged probe sets • Constant folding / array value propagation • Spatial Common Sub-expression Elimination • Temporal Common Sub-expression Elimination 12 probes 9 probes • Window Compaction probe common to the two probe sets Dr Dobbs article 21 Dr Dobbs article 22 Window Compaction in Probing Temporal CSE in Probing Identify probes that will be recomputed in next iterations, and replace them by delay lines of registers. Shifts all operations as far right as possible (earlier in time) Inserts 1-bit delay registers to Compute and Shift 3,5,and 7 bring result to proper temporal placement Sets the stage for window narrowing, removing 12 bit registers from circuit Shift 8 Shift 12 Shift 1 Dr Dobbs article 23 Dr Dobbs article 24 6

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.