1 Recall MIPS word size In hex 31 30 29 28 27 26 25 24 23 22 21 - PDF document

Stored program computer MIPS Memory Forms of Address (2 32 -1) . . . MIPS private regs PC (A+24) MIPS machine code and addressing IR (A+20) modes MIPS user regs (A+16) 0 0 0 0 $zero (A+12) $v0

Stored program computer MIPS Memory � Forms of Address (2 32 -1) � . . . MIPS private regs � PC � (A+24) � MIPS machine code and addressing IR � (A+20) � modes MIPS user regs � (A+16) � 0 0 0 0 $zero � (A+12) � $v0 � (A+8) � . . . (A+4) � $a0 � . . . (A) � $t0 � CS240 Computer Organization . . . Department of Computer Science $t1 � (12) � Wellesley College . $t2 � MIPS � (8) � . . . (4) � $s0 � (0) � $s1 � . . . Instruction, number, or string? CISC / RISC o The numeric form of a computer’s instruction set is know as its machine code. o Memory addresses can contain either integer data or instructions represented in numeric form. How do we tell them apart? 000000 � 10001 � 10010 � 01000 � 00000 � 100000 � � 32 bits or one word o MIPS machine code is a bit complicated, but not as complicated as Lucy’s. Machine code 7-3 Machine code 7-4 1 ¡

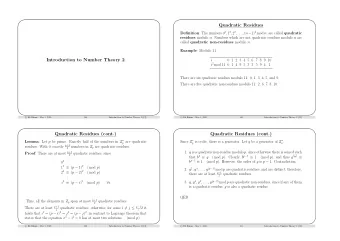

Recall MIPS word size In hex 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 � 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 � 0 0 0 0 � 0 0 0 0 � 0 0 0 0 � 0 0 0 0 � 0 0 0 0 � 0 0 0 0 � 0 0 0 0 � 1 0 1 1 � 0 0 1 0 � 1 0 0 1 � 1 0 1 1 � 0 1 1 0 � 0 0 0 0 � 0 0 0 0 � 0 0 0 0 � 1 0 1 1 � most most least least significant bit significant bit significant bit significant bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 � 29 � B6 � 00 � 0B � Machine code 7-5 Machine code 7-6 Machine code Assembling MIPS instructions The MIPS assemble language instruction What to do (operation code) add � $t0, $s1, $s2 � translates into the following machine code 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 � 0 0 0 0 0 0 � 0 0 1 0 1 0 1 1 1 1 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 � 000000 � 10001 � 10010 � 01000 � 00000 � 100000 � � 6 bits 5 bits 5 bits 5 bits 5 bits 6 bits What to do it with* 32 bits or one word *Well, more or less. Machine code 7-7 Machine code 7-8 2 ¡

MIPS instruction format* add $t0, $s1, $s2 instruction operation second register shift amount instruction operation second register shift amount or opcode source operand (coming soon) or opcode source operand (coming soon) � funct op � rs � rt � rd � shamt 000000 � 10001 � 10010 � 01000 � 00000 � 100000 � � 6 bits 5 bits 5 bits 5 bits 5 bits 6 bits 6 bits 5 bits 5 bits 5 bits 5 bits 6 bits first register register destination function code first register register destination function code source operand operand source operand operand *R-type (for register) or R-format. Machine code 2-9 Machine code 7-10 Design Principle 4. addi $t0, $s1, 1024* Good design demands good compromises instruction operation second register shift amount or opcode source operand (coming soon) op � rs � rt � constant or address � � 6 bits 5 bits 5 bits 16 bits 001000 � 10001 � � 01000 � 00000 � � 6 bits 5 bits 5 bits 5 bits 5 bits 6 bits still 32 bits first register register destination function code source operand operand *Doesn't fit! Machine code 7-11 Machine code 7-12 3 ¡

register 8 register 17 Oompa Loompa Doompadee Doo* addi $t0, $s1, 1024 op � rs � rt � constant or address � op � rs � rt � constant or address � � � 6 bits 5 bits 5 bits 16 bits 6 bits 5 bits 5 bits 16 bits instruction operation still 32 bits or opcode Exercise. First compile and then assemble A[200] = h + A[300], where we assume $t1 has the base address of A and $s2 corresponds 001000 � 10001 � 01000 � 0000 0100 0000 0000 � to h. � 6 bits 5 bits 5 bits 16 bits register first source immediate amount *Here’s where that green card in the front of your text comes in handy. destination register operand operand Machine code 7-13 Machine code 7-14 Dealing with larger constants addi $t0, $s1, 16711685 lui $t0, 255 # $t0 is register 8 op � rs � rt � constant or address � � 0000 0000 1111 1111 001111 00000 � 01000 � 6 bits 5 bits 5 bits 16 bits transfers 16-bit immediate constant register 8 0000 0000 1111 1111 0000 0000 0000 0000 still 32 bits fills lower 16 bits with zeros *But what about the lower 16-bits? Machine code 6-15 Machine code 7-16 4 ¡

OR immediate to the rescue addi $t0, $s1, 16711685 lui $t0, 255 # $t0 is register 8 o Finally, the newly constructed binary value of 16711685 is added to the contents of $s1 and stored in $t0. � 0000 0000 1111 1111 001111 00000 � 01000 lui � $t0, 255 � # $t0 is register 8 � transfers 16-bit ori � $t0, $t0, 5 � # or lower half with upper � immediate constant register 8 add � $t0, $t0, $s1 � # $t0 <- $s1 + 16711785 � o The original pseudoinstruction is translated into three actually 0000 0000 1111 1111 0000 0000 0000 0000 assembly language instructions at assemble time. OR of these two values goes into lower 16-bits of $t0 ori $t0, $t0, 5 � 0000 0000 0000 0101 001101 01000 � 01000 Machine code 7-17 Machine code 7-18 Hardware/Software interface J-type instruction format o The MIPS assembler j 1025 # goto location 1025 takes care of breaking large constants into pieces 000010 00 0000 0000 0000 0010 0000 0001 and then reassembling them into a register. o A special register, $at, is 6 bits 26 bits reserved for this task. op jump address Memory jump destination instruction : Program Counter (PC) 26-bit destination is concatenated with upper 4 bits of PC. Machine code 7-19 Machine code 7-20 5 ¡

Conditional branches are more limited Elementary my dear Watson o Conditional branches are bne $s0, $s1, address found in “loops” and in “if” statements, so they tend 000101 � 10000 � 10001 � address � to branch to a nearby � location. 6 bits 5 bits 5 bits 16 bits o Since the PC contains the address of the current location, we can branch to within 2 15 words of the still 32 bits current location using PC- relative addressing. Machine code 7-21 Machine code 7-22 PC-relative addressing Compare with base addressing bne $t0, $s5,Exit bne $t0, $s5,Exit op rs rt offset Memory op rs rt offset Memory branch destination instruction branch destination instruction Program Counter Program Counter lw $t0, 12($t1) op rs rt offset Memory word or byte operand base register Machine code 7-23 Machine code 7-24 6 ¡

Branching offsets in machine language This week’s puzzler o Suppose we are given a while (save[i] == k) � branch on register $s0 � i += 1; � being equal to register $s1: address op rs rt rd shamt funct � beq $s0, $s1, L1 Loop: sll $t1, $s3, 2 � 80000 � 0 0 19 9 2 0 � o Replace this by instruction add $t1, $t1, $s6 � 80004 � 0 9 22 9 0 32 � (s) that offers a much lw $t0, 0($t1) � 80008 � 35 9 8 0 � greater branching distance. bne $t0, $s5, Exit � 80012 � 5 8 21 2 � addi $s3, $s3, 1 � 80016 � 8 19 � 19 � 1 � j Loop � � 80020 � 2 20000 � � address or offset Exit: � � � � � Machine code 7-25 Machine code 7-26 The five MIPS addressing modes o It is sometimes necessary 1. Immediate addressing op rs rt Immediate (when reading a core dump for example) to reverse 2. Register addressing op rs rt rd . . . funct Registers engineer machine language Register into assembly. 3. Base addressing Memory op rs rt Address o What is the assembly + Register Byte Halfword Word language statement corresponding to 4. PC-relative addressing op rs rt Address Memory 00af8020? + Word PC 5. Pseudodirect addressing op Memory Address Word PC Machine code 7-27 7 ¡

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.