1 Target Model - Units Target Model Channel (1) Inside edge - PDF document

Outline RAMP: Architecture, Language RAMP Architecture & Compiler Target & Host Models RAMP Description Language http://ramp.eecs.berkeley.edu RDLC2 Toolflow Greg Gibeling, Andrew Schultz & Krste Asanovic FLEET

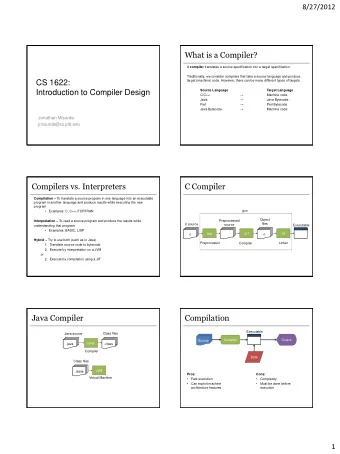

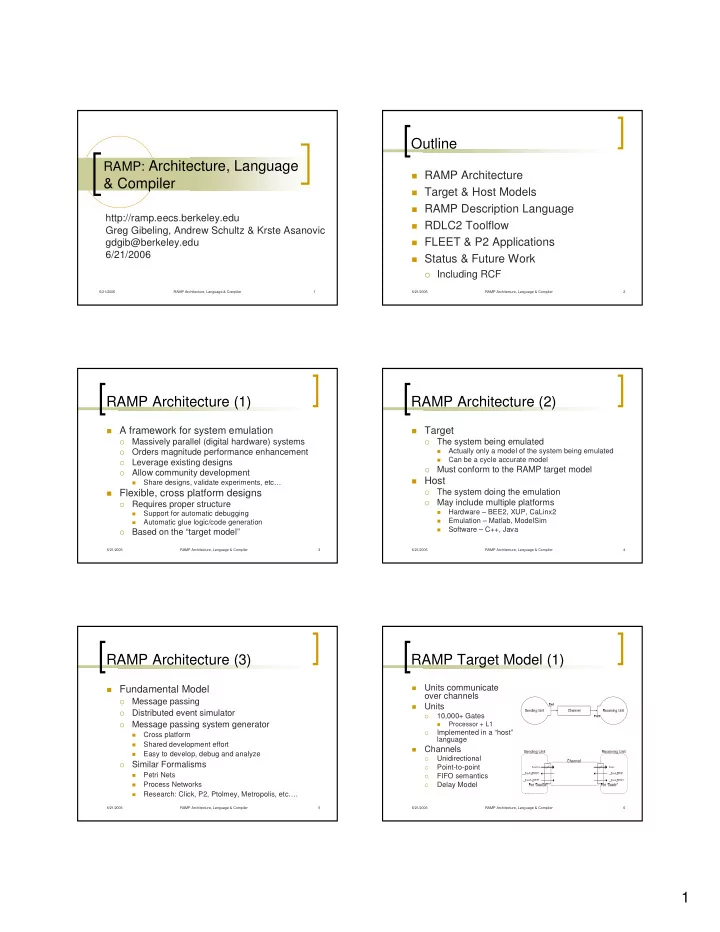

Outline RAMP: Architecture, Language � RAMP Architecture & Compiler � Target & Host Models � RAMP Description Language http://ramp.eecs.berkeley.edu � RDLC2 Toolflow Greg Gibeling, Andrew Schultz & Krste Asanovic � FLEET & P2 Applications gdgib@berkeley.edu 6/21/2006 � Status & Future Work � Including RCF 6/21/2006 RAMP Architecture, Language & Compiler 1 6/21/2006 RAMP Architecture, Language & Compiler 2 RAMP Architecture (1) RAMP Architecture (2) � A framework for system emulation � Target Massively parallel (digital hardware) systems The system being emulated � � Actually only a model of the system being emulated Orders magnitude performance enhancement � � � Can be a cycle accurate model Leverage existing designs � Must conform to the RAMP target model � Allow community development � � Host Share designs, validate experiments, etc… � � Flexible, cross platform designs The system doing the emulation � May include multiple platforms Requires proper structure � � Hardware – BEE2, XUP, CaLinx2 Support for automatic debugging � � Emulation – Matlab, ModelSim � Automatic glue logic/code generation � Software – C++, Java � Based on the “target model” � 6/21/2006 RAMP Architecture, Language & Compiler 3 6/21/2006 RAMP Architecture, Language & Compiler 4 RAMP Architecture (3) RAMP Target Model (1) Units communicate � Fundamental Model � over channels Message passing � Units � Distributed event simulator � 10,000+ Gates � Message passing system generator � � Processor + L1 Implemented in a “host” Cross platform � � language � Shared development effort Channels � � Easy to develop, debug and analyze Unidirectional � Similar Formalisms � Point-to-point � � Petri Nets FIFO semantics � � Process Networks Delay Model � Research: Click, P2, Ptolmey, Metropolis, etc…. � 6/21/2006 RAMP Architecture, Language & Compiler 5 6/21/2006 RAMP Architecture, Language & Compiler 6 1

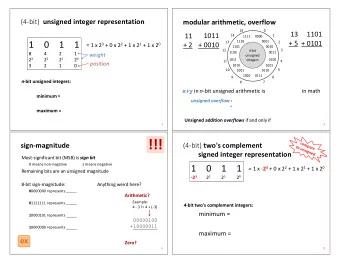

Target Model - Units Target Model – Channel (1) � Inside edge � Channel semantics Ports connect units � � Arbitrary message size to channels � The messages are statically typed FIFO signaling � � Hardware or � Ordered delivery Software � Debugging through monitoring & injection Target cycle control � __Start � � Provides for cross-platform simulations __Done � Allows for variable � timing, and timing accurate simulation 6/21/2006 RAMP Architecture, Language & Compiler 7 6/21/2006 RAMP Architecture, Language & Compiler 8 Target Model – Channel (2) Host Model Channel Params � Cross platform � #$���% �#�������&�'��� �� ���! Only used for timing �������� � Units implemented � accurate simulations ������������ ������������ in many languages ������ ������ Bitwidth � ����������� ����������� ��������� ��������� �������� Library units for I/O �������� �������� � Latency � ������ ����������� ������ Links implement � Buffering ����������� � ������ ������ ����������� ����������� ������ �� ���! channels � Fragments ����������� �"����� �����# �����" � Links ���������� ��������� Smaller than messages � ��.��� ��.��� #$���2���$�������$�� /0�1� 5�'&"' Convey the simulation #$���( �����4 � ����������� Any communication � �)��*+�'���,$�-� ��������1 �� ���! time through idles ������ �����3 ������1� ��� ��� ���������#� ����������� Less defined � ������������ 6/21/2006 RAMP Architecture, Language & Compiler 9 6/21/2006 RAMP Architecture, Language & Compiler 10 Host Model – Wrapper Host Model - Link Typically Three Components ������������ � Packing & Unpacking � 0�����.��$���$� Timing Model � �$���$��.�0����� "���������� Physical Transport � 660���� 66�$�� � Generated by RDLC2 plugins 5�-���7� ��,,��7� ������ ����*�����.� '�*�����.� ������ ��,,�� ���� 5�-��� '$���� '$���� 5�-���7� ��,,��7� ������ ����*�����.� '�*�����.� ������ '$���� '$���� ��,,�� 5�-��� "���������� ������� ������������ 6/21/2006 RAMP Architecture, Language & Compiler 11 6/21/2006 RAMP Architecture, Language & Compiler 12 2

RDL (1) RDL (2) � “RAMP Description Language” � Why RDL? General message passing system description � � Allows specification of partitioning language � Regular communication “Netlisting” language � � Enables cross platform system design Does NOT include leaf unit behavior � � RDL is a research enabler � Compiler is highly extensible � Ties together EXISTING designs Links � � Allows sharing of work & results Other toolflows � � Saves a lot of work External signals � � Complex interconnect is painful in HDLs Memories, etc… � 6/21/2006 RAMP Architecture, Language & Compiler 13 6/21/2006 RAMP Architecture, Language & Compiler 14 RDLC2 Toolflow (1) RDLC2 Toolflow (2) Help � rdlc2 –help � Explains � commands Includes all � the options GUI � rdlc2 –gui � 0����� �$���$��.� Easy to use � Includes error � �������� message display 6/21/2006 RAMP Architecture, Language & Compiler 15 6/21/2006 RAMP Architecture, Language & Compiler 16 FLEET Builder Application (1) P2/Overlog Application � FLEET � Overlay Networks /$����/$ ����� ���� 0����-������ ��$� A one instruction � Overlog (datalog) �� ���� � computer (Move) spec is compiled as Highly concurrent � in a DB query Location and � planner operation are tied Creates distributed initial codebag Accumulate { � Includes network � move (0) -> Adder.Adder; tuple processors 0��*��5$� 0��*����� )�8 builder move [] IntegerInput.Output �$������� We did a hardware -> Adder.Addend; � Includes assembler � move [] Adder.Sum -> �$������� implementation generator Display.Input, Adder.Adder; }; Includes an ASIP � 6/21/2006 RAMP Architecture, Language & Compiler 17 6/21/2006 RAMP Architecture, Language & Compiler 18 3

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.