Unit 13 Sequential Logic Constructs 13.2 Learning Outcomes I - PowerPoint PPT Presentation

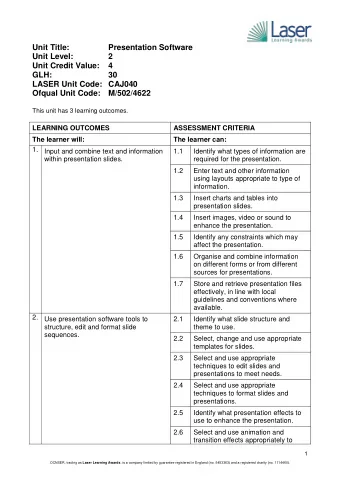

13.1 Unit 13 Sequential Logic Constructs 13.2 Learning Outcomes I understand the difference between level- sensitive and edge-sensitive I understand how to create an edge-triggered FF from 2 latches 13.3 How sequential building

13.1 Unit 13 Sequential Logic Constructs

13.2 Learning Outcomes • I understand the difference between level- sensitive and edge-sensitive • I understand how to create an edge-triggered FF from 2 latches

13.3 How sequential building blocks work BISTABLES, LATCHES, AND FLIP- FLOPS

13.4 Sequential Logic • Suppose we have a sequence of input numbers on X[3:0] that are entered over time that we want to sum up • Possible solution: Route the outputs ________________ so we can add the current sum to the input X A0 S0 A1 X[3:0] A2 Z[3:0] S1 9, 3, 2 14,5,2 A3 Adder B0 S2 B1 B2 S3 B3

13.5 Sequential Logic • Suppose we have a sequence of input numbers on X[3:0] that are entered over time that we want to sum up • Possible solution: Route the outputs back to the inputs so we can add the current sum to the input X • Problem 1: No way to Possible Solution _________________ X0 A0 S0 Z0 X1 A1 • Problem 2: Outputs can 9, 3, 2 X2 A2 S1 Z1 X3 A3 Adder _____________ to inputs and B0 S2 Z2 be added more than once B1 B2 S3 Z3 per input number B3 Outputs can feedback to inputs and update them sum more than once per input

13.6 Sequential Logic • Add logic at outputs to just capture and remember the new sum until we’re ready to input the next number in the sequence This logic should remember (i.e. sequential logic) the sum and only update it when the next number arrives X0 A0 S0 Z0 X1 A1 9, 3, 2 X2 A2 S1 Z1 X3 A3 Adder The data can still loop around and add up again B0 S2 Z2 (2+2=4) but if we just B1 hold our output = 2 then B2 S3 Z3 the feedback loop will be B3 broken We remember initial sum of 2 until input 3 arrives at which point we’d capture & remember the sum 5.

13.7 Sequence Adder • If X changes _____________ then Z should also change once per cycle • That is why we will use ___________________ to ensure the outputs can only update once per cycle Y0 Z0 X0 A0 S0 D Q X1 A1 CLR X2 A2 Y1 Z1 S1 D Q X3 A3 4-bit CLR Adder Y2 Z2 B0 S2 D Q B1 CLR Y3 Z3 B2 S3 D Q B3 CLR Clock Reset

13.8 Sequence Adder • The Reset (aka Clear) input on the FFs will cause Z to be initialized to 0, but then Z can’t change until the next positive edge • That means we will just keep adding 0 + 2 = 2 Y0 Z0 X0 A0 S0 D Q time X1 A1 2 CLR X2 A2 Y1 Z1 S1 D Q X3 A3 Clock 2 0 4-bit CLR Adder Y2 Z2 B0 S2 D Q Reset B1 CLR B2 Y3 Z3 0 S3 D Q B3 2 3 9 X CLR Clock Reset 2 Y Z 0

13.9 Sequence Adder • At the edge the flip-flops will sample the D inputs and then remember 2 until the next positive edge • That means we will just keep adding 3 + 2 = 5 Y0 Z0 X0 A0 S0 D Q time X1 A1 3 CLR X2 A2 Y1 Z1 S1 D Q X3 A3 Clock 5 2 4-bit CLR Adder Y2 Z2 B0 S2 D Q Reset B1 CLR B2 Y3 Z3 2 S3 D Q B3 2 3 9 X CLR Clock Reset 2 5 Y Z 0 2

13.10 Sequence Adder • Finally, at the positive edge the flip-flops will sample the D inputs and then remember 14 Y0 Z0 X0 A0 S0 D Q time X1 A1 CLR X2 A2 Y1 Z1 S1 D Q X3 A3 Clock 14 4-bit CLR Adder Y2 Z2 B0 S2 D Q Reset B1 CLR B2 Y3 Z3 S3 D Q B3 2 3 9 X CLR Clock Reset 2 5 14 Y Z 0 2 5 14

13.11 Sequential Logic • But how do flip-flops work? • Our first goal will be to design a circuit that can remember one bit of information • Easiest approach… • But how do you change the input? – A signal should only have one driver

13.12 D-Latches • The primary building block of sequential logic is a D-Latch • D-Latches (Data latches) store/remember/hold data when the clock is _______________ and ____ data when the clock is _______ (CLK=___) D-Latch Closed when CLK=1 D Q Q Closed when CLK CLK=0 These "switches" which can be closed or open are really transistors that can be on or off

13.13 Transparent & Hold Mode of D-Latches • The D-Latch operates in either Q ’ C D Q ____________ or ________ Q 0 ’ 0 x Q 0 mode based on the clock value 1 0 0 1 1 1 1 0 Function Table Description of D-Latch When Clock = 1 When Clock = 0 D D Q Q Q Q CLK CLK Transparent Mode Hold Mode (Q=D when CLK=1) (Q=Q 0 when CLK=0)

13.14 D-Latches Hold Mode Q ’ C D Q D Q Q 0 ’ Hold Mode 0 x Q 0 D Latch 1 0 0 1 Transparent Q’ C Mode 1 1 1 0 Triggering Rule: The Q output follow the D input D-LATCH (i.e. Q=D) when the clock or gate input is high (i.e. the latch is enabled). When the latch is disabled As clock is LOW, don’t 7475 (Clock = LOW) the output remains put. look at the D input D CLK Q 0 Complete 1 2 6 3 7 waveform for Q

13.15 D-Latches Hold Mode Q ’ C D Q D Q Q 0 ’ Hold Mode 0 x Q 0 D Latch 1 0 0 1 Transparent Q’ C Mode 1 1 1 0 When C=0, outputs don’t change no matter what the inputs do CLK D When C=1, Q outputs change based on inputs

13.16 Notation • To show that Q remembers its value we can put it in the past tense: – Q = Q 0 (Current Value of Q = Old Value of Q) • OR put it in the future tense – Q* = Q (Next Value of Q = Current Value of Q) Indicates “next - value” of Q Q ’ Q ’ * C D Q C D Q* Q 0 ’ Q ’ 0 x Q 0 0 x Q 1 0 0 1 1 0 0 1 1 1 1 0 1 1 1 0 Next Value = Current Value Current Value = Old Value

13.17 Adding a Sequence of Numbers • What if we put D-Latches at the outputs Y0 Z0 X0 A0 S0 D Q X1 A1 C X2 A2 Y1 Z1 S1 D Q X3 A3 Adder C Y2 Z2 B0 S2 D Q B1 C Y3 Z3 B2 S3 D Q B3 C Clock

13.18 Adding a Sequence of Numbers • We’ll change X on every clock period Y0 Z0 X0 A0 S0 D Q X1 A1 C X2 A2 Y1 Z1 S1 D Q X3 A3 Adder C Y2 Z2 Clock B0 S2 D Q B1 C X 2 3 Y3 Z3 B2 S3 D Q B3 C Clock When C=0 => Q* = Q When C=1 => Q* = D

13.19 Adding a Sequence of Numbers • Since the clock starts off low, the outputs of the latches can’t change and just hold at 0 Y0 Z0 X0 A0 S0 D Q X1 A1 C 2 X2 A2 Y1 Z1 time S1 D Q X3 A3 2 Adder C 0 Y2 Z2 Clock B0 S2 D Q B1 C X 2 3 Y3 Z3 B2 S3 D Q B3 C Y 2 Clock Z 0 When C=0 => Q* = Q When C=1 => Q* = D

13.20 Adding a Sequence of Numbers • When the clock goes high the D goes through to Q and is free to loop back around Y0 Z0 X0 A0 S0 D Q X1 A1 C 2 X2 A2 Y1 Z1 time S1 D Q X3 A3 Adder C 2 Y2 Z2 Clock B0 S2 D Q B1 C X 2 3 Y3 Z3 B2 S3 D Q B3 2 C Y 2 Clock Z 0 2 When C=0 => Q* = Q When C=1 => Q* = D

13.21 Adding a Sequence of Numbers • Once it loops back around it will be added again, change the Y value and go through to Z and loop back around again Y0 Z0 X0 A0 S0 D Q X1 A1 C 2 X2 A2 Y1 Z1 time S1 D Q X3 A3 Adder C 4 4 Y2 Z2 Clock B0 S2 D Q B1 C X 2 3 Y3 Z3 B2 S3 D Q B3 4 C Y 2 4 Clock Z 0 2 4 When C=0 => Q* = Q When C=1 => Q* = D

13.22 Adding a Sequence of Numbers • This feedback loop continues until the clock goes low again Y0 Z0 X0 A0 S0 D Q X1 A1 C 2 X2 A2 Y1 Z1 time S1 D Q X3 A3 Adder C 8 6 Y2 Z2 Clock B0 S2 D Q B1 C X 2 3 Y3 Z3 B2 S3 D Q B3 6 C Y 2 4 6 8 Clock Z 0 2 4 6 8 When C=0 => Q* = Q When C=1 => Q* = D

13.23 Adding a Sequence of Numbers • When the clock goes low again, the outputs will hold at their current value 8 until the clock goes high Y0 Z0 X0 A0 S0 D Q X1 A1 C 3 X2 A2 Y1 Z1 time S1 D Q X3 A3 Adder C 11 8 Y2 Z2 Clock B0 S2 D Q B1 C X 2 3 Y3 Z3 B2 S3 D Q B3 8 C Y 2 4 6 8 11 Clock Z 0 2 4 6 8 When C=0 => Q* = Q When C=1 => Q* = D

13.24 Adding a Sequence of Numbers • When the clock goes high, the outputs will be free to change and we will get the feedback problem Y0 Z0 X0 A0 S0 D Q X1 A1 C 3 X2 A2 Y1 Z1 time S1 D Q X3 A3 Adder C 11 8 Y2 Z2 Clock B0 S2 D Q B1 C X 2 3 Y3 Z3 B2 S3 D Q B3 8 C Y 2 4 6 8 11 14 17 20 Clock Z 0 2 4 6 8 11 14 17 20 When C=0 => Q* = Q When C=1 => Q* = D

13.25 Adding a Sequence of Numbers • Latches clearly don’t work • The goal should be to get one change of the outputs per clock period Y0 Z0 X0 A0 S0 D Q X1 A1 C 3 X2 A2 Y1 Z1 time S1 D Q X3 A3 Adder C 11 8 Y2 Z2 Clock B0 S2 D Q B1 C X 2 3 Y3 Z3 B2 S3 D Q B3 8 C Y 2 4 6 8 11 14 17 20 Clock Z 0 2 4 6 8 11 14 17 20 When C=0 => Q* = Q When C=1 => Q* = D

13.26 FLIP-FLOPS

13.27 Flip-Flops vs. Latches Flip-Flops Latches • Synchronous • Asynchronous • Clock Input • Clock/Enable input • Edge Sensitive • Level Sensitive – Outputs change – Action of the device is dependent only on the on the level of the clock positive – Outputs can change anytime (negative) edges Clock = 1 D Q D Q D-Latch D-FF Q Q CLK CLK

13.28 Flip-Flops • Change D Latches to D Flip-Flops D Q D Q D-FF D-Latch Q CLK Q C Triangle at clock input indicates edge- sensitive FF

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.