TOTEM experiment Online Software chain: the role of the firmware in - PowerPoint PPT Presentation

TOTEM experiment Online Software chain: the role of the firmware in the TOTEM Scientific Computation. F.S. Cafagna 1 , A. Fierkolski 2 , M. Quinto 1,2 , E. Radicioni 1,2 INFN Bari unit, CERN On behalf of TOTEM Collaboration TOTEM Physics goals

TOTEM experiment Online Software chain: the role of the firmware in the TOTEM Scientific Computation. F.S. Cafagna 1 , A. Fierkolski 2 , M. Quinto 1,2 , E. Radicioni 1,2 INFN Bari unit, CERN On behalf of TOTEM Collaboration

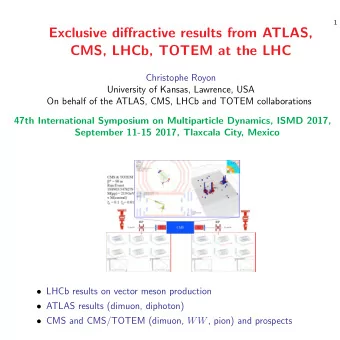

TOTEM Physics goals • TOTEM (TOTal cross section, Elastic scattering and diffraction dissociation Measurement at the LHC) pp with a precision ~ 1-2%, simultaneously measuring: • TOT • N el down to -t ~10 -3 GeV 2 • N inel with losses < 3% • Elastic pp scattering in the range 10 -3 < |t| ~ (p ) 2 < 10 GeV 2 • Soft diffraction (SD and DPE) • Particle flow in the forward region (cosmic ray MC validation/tuning) • TOTEM & CMS • Soft and hard diffraction in SD and DPE (production of jets, bosons, h.f.) • Central exclusive particle production • Low-x physics • Particle and energy flow in the forward region N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 2

TOTEM Experiment TOTEM N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 3

Experimental Setup @ IP5 Inelastic telescopes: charged particle & vertex reconstruction in inelastic events T1: 3.1 < < 4.7 T1: 18 – 90 mrad T2: 5.3 < < 6.5 T2: 3 – 10 mrad HF (CMS) IP5 ~ 10 m T1 CASTOR (CMS) ~ 14 m T2 T2 CMS + TOTEM unprecedented coverage Roman Pots: measure elastic & diffractive protons close to outgoing beam IP5 RP147 RP220 RP220 N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 4

TOTEM F.E. block scheme • VFAT is a 128 channel trigger and tracking front-end ASIC. • A total of 2120 VFATs (960 RP, 480 T2, 680 T1). For ~233000 channels. N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 5

Overview of the DAQ chain TOTEM VME based standalone DAQ Detector FEs CMS DAQ N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 6

The TOTFED • The TOTFED (TOTem Front End Driver) receives and handles data from the detectors and provide interfaces to local and global DAQs and trigger systems. • Modular and flexible in design, hosts: • 3 mezzanines for the OptoRX. • 1 mezzanine for an S-link64 TX card. • 1 mezzanine for a Front End Control (FEC) card. • A TTCrx chip to decode the TTC fast commands and the global clock (both optical and electrical interfaces). • VME64x (using 1 Altera’s Cyclone FPGA) and JTAG interfaces. • An interface to the Trigger Throttling System (TTS) • 4 Altera Stratix FPGA each connected to 18 MB of the SRAM memory and an USB2.0 port. • 3 FPGAs are connected to the OptoRX mezzanine via a 192bit bus. 64 bits of these 3 busses are connected to the 4 th . N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 7

The OptoRX • The Optical Link Interface (OptoRX), is equipped with an Altera Stratix II GX, embedded with high-speed serial transceivers rated to work up to 6.375 Gbps. • Up to 12 fibers can be connected for a total of 192 channels (up to 16 VFAT for fiber). • This FPGA embedded deserializers provide built-in functions compatible with the Gigabit Ethernet (8b/10b encoding) protocol used by the TOTEM FE optical transmitter: the GOL ASIC. • Hosts a mezzanine for a S-Link64 transmitter card • The OptoRX should: • receive and decode data from an optical link with speed of 800 Mbps; • build the events according to the CMS Common Data Format ; • support the local S-Link interface; • transmit data to the VME bus via the TOTFED board; • provide back pressure signals (TTS); • perform data quality checks; N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 8

The TOTFED block scheme Data Buses Control Buses VME32 Local Bus To OptoRx(es) Clock, Fast commands, TTC, TTS N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 9

The Opto-RX Synchronization blocks S-Link packets builder N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 10

The Opto-RX VFAT frame emulator DATA bus to MAIN or S-link mezanine using the same protocol Clock lock checks. Recovered at the end of run VME controled via MAIN control bus. Same Local Bus protocol N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 11

The OptoRX event builder Check fiber requested and active DATA bus to MAIN or S-link mezanine using the same protocol S-Link CRC check OptoRx event counter compared to the L1A received from TTCrx N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 12

The MAIN Trigger & OptoRX backpressure MAIN-OptoRX Data Bus MAIN-OptoRX TOTFED Local Bus Local Bus (VME) N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 13

The MAIN Data Bus from OptoRX VME polling register and Data FIFO status N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 14

The CMS S-Link Data Format N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 15

The Data Structure 4 fiber bundle Single fiber Data N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 16

Conclusion • TOTEM extends over 440 meters and its readout electronics should be interfaced to two different data acquisition system: VME and S- Link based. • Giving these requirements we designed the readout electronics firmware as a smart glue logic and flexible pipeline between the detector front-end electronics and the online and event builder software chain. This design implementation is able to sustain the requested average trigger rates of 1kHz, in the standalone VME TOTEM DAQ. • Event data fragments, acquired with widely different latencies, are synchronized and checked on board. In this way the online software can easily tag good events, ready for the track pattern recognition, increasing the efficiency of the offline software chain. • Thanks to the VFAT features and choosing the right fiber configuration, a raw pattern recognition and more refined data quality checks can be implemented in the firmware leveraging the FPGA resources available on the TOTFED and OptoRX cards. THANKS!!! N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 17

Spares N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 18

The VFAT Emulator N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 19

Interface to the TTCrx N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 20

VFAT VFAT Data structure VFAT Control logic N68-04 F.S. Cafagna, IEEE NSS, Knoxville TN, 4th November 2010 21

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.