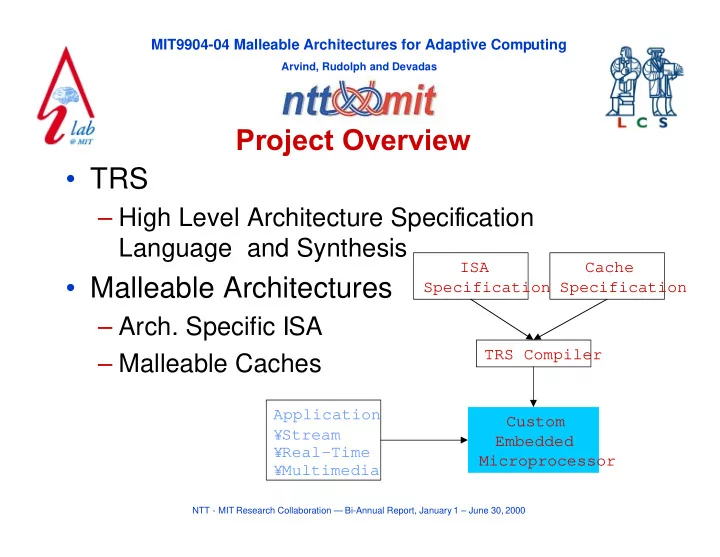

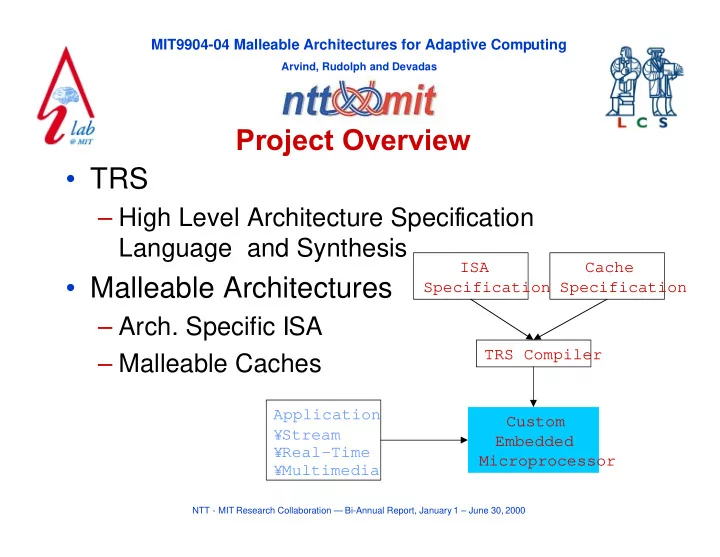

MIT9904-04 Malleable Architectures for Adaptive Computing Arvind, Rudolph and Devadas Project Overview • TRS – High Level Architecture Specification Language and Synthesis ISA Cache • Malleable Architectures Specification Specification – Arch. Specific ISA TRS Compiler – Malleable Caches Application Custom ¥Stream Embedded ¥Real-Time Microprocessor ¥Multimedia NTT - MIT Research Collaboration — Bi-Annual Report, January 1 – June 30, 2000

MIT9904-04 Malleable Architectures for Adaptive Computing Arvind, Rudolph and Devadas Progress Through June 2000 • Column Cache Implementation – Dedicated SRAM for embedded applications – Partitioned Cache for real-time applications • Adaptation Schemes for Multiprocessing • Curious Caching ISA w/ cache Column control inst. Cache – Initial Investigation TRS Compiler Application Custom ¥Stream Embedded ¥Real-Time Microprocessor ¥Multimedia NTT - MIT Research Collaboration — Bi-Annual Report, January 1 – June 30, 2000

MIT9904-04 Malleable Architectures for Adaptive Computing Arvind, Rudolph and Devadas Research Plan for the Next Six Months • Apply Technology to – Speech Processing (SLS) – Image Understanding • Analyze Other Apps ISA w/ cache Column control inst. Cache • Architectural Description TRS Compiler Application Custom ¥Stream Embedded ¥Real-Time Microprocessor ¥Multimedia NTT - MIT Research Collaboration — Bi-Annual Report, January 1 – June 30, 2000

Recommend

More recommend