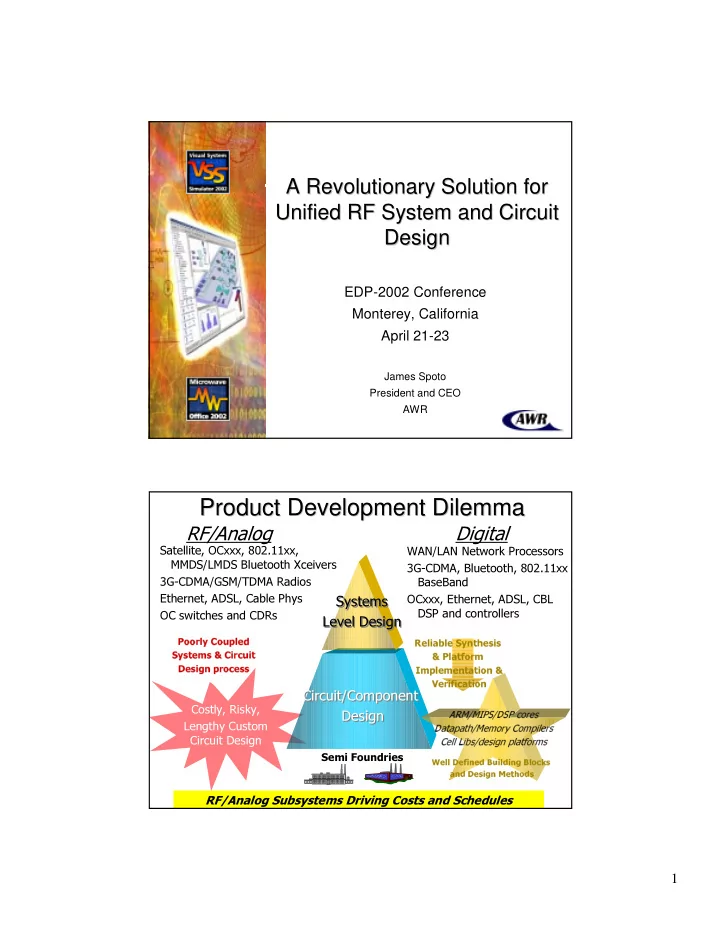

A Revolutionary Solution for A Revolutionary Solution for Unified RF System and Circuit Unified RF System and Circuit Design Design EDP-2002 Conference Monterey, California April 21-23 James Spoto President and CEO AWR Product Development Dilemma Product Development Dilemma ��������� ������� ���������������������������� �������������������������� ������������������� ��������� ����������������������������� ����������������������� �������� �������������������������� ������������������������������ ������� ������� ������������������� �������������������� ������������ ������������ 3RRUO\�&RXSOHG 5HOLDEOH�6\QWKHVLV� 6\VWHPV���&LUFXLW ��3ODWIRUP� 'HVLJQ�SURFHVV ,PSOHPHQWDWLRQ�� 9HULILFDWLRQ ������������������ ������������������ �������������� $50�0,36�'63�FRUHV ������ ������ 'DWDSDWK�0HPRU\�&RPSLOHUV ��������������� &HOO�/LEV�GHVLJQ�SODWIRUPV �������������� �������������� :HOO�'HILQHG�%XLOGLQJ�%ORFNV� DQG�'HVLJQ�0HWKRGV ������������������������������������������������ 1

������������������������������������� ������������ InP-pHEMT 200 SiGe BiCMOS T B H P n I Ft ~ 70GHz @ 0.35 � m >10 GHz 40 Gb/s GaAs-pHEMT SiGe BiCMOS Ft ~ 120GHz @ 0.18 � m T B H 100 a P G n I Si BiCMOS 80 F t (GHz) Ft ~ 30GHz @ 0.35 � m >4 GHz 10 Gb/s 60 Si CMOS 40 BiCMOS Ft ~ 15GHz @ 0.5 � m Ft ~ 25GHz @ 0.35 � m 2 GHz 2.5 Gb/s 20 S Ft ~ 35GHz @ 0.25 � m O M C Ft ~ 50GHz @ 0.18 � m 0.45 - 1 GHz InGaP HBT 10 Ft ~ 85GHz @ 1.0 � m 1.0 0.5 .35 .25 .18.15 .13 .1 Technology (µm) ��������������������������������������������� Design Platform Architecture Design Platform Architecture Application Specific IP and System Design Flow Application Specific IP and System Design Flow Application Specific IP and System Design Flow Block Arch & Parameterized Component Chip/Board Component Systems Footprint & Verification Descriptions Models Chip/MCM/PCB P&R Application Specific Circuit Design Flow Application Specific Circuit Design Flow Application Specific Circuit Design Flow Exploration, Design Capture Physical Final Design Optimization & Synthesis Design Verification & Analysis Foundry Kit Representations Foundry Kit Representations Foundry Kit Representations Symbols & Spice Models Device LVS, DRC, Component Interconnect & Generators & Ext Tech Files Descriptions Passive Models Layout Options Circuit DRC, LVS & Analog P&R Schematic Simulation & Extraction & Layout Capture Waveform Tools Editor Tool AWR EDA Platform 2

Application Specific Design Solutions Application Specific Design Solutions LMDS/ LMDS/ LMDS/ 802.11/ 802.11/ 802.11/ Wideband Wideband OCxxx Wideband OCxxx OCxxx �������� Satellite Satellite Satellite MMDS MMDS MMDS Bluetooth Bluetooth Bluetooth CDMA CDMA CDMA �� RF Optical Optical RF RF Optical Microwave MIMIC RF PCB RFIC Microwave Microwave MIMIC MIMIC RF PCB RF PCB RFIC RFIC ������� IC IC IC ��������� ��������� ������� RF CMOS InP InP InGaP InGaP SiGe SiGe RF CMOS RF CMOS InP InGaP SiGe ���� Circuit & IC Layout DRC, LVS & Design System & Extraction Capture & Simulation & Chip/PCB Tools ��� Synthesis Analysis P&R Interface AWR EDA Platform DB(PWR_SPEC[TP.MSIG,1024,5]) (dBm) IQ[TP.RCVR,100,1] System Diagram 1 BER System Diagram 1 Power Spectrums 1 50 DB(PWR_SPEC[TP.AMP,1024,5]) (dBm) IQ[TP.AMP,100,1] System Diagram 1 Constellations System Diagram 1 DB(PWR_SPEC[TP.CHNL,256,5]) (dBm) 20 System Diagram 1 TP .1 ID= MSIG 0 .01 10 -50 .001 .0001 BER[BER.3] 0 -100 MPSK_SRC QPSK ID= A1 QPSK_BERREF[BER.3,0,0] MOD= 8-PSK QPSK 1e-005 PWR= -24.3 dB 0 2 4 6 8 10 -150 PTYP= Avg. Power -10 -8e-006 -4e-006 0 4e-006 8e-006 NL_HB AWGN CTRFRQ= 0 MHz Frequency (MHz) ID= S1 ID= A2 CDNG= Binary NET= "High Power BJT Amp" PSD= -30 dB RCVR ID= A3 Systems Level -20 1 2 -20 -10 0 10 20 R D (Time Domain) 3 IQ 5 4 • Spec Synthesis TP ID= RCVR • Test Bench TP TP ID= AMP ID= CHNL Spectrum • Behavioral Model 20 Output Power (dBm) Voltage Gain 10 15 Delivered Input Power (dBm) • Characterization 10 Power (dBm) -10 Voltage Gain 5 Available Voltage G ain -30 0 DC VS ID= VC C1 -5 V= 3.97 V DCVS -50 ID= VB B1 0 20 40 60 80 98 -10 V= 0.93 V -30 0 30 Frequency (GHz) Power (dBm) Smith Chart Swp Max 1.0 I_MET ER I_ ME TER I_METER 8 . 7.3GHz ID=AMP3 ID=AMP4 ID=AMP5 0 3 0.6 PORT _PS1 LTU NER P= 1. DC 2.0 ID= TU1 DC Z= 50 Ohm Mag= 0.505 & RF 4 PS tar t= -40 dBm Ang= 170.3 Deg 1 RF 2 0 . 0 I_MET ER I_METER 2 C 3 . PS top= 10 dBm ID=AMP1 Zo= 50 Ohm ID=AMP2 3 PS tep= 1 d B PORT BIA STEE P= 2. 4.0 DC ID=X2 LTUNE R DC 1 Z= 50 Ohm 5.0 RF & ID = TU2 SU BCKT Mag= 0.255 0.2 2 RF 1 B ID= S1 Ang = 155 Deg 10.0 N ET= "BF G1981" Zo= 50 Oh m BIA STEE ID=X1 3 E V_ME TER V_METER V _METER ID =VM3 ID=V M4 ID =VM5 10.0 0.2 0.4 0.6 0.8 1.0 2.0 3.0 4.0 5.0 0 Circuit Level V_MET ER V_METER 0 ID=VM1 . 0 1 - ID=VM2 -0.2 -5.0 S[1,1] -4.0 -3.0 S[2,2] 4 . 0 - (Freq Domain) -2.0 -0.6 8 Swp Min 0 . -1.0 - 6.7GHz 3

A Unique Product Architecture A Unique Product Architecture Traditional AWR EDA System EDA Systems V A S = ID M 1 S W V P = R 0 A P D A J = -1 0 *lo g 1 0 ( _ Z 0 ) P S A B E = s w e e p ( s te p p -6 e d ( 0 ,-2 ) ) ,2 0 SRC MEAS P R W P B = S E A + P A D J Q M A R _ ID S 1 A C = M D O = 1 6 -Q M A O U T L V L P = W R d B O L V L T Y P S = ym o b E l n e r g y N S _ L A W G N P H S E A B E R ID = 5 C R T F R Q = 1 9 0 0 M H z ID = S 1 = A ID 3 ID = 4 A S W P A V R = B P S E A R T E A D _ = R A T E N E T = "A P M 9 0 1 0 S y m s te T e s s t" P S D = -4 9 + P A D J d B S H F T = 9 D 9 g e P S W P Y T = u A to ID Q 2 A M _ A = R X 1 R D 2 BER IQ 3 5 4 P T P T ID = 2 = ID 6 T P P T = ID 3 ID = 4 V A S M = ID 1 S W P V 0 R = A P D A = -1 J 0 *lo g ( 0 _ 1 ) 0 Z P S A B = E e s w p e ( s te p p e d ( -6 0 ,-2 0 ) ,2 ) Q A M R S _ C SRC MEAS P W R B P = S E A A + P D J ID 1 A = M D O 6 1 = -Q A M O U T L L V W = P B d R E R B Common O L V L Y T P ym = S b o l E n e g r y N L _ S W A G N P H E A S ID = 5 R C T Q R F 1 9 = 0 0 M H z = ID S 1 A ID = 3 ID = 4 A S W P V A R = P B A E S R T E A = D _ A T E R N E "A T = P M 9 1 0 S 0 y m te s T s e t" s P S D -4 = P + 9 J d D A B H S = T F D 9 9 g e Q A M _ R X S W P P Y T u = A to ID = A 2 1 R D 2 BER Database IQ 3 Netlists 5 4 T P T P = ID 2 = ID 6 P T P T = ID 3 ID = 4 Datafiles Robust Dependency Management Robust Dependency Management with Incremental Computation with Incremental Computation All dependency relationships Since objects can cache state, are managed in a uniform only objects that change will manner by the environment require updating 4

Recommend

More recommend