Phase-Noise and Amplitude-Noise Measurement of DACs and DDSs Claudio - PowerPoint PPT Presentation

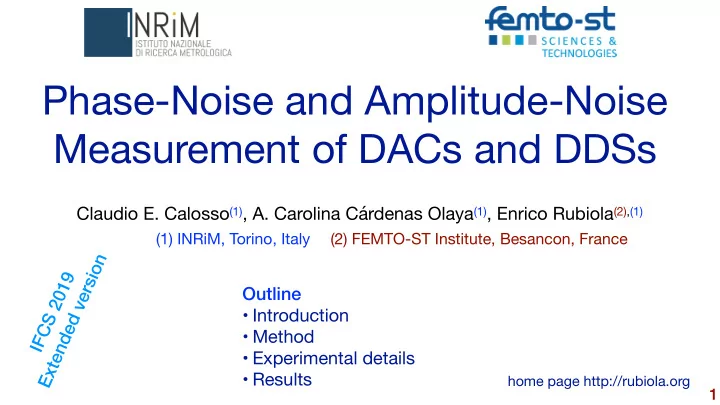

Phase-Noise and Amplitude-Noise Measurement of DACs and DDSs Claudio E. Calosso (1) , A. Carolina Crdenas Olaya (1) , Enrico Rubiola (2),(1) (1) INRiM, Torino, Italy (2) FEMTO-ST Institute, Besancon, France Extended version IFCS 2019 Outline

Phase-Noise and Amplitude-Noise Measurement of DACs and DDSs Claudio E. Calosso (1) , A. Carolina Cárdenas Olaya (1) , Enrico Rubiola (2),(1) (1) INRiM, Torino, Italy (2) FEMTO-ST Institute, Besancon, France Extended version IFCS 2019 Outline • Introduction • Method • Experimental details • Results home page http://rubiola.org � 1

� 2 Basic DDS Scheme n k = ( n k − 1 + N ) mod D integer: quantity digital analog z k = z k − 1 exp( j η ) complex: θ = 2 π n θ k = ( θ k − 1 + η ) mod 2 π phase: n state variable D z = e j θ assoc. complex LUT D = 2 m modulo 2 π output D-type ν s η = 2 π N register sin clock N increment DAC carry D ν 0 = N k , 0 , 1 , 2 , . . . t = k/ ν s time adder D ν s output freq. ν 0 = N cos clock freq. ν s D ν s DAC control N word = { z } The contents n of the m -bit register z plane is interpreted as a complex number z k High resolution z k − 1 < { z } D = 2 48 θ k ν s = 1 GHz k θ k − 1 < { z } time t = k/ ν c = { z } ∆ν = 3.55 µHz k

High-Speed DACs Have DDSs Inside � 3 AD9144 NCO gain quadrature DC offset t DACCLK If no internal NCO e e h SERDES s PLL a Q OUT3+ • Implement the NCO COMPLEX t MODULATION a HB1 HB2 HB3 d FSC OUT3– JESD 204 B INV SINC 4 Q-GAIN Q-OFFSET in FPGA 4 DACCLK PHASE PDP1 NCO MODE CONTROL I-GAIN I-OFFSET 1 ADJUST V TT 9 D f DAC I OUT2+ AND CLOCK FORMATTER A CLOCK DATA RECOVERY • The brute force of the ÷4, ÷8 HB1 HB2 HB3 SERDIN7± , FSC OUT2– s e c JESD204B su ffi ces i v e D Q COMPLEX OUT1+ MODULATION HB1 HB2 HB3 • IP NCOs available g SERDIN0± FSC o OUT1– INV SINC l Q-GAIN Q-OFFSET a PHASE PDP0 NCO DACCLK n MODE CONTROL I-GAIN I-OFFSET ADJUST A • Minimal NCO not I f DAC OUT0+ ÷4, ÷8 HB1 HB2 HB3 FSC PROTECT_OUT0 OUT0– di ffi cult to implement PROTECT_OUT1 SYNCOUT0+ SYNCHRONIZATION LOGIC SYNCOUT0– REF I120 SYNCOUT1+ AND CLOCK DISTRIBUTION BIAS AND SYNCOUT1– DAC CONTROL LOGIC CONFIG CLK_SEL ALIGN REGISTERS SYSREF+ DETECT SYSREF Rx SYSREF– PLL_CTRL CLK+ SERIAL POWER-ON DACCLK CLK I/O PORT RESET CLK– Rx PLL_LOCK DAC PLL IRQ SDIO SCLK TXEN0 TXEN1 11675-002 SDO CS RESET

The Beast to Kill � 4 Aka, the lowest noise we have seen in a DDS AD9915 L(ƒ), dBc (two DDSs) Y.Gruson Not a real challenge, but low enough to spend attention

Traditional Measurement Methods � 5 Saturated mixer PM-noise analyzer • Low output power, ≈ 0 dBm, the mixer takes ref 1 DAC NCO ≈ 10 dBm —> amplifier FFT analyzer τ 1 in τ c • Some commercial instruments have only one τ 2 input (FSWP , E5052A), ref 1 and ref 2 come ref 2 DAC NCO from internal synthesizers Fully digital PM-noise analyzer • DACs and DDSs have higher resolution and in DAC ADC NCO CORDIC clock frequency than ADCs FFT analyzer τ 1 ADC τ c • At least 100 averages for 10 dB noise rejection, ADC CORDIC τ 2 1000 for 15 dB ref ADC DAC NCO • How long does it take going down to ≤ 1 mHz? Cross-spectrum and averaging —> known problems Alternative?

� 6 Bridge (Interferometric) AN-PN Measurement alternate LO path Noisy signal v ( t ) = V 0 cos( ω t ) + x sin( ω t ) − y sin( ω t ) φ = x / V 0 α = y / V 0 Suppressed carrier ) 1 ( 0 7 9 9 I v Δ ( t ) = x sin( ω t ) − y sin( ω t ) S 9 R 1 n , l a a J & , 5 a 2 l o Synchronous detection 2 i - b 0 u 2 R 2 [ v Δ 2 cos( ω T )] * h lp = x • Suppress the carrier • Amplify and detect the noise sidebands [ v Δ 2 sin( ω T )] * h lp = y • PN results from (detected noise) / carrier Use the detected x and y to Rubiola & al, RSI 70(1) 220-225, Jan 1999 estimate AM and PM noise Also: Ivanov, IEEE T UFFC 45(6) 1526-1536, Nov 1998 Rubiola, RSI 73(6) 2445-2457, Jun 2002

� 7 Bridge (Interferometric) AN-PN Measurement alternate LO path Benefits • Lowest background noise • Amplifier NF —> white noise • No up-conversion of near-dc 1/ƒ with high carrier rejection ) 1 ( 0 • Low 50-60 Hz pickup due to 7 9 9 I S 9 R 1 Microwave gain before detection n , l a a J & • The noise in the LO arm is rejected , 5 a 2 l o 2 i (amplification allowed) - b 0 u 2 R 2 • No AM noise pickup, as in the • Suppress the carrier saturated mixer • Amplify and detect the noise sidebands • PN results from (detected noise) / carrier Annoying • Di ffi cult alignment Rubiola & al, RSI 70(1) 220-225, Jan 1999 Also: • Narrow band setup Ivanov, IEEE T UFFC 45(6) 1526-1536, Nov 1998 Rubiola, RSI 73(6) 2445-2457, Jun 2002

How Amplifier’s Flicker Works � 8 • No carrier u (t) v (t) noise-free • White noise only in the RF region AM PM amplifier input output • Flicker in the near DC region x (t) y (t) • No RF flicker near-dc noise • RF noise sidebands result from up- conversion Sv(f) internal • AM and PM noise ≈ independent of input (output) PSD noise up-conversion carrier power Su(f) (input) ν stopband passband stopband ν 0

Bridge with a Commercial Instrument? � 9 Saturated-mixer instruments Mixer • Only some give full access to the instrument mixer • Modern instruments use two channels and correlation • One channel cannot be used alone Digital instruments • Nope, extracting the phase requires a carrier

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.