Nachos Instructional OS: Part 2 CS 170, Tao Yang, Fall 2015 - PowerPoint PPT Presentation

Nachos Instructional OS: Part 2 CS 170, Tao Yang, Fall 2015 Announcement and update Project 1 deadline was extended. Project 2 description was revised last weekend. Start now or you miss deadline There are bonus points to submit and

Nachos Instructional OS: Part 2 CS 170, Tao Yang, Fall 2015

Announcement and update Project 1 deadline was extended. Project 2 description was revised last weekend. Start now or you miss deadline There are bonus points to submit and pass 1/3 of autograding by this Saturday. Midterm exam sample was given out. Exercise 1 will be updated in next few days. Some students still look for a partner… 5/14/2015 2

What to learn? How to execute a program in Nachos Produce binary MIPS code from a C program Execute this MIPS code in a tiny space Make a simple Nachos system call in a C program Project 2. Support the execution of multiple processes Support multiprogramming and memory protection with address translation using 1-level page table System calls for process execution. System calls for a simple file system interface. 5/14/2015 3

System Layers User process: User process: Binary code Binary code Nachos kernel threads Thread 1 Thread 2 Thread N Nachos OS modules (Threads mgm, File System, Code execution/memory mapping, System calls/Interrupt) MIPS Virtual Machine (Memory, Disk, Console) Base Operating System (Linux for our class)

Virtual Machine Layer under machine subdirectory. Approximates the MIPS architecture Rn page Machine SP table object PC memory registers Timer Can execute a sequence of MIPS instructions. 5/14/2015 5

Two modes of executions User mode: execute instructions which only access the user space. Kernel mode kernel executes when Nachos first starts up or when an instruction causes a trap illegal instruction, page fault system call Nachos layer 5/14/2015 6

Code execution steps in Nachos Load instructions into the machine's memory. Initialize registers (program counter, etc). Tell the machine to start executing instructions. The machine fetches the instruction, decodes it, and executes it. Repeat until all instructions are executed. Handle interrupt/page fault when needed User binary code Nachos Nachos execution layer MIPS Machine 5/14/2015 7

Machine Object: Implement a MIPS machine an instance created when Nachos starts up. Supported public variables: Registers: 40 registers. 4KB Memory: Byte-addressable. 32 pages (128Bytes) Virtual memory: use a single linear page table or a software-managed TLB. Rn page Machine SP table object PC memory 5/14/2015 8

Code/machine/machine.h class Machine { char *mainMemory; // physical memory to store user program, // code and data, while executing int registers[NumTotalRegs]; // CPU registers, for executing user programs TranslationEntry *pageTable; unsigned int pageTableSize; } Rn page Machine SP table object PC memory 5/14/2015 9

Machine Object: Supported operations Machine(bool debug);//allocate memory of 32 pages (128bytes per page). Initialize memory/register/ page table Translate(int virtAddr, int* physAddr, int size, bool writing); OneInstruction(); // Run one instruction of a user program. Run(); // Run a user program ReadRegister(int num); WriteRegister(int num, int value); ReadMem(int addr, int size, int* value); WriteMem(int addr, int size, int value); 5/14/2015 10

Code/machine/ipssim.cc void Machine::Run(){ Instruction *instr = new Instruction; // storage for decoded instruction interrupt->setStatus(UserMode); for (;;) { OneInstruction(instr); //fetch and execute one instruction interrupt->OneTick(); //advance clock } } 5/14/2015 11

Code/machine/machine.h class Instruction { public: void Decode(); // decode binary representation of instruction unsigned int value; // binary representation of the instruction unsigned char opCode; // Type of instruction unsigned char rs, rt, rd; // Three registers from instruction. int extra; // offset or other purpose. Treat as 0 }; 12

Code/machine/ipssim.cc Void Machine::OneInstruction(Instruction *instr) { //Fetch an instruction and then decode if (!machine->ReadMem(registers[PCReg], 4, &raw)) return; //if error, return instr->value = raw; instr->Decode(); // Execute the instruction switch (instr->opCode) { … case OP_ADDU: registers[instr->rd] = registers[instr->rs] + registers[instr->rt];break; case OP_SW: machine->WriteMem(registers[instr->rs], 4, registers[instr- >rt]); break; … case OP_SYSCALL: RaiseException(SyscallException, 0); return; … } // Advance program counters. registers[PCReg] = registers[NextPCReg]; registers[NextPCReg] = pcAfter; //which is registers[NextPCReg] + 4; 13 }

Code/machine/translate.cc bool Machine::WriteMem(int addr, int size, int value) { ExceptionType exception; int physicalAddress; exception = Translate(addr, &physicalAddress, size, TRUE);//address translation if (exception != NoException) { machine->RaiseException(exception, addr); return FALSE; } switch (size) { //Copy value to the target physical memory address properly case 1: machine->mainMemory[physicalAddress] = (unsigned char) (value & 0xff); break; case 2: *(unsigned short *) &machine->mainMemory[physicalAddress] = ShortToMachine((unsigned short) (value & 0xffff)); break; case 4: …. } } bool Machine::ReadMem(int addr, int size, int *value) { … 14 }

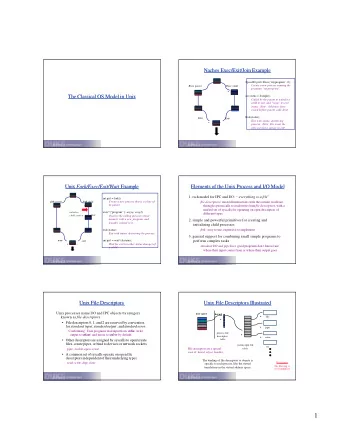

A Simple Page Table process page table PFN 0 PFN 1 Each process has its own page table. Virtual addresses are translated relative to PFN i the current page PFN i table. + offset page #i offset user virtual address physical memory page frames

Code/machine/translate.cc ExceptionType Machine:: Translate(int virtAddr, * physAddr, size, writing) { unsigned int vpn, offset; TranslationEntry *entry; unsigned int pageFrame; // calculate virtual page number, and offset within the page vpn = (unsigned) virtAddr / PageSize; offset = (unsigned) virtAddr % PageSize; entry = &pageTable[vpn]; Physical page use bit | dirty bit pageFrame = entry->physicalPage; entry->use = TRUE; // set the use, dirty bits if (writing) entry->dirty = TRUE; *physAddr = pageFrame * PageSize + offset; // compute physical address return NoException; } 16

Virtual Machine Layer Rn page SP table Machine object PC memory registers Timer Interrupt 5/14/2015 17

Interrupt Object Maintain an event queue with a simulated clock. Supported operations: Schedule(VoidFunctionPtr handler, int arg, int when, IntType type) Schedule a future event to take place at time ``when''. Usage: schedule a yield at random interval. SetLevel(IntStatus level). Used to temporarily disable and re-enable interrupts. Two levels are supported: IntOn and IntOff. OneTick() — advance 1 clock tick CheckIfDue(bool advanceClock). Examines if some event should be serviced. Idle(). ``advances'' to the clock to the time of the next scheduled event 5/14/2015 18

Interrupt::OneTick() Software managed clock. The clock advances 1 tick after one binary instruction execution with user mode , 10 with system mode after every restored interrupt (disable/enable Interrupt) or after the MIPS simulator executes one instruction. When the ready list is empty, fast-advance ticks until the next scheduled event happens. 5/14/2015 19

Timer object Generate interrupts at regular or random intervals Then Nachos invokes the predefined clock event handling procedure. Supported operation: Timer(VoidFunctionPtr timerHandler, int callArg, bool doRandom). Create a real-time clock that interrupts every TimerTicks (100) time units Or set this a random number for random mode nachos – rs 0 Setup a random timer that requests a thread yield 20

Console Object Simulates a character-oriented CRT device Data can be written to the device one character at a time through the PutChar() routine. Input characters arrive one-at-a-time. They can be retrieved by GetChar(). Supported operations: Console(char *readFile, char *writeFile, VoidFunctionPtr readAvail,VoidFunctionPtr writeDone, int callArg). Create a console instance.``readFile'' is the Unix file of where the data is to be read from; if NULL, standard input is assumed. PutChar(char ch) GetChar() 21

Disk Object Simulates the behavior of a real disk. The disk has only a single platter, with multiple tracks (32). Each track contains the same number of sectors (32). Allow only one pending operation at a time. Contain a ``track buffer'' cache. Immediately after seeking to a new track, the disk starts reading sectors, placing them in the track buffer. Supported operations: Disk(char *name, VoidFunctionPtr callWhenDone, int callArg) ReadRequest(int sectorNumber, char *data) WriteRequest(int sectorNumber, char *data) ComputeLatency(int newSector, bool writing) 5/14/2015 22

Executing a user program halt user space MIPS instructions executed data by the emulator ExceptionHandler() Nachos kernel MIPS emulator Machine::Run() fetch/execute SaveState/RestoreState examine/deposit examine/deposit Rn page process Machine SP table page object PC tables memory registers

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.