Lecture 8: Sequential Networks and Finite State Machines CK Cheng - PowerPoint PPT Presentation

CSE 140: Components and Design Techniques for Digital Systems Lecture 8: Sequential Networks and Finite State Machines CK Cheng Dept. of Computer Science and Engineering University of California, San Diego 1 Outlines Specification:

CSE 140: Components and Design Techniques for Digital Systems Lecture 8: Sequential Networks and Finite State Machines CK Cheng Dept. of Computer Science and Engineering University of California, San Diego 1

Outlines • Specification: Finite State Machine – State Table, State Diagram, Behavior • Implementation – Excitation Table – Mealy and Moore Machines – Examples 2

Sequential Networks Y D A B C X Combinational S(t) CLK CLK RTL: Register-Transfer Level Description CLK 1.Components F-Fs 2.Specification Conceptually, we can 3.Implementation: Excitation align all registers into one Table single column 3

Specification • Combinational Logic – Truth Table – Boolean Expression – Logic Diagram (No feedback loops) • Sequential Networks: – State Diagram, State Assignment, State Table – Excitation Table and Characteristic Expression – Logic Diagram (FFs and feedback loops) 4

N OT ALL S EQUENCES ARE CREATED EQUAL A coin has two faces. A toss of the coin lands either Head or Tail with equal probability. A series of tossing creates a sequence. Given two patterns, say HHH and HTT, the pattern appears first wins. A. The two patterns have an T H H H H H equal chance to win B. HHH wins more times C. HTT wins more times D. None of the above

N OT ALL S EQUENCES ARE CREATED EQUAL State Diagram of HHH H/1 H/0 H/0 H H S H T/0 T/0 T/0 Different diagrams yield different expectations State Diagram of HTT S H T T/0 T/1 H/0 T H/0 H/0 T/0

Implementation: Design Flow • Input Output Relation • State Diagram (Transition of states) – State minimization (Reduction) – Finite state machine partitioning • State Assignment (Map states into binary code) – Binary code, Gray encoding, One hot encoding, Coding optimization • State Table (Truth table of states) • Excitation Table (Truth table of FF inputs) – K Map, Minimal Expression – Logic Diagram 7

Implementation: Examples • Example 1: a circuit with D Flip Flops • Example 2: analysis of a sequential machine 8

State: What is it? Why do we need it? Behavior over time Symbol/ Circuit CLK time Free running 2 bit Counter Q 0 Q 1 What is the expected output of the counter over time? 9

Finite State Machines: Describing circuit behavior over time Diagram that depicts Symbol/ Circuit behavior over time 2 bit Counter 10

Implementing the 2 bit counter State Diagram State Table: Symbol S 0 Current state Next State S 0 S 1 S 3 S 1 S 1 S 2 S 2 S 3 S 3 S 0 S 2 State Assignment Q 1 (t) Q 0 (t) Q 1 (t+1) Q 0 (t+1) State Q 1 Q 0 S 0 0 0 S 1 0 1 S 2 1 0 S 3 1 1 State Table: Binary 11

Implementing the 2 bit counter S 0 Current state Next State S 0 S 1 S 1 S 3 S 1 S 2 S 2 S 3 S 3 S 0 S 2 Q 1 (t) Q 0 (t) Q 1 (t+1) Q 0 (t+1) State Diagram 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 State Table 12

State Table Q 1 (t) Q 0 (t) Q 1 (t+1) Q 0 (t+1) 0 0 0 1 D 0 (t) = Q 0 (t)’ D 1 (t) = Q 0 (t) Q 1 (t)’ + Q 0 (t)’ Q 1 (t) 0 1 1 0 1 0 1 1 1 1 0 0 Q 0 (t) Q D Combinational Q’ circuit Q 1 (t) Q D Q’ CLK Circuit with 2 flip flops 13

Q 1 (t) Q 0 (t) Q 1 (t+1) Q 0 (t+1) Truth table→K map→Switching function 0 0 0 1 Q 0 (t+1) = Q 0 (t)’ 0 1 1 0 Q 1 (t+1) = Q 0 (t) Q 1 (t)’ + Q 0 (t)’ Q 1 (t) 1 0 1 1 1 1 0 0 State Table Q We store the current state using D-flip D Q’ flops so that: Q 0 (t) • Inputs to the combinational circuit Q D don’t change while the next output is Q’ being computed • The transition to the next state only CLK occurs at the rising edge of the clock Q 1 (t) Implementation of 2-bit counter 14

Generalized Model of Sequential Circuits Y X S(t) CLK 15

Netlist State Table State Diagram Input Output Relation 1/1 PS\Input X=0 X=1 0/0 S0 S0,0 S2,0 0/1 S0 S1 S3 S1 S3,0 S3,0 S2 S2,0 S1,0 1/0 0, 1/0 S3 S1,1 S0,1 1/0 S2 Example: Output sequence 0/0 Time 0 1 2 3 4 5 Input 0 1 1 0 1 - State S0 Output 16

Netlist State Table State Diagram Input Output Relation 1/1 PS\Input X=0 X=1 0/0 S0 S0,0 S2,0 0/1 S0 S1 S3 S1 S3,0 S3,0 S2 S2,0 S1,0 1/0 0, 1/0 S3 S1,1 S0,1 1/0 S2 Example: Output sequence 0/0 Time 0 1 2 3 4 5 Input 0 1 1 0 1 - State S0 S0 S2 S1 S3 S0 Output 0 0 0 0 1 0 17

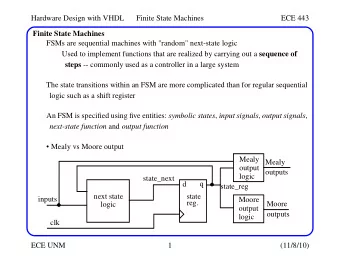

Implementation State Diagram => State Table => Logic Diagram • Canonical Form: Mealy and Moore Machines • Mealy machines: General • Moore machines: Output is independent of current input. • Excitation Table • Truth Table of the F-F Inputs • Boolean algebra, K-maps for combinational logic • Examples • Timing 18

Canonical Form: Mealy and Moore Machines x(t) y(t) Combinational Logic CLK x(t) C2 y(t) x(t) y(t) C1 C2 C1 CLK CLK 19

Canonical Form: Mealy and Moore Machines Mealy Machine: y i (t) = f i (X(t), S(t)) Moore Machine: y i (t) = f i (S(t)) s i (t+1) = g i (X(t), S(t)) x(t) x(t) y(t) C1 C2 y(t) C1 C2 CLK S(t) S(t) CLK Moore Machine Mealy Machine 20

Canonical Form: Mealy and Moore Machines Mealy Machine: y i (t) = f i (X(t), S(t)) Moore Machine: y i (t) = f i (S(t)) s i (t+1) = g i (X(t), S(t)) Mealy Machine Moore Machine x(t) x(t) y(t) C1 C2 y(t) C1 C2 CLK S(t) S(t) CLK Input Input PS NS Output PS NS, output input input/outpu t Si Sj Si S S Sj output output 21

Life on Mars? Mars rover has a binary input x. When it receives the input sequence x(t-2, t) = 001 from its life detection sensors, it means that the it has detected life on Mars and the output y(t) = 1, otherwise y(t) = 0 (no life on Mars ). Implement the Life-on-Mars Pattern Recognizer! 22

Mars Life Recognizer FSM Which of the following diagrams is a correct Mealy solution for the 001 pattern recognizer on the Mars rover? 1/1 A. 0/0 0/0 1/0 S0 S1 S2 0/0 1/0 0/0 B. 0/0 1/1 Input/output 1/0 S0 S1 S2 1/0 0/0 C. Both A and B are correct D. None of the above 23

Mars Life Recognizer FFs Mealy Machine Pattern Recognizer ‘001’ x(t) 1/0 1/1 y(t) C1 C2 0/0 0/0 S0 S1 S2 CLK S(t) 0/0 1/0 What does state table need to show to design controls of C1? A. next state S(t+1) vs. input x(t), and present state S(t) B. output y(t) vs. input x(t), and present state S(t) C. output y(t) vs. present state S(t) D. None of the above 24

State Diagram => State Table with State Assignment x(t) 1/1 y(t) C1 C2 0/0 0/0 S0 S1 S2 1/0 0/0 CLK S(t) 1/0 Mealy Machine State Assignment S(t)\x 0 1 S(t)\x 0 1 S0: 00 S0 S1,0 S0,0 00 01,0 00,0 S1: 01 01 10,0 00,0 S1 S2,0 S0,0 S2: 10 10 10,0 00,1 S2 S2,0 S0,1 Q 1 (t+1)Q 0 (t+1), y 25

State Diagram => State Table => Excitation Table => Circuit id Q 1 Q 0 x D 1 D 0 y Q 1 (t) Q 0 (t)\x 0 1 00 01,0 00,0 000 0 0 1 0 01 10,0 00,0 001 1 0 0 0 10 10,0 00,1 010 2 1 0 0 x(t) 011 3 0 0 0 4 100 1 0 0 y(t) C1 C2 101 5 0 0 1 CLK 110 6 S(t) Mealy Machine 111 7 26

State Diagram => State Table => Excitation Table => Circuit id Q 1 Q 0 x D 1 D 0 y Q 1 (t) Q 0 (t)\x 0 1 0 000 0 1 0 00 01,0 00,0 001 1 0 0 0 01 10,0 00,0 010 2 1 0 0 10 10,0 00,1 x(t) 011 3 0 0 0 100 4 1 0 0 y(t) C1 C2 5 101 0 0 1 CLK 110 6 S(t) Mealy Machine 111 7 iClicker: What to fill in rows 6 and 7 of excitation table? A. All 0s B. All 1s C. All Don’t Cares 27

State Diagram => State Table => Excitation Table => Circuit Q 0 id Q 1 Q 0 x D 1 D 0 y D 1 (t): 0 2 6 4 000 0 0 1 0 0 1 X 1 1 3 7 5 001 1 0 0 0 0 0 X 0 x(t) 010 2 1 0 0 Q 1 3 011 0 0 0 D 1 (t) = x’Q 0 + x’Q 1 100 4 1 0 0 D 0 (t)= Q’ 1 Q’ 0 x’ 101 5 0 0 1 y= Q 1 x 110 6 X X X 111 7 X X X 28

State Diagram => State Table => Excitation Table => Circuit Q’ 1 Q 0 D 0 Q Q’ 0 D x’ Q’ Q 1 y x’ D 1 Q D Q 0 Q’ Q 1 x x(t) y(t) C1 C2 D 1 (t) = x’Q 0 + x’Q 1 D 0 (t)= Q’ 1 Q’ 0 x’ CLK y= Q 1 x S(t) Mealy Machine 29

Moore FSM for the Mars Life Recognizer Which of the following diagrams is a correct Moore solution to the ‘001’ pattern recognizer? input/output 1/1 A. 0/0 0/0 1/0 S1 S0 S2 0/0 1/0 B. 1 0 1 1 S3 0 0 S2 S0 S1 1 0 input 0 0 1 0 output C. Both A and B are correct 30 D. None of the above

Moore Mars Life Recognizer: FF Input Specs Pattern Recognizer ‘001’ x(t) y(t) S(t) C1 C2 1 0 1 1 0 S3 0 S2 S0 S1 CLK 1 0 0 0 Moore Machine 1 0 What does state table need to show to design controls of C2? A.(current input x(t), current state S(t) vs. next state, S(t+1)) B.(current input, current state vs. current output y(t)) C.(current state vs. current output y(t) and next state) D.(current state vs. current output y(t) ) E.None of the above 31

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.