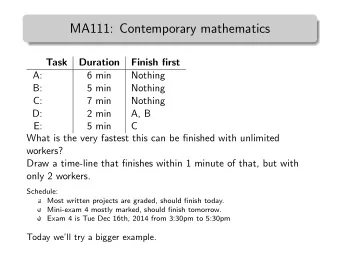

Lecture 10: Sequential Networks: Timing and Retiming CSE 140: - PowerPoint PPT Presentation

Lecture 10: Sequential Networks: Timing and Retiming CSE 140: Components and Design Techniques for Digital Systems Spring 2014 CK Cheng, Diba Mirza Dept. of Computer Science and Engineering University of California, San Diego 1 Timing

Lecture 10: Sequential Networks: Timing and Retiming CSE 140: Components and Design Techniques for Digital Systems Spring 2014 CK Cheng, Diba Mirza Dept. of Computer Science and Engineering University of California, San Diego 1

Timing • Clock specifies a precise time for the next state • Too late: fail to reach for the setup of the next state. • Too early: Race to disturb the holding of the next state. • Analysis: Verify the timing of the system. • Goal: A robust design. 2

Sequential Networks R1 R2 D B C A Combinational CLK1 CLK2 A typical sequential network has combinational circuit between registers (R1 to R2). The registers are synchronized by clocks (CLK1 to CLK2). Timing is set between clocks (CLK1 and CLK2). 3

B C A Combinational CLK1 CLK2 t cq + t comb + t setup ≤ T t hold < t cq + t comb 4

So far …. Combinational CLK

This lecture … Combinational CLK • When does our (seemingly logically correct) design go wrong? • How can we design a circuit that works under real constraints?

Timing Constraints of flip flops CLK Q D Q’ D t 1 time Q: What is the output of the flip flop at time t 1 ? A. One B. Zero C. Can’t say for sure 7

Timing Constraints of flip flops Q D Q’ D t 1 time What if the input transition happens late, close to the rising edge? A. Output will still be one at t 1 B. Output will be zero at t 1 C. Can’t say for sure 8

Input Timing Constraint: Set up time CLK Q D Q’ D t 1 time I. Setup time: t setup This is the time before the clock edge that data must be stable (i.e. not change) 9

Input Timing Constraint: Hold time CLK Q D Q’ D t 1 time I. Is it okay for the input to the flip flop to change right after the rising edge? 10

Input Constraints: Set up and hold time CLK Q D Q’ D t setup t hold I. Setup time: t setup t a Time before the clock edge that data must be stable (i.e. not change) II. Hold time: t hold Time after the clock edge that data must be stable Aperture time: t a Time around clock edge that data must be stable ( t a = t setup + t hold ) 11

Set up and hold time violations CLK Q D Q’ D t setup t hold I. Setup time violation t a This occurs if the input data signal does not remain unchanged for at least t setup before the clock edge. II. Hold time violation This occurs if the input data signal does not remain unchanged for at least t setup after the clock edge 12

Output Timing Constraints CLK Q D Q Q’ t ccq t pcq 13

Output Timing Constraints CLK Q D Q Q’ t ccq t pcq I. Contamination delay: t ccq Time after clock edge that Q might be unstable (i.e., start changing) II. Propagation delay: t pcq Time after clock edge that the output Q is guaranteed to be stable (i.e., to stop changing) 14

PIQ: A hold time violation is likely to occur when A. The input signal (into the flip flop) fails to change to a desired value fast enough B. The output signal (out of the flip flop) takes too long to stabilize C. The input signal (into the flip flop) does not remain stable long enough after the clock edge D. The output signal (out of the flip flop) changes too quickly 15

PIQ: The timing of which of the following signals can cause a setup-time violation? Q(t) T(t) Q T A. The input signal T(t) Q’ B. The output signal Q(t) C. The clock signal, CLK CLK D. Some of the above E. None of the above 16

PIQ: For a given flip-flop implementation which of its timing parameters can we modify when designing a sequential network (depicted below) A. Set up and hold time Combinational B. Propagation and Contamination delays CLK C. All of the above D. None of the above 17

Fact 1: Once a flip flop has been ‘built’ we are stuck with its timing characteristics: t setup , t hold, t ccq, t pcq Combinational CLK Now let’s look at the timing characteristics of the combinational part 18

Combinational Logic: Output timing constraints X 1 Y 1 Combinational X 2 Y 2 circuit X 3 Y 3 X 4 Y 4 I. Why don’t we have input constraints? 19

Combinational Logic: Output timing constraints X 1 Y 1 Combinational X 2 Y 2 circuit X 3 Y 3 X 4 Y 4 I. Contamination delay: t cd Minimum time from when an input changes until any output starts to change 20

Combinational Logic: Output timing constraints X 1 Y 1 Combinational X 2 Y 2 circuit X 3 Y 3 X 4 Y 4 I. Contamination delay: t cd Minimum time from when an input changes until any output starts to change II. Propagation delay: t pd Maximum time from when an input changes until the output or outputs of a combinational circuit are guaranteed to reach their final value (i.e., stop changing) 21

Combinational Logic: Output timing constraints A B Y C D PI Q: Which path in the above circuit determines the contamination delay of the circuit (assuming the delay of all the gates is the same)? A. AND- OR – NOR B. AND-OR C. NOR D. OR-NOR 22

Combinational Logic: Output timing constraints A B Y C D PI Q: Which path in the above circuit determines the propagation delay of the circuit (assuming the delay of all the gates is the same)? A. AND- OR – NOR B. AND-OR C. NOR D. OR-NOR 23

An alternate view of the sequential circuit Combinational CLK Q1 D2 D1 R1 R2 Combinational CLK CLK

The delay between registers has a minimum and maximum delay, dependent on the delays of the circuit elements (Dynamic Discipline) CLK CLK Q1 D2 C L R1 R2 (a) T c CLK Q1 D2 (b) 25

PI Q: Suppose input to R1 changed before t 1 , what is the maximum delay (from t 1 ) after which D2 reaches a stable value? CLK CLK A. Setup time of R1+ Q1 D2 Propagation delay of CL + C L Propagation delay of R2 B. Hold time of R1+ R1 R2 (a) Propagation delay of CL + t 1 T c setup time of R1 C. Propagation delay of R1+ CLK Propagation delay of CL + Propagation delay of R2 Q1 D. Propagation delay of R1+ Propagation delay of CL D2 E. Propagation delay of CL + (b) Propagation delay of R2 26

PI Q: Suppose input to R1 changed before t 1 , what is the minimum delay (from t 1 ) after which D2 starts to change? CLK CLK A. Setup time of R1+ Q1 D2 propagation delay of CL + C L propagation of R2 B. Hold time of R1+ R1 R2 (a) propagation time of CL T c +setup time of R1 C. Hold time of R1+ CLK Contamination delay of CL + Propagation time of R2 Q1 D. Contamination delay of R1+ Contamination delay of CL D2 E. Contamination delay of CL + (b) Contamination delay of R2 27

Setup Time Constraint • The setup time constraint depends on the maximum delay from register R1 through the combinational logic. • The input to register R2 must be stable at least t setup before the clock edge. CLK CLK Maximum delay, t max Q1 D2 C L = R1 R2 T c Setup Time Constraint: CLK Q1 D2 t pcq t pd t setup 28

Setup Time Constraint T c ≥ t pcq + t pd + t setup t pd ≤ T c – ( t pcq + t setup ) CLK CLK Q1 D2 C L R1 R2 T c CLK Q1 D2 t pcq t pd t setup 29

Hold Time Constraint • The hold time constraint depends on the minimum delay from register R1 through the combinational logic. • The input to register R2 must be stable for at least t hold after the clock edge. CLK CLK Q1 D2 C L Minimum delay, t min R1 R2 = CLK Hold Time Constraint: Q1 D2 t ccq t cd t hold 30

Hold Time Constraint t hold < t ccq + t cd t cd > t hold - t ccq CLK CLK Q1 D2 C L R1 R2 CLK Q1 D2 t ccq t cd t hold 31

Timing Analysis Timing Characteristics CLK CLK t ccq = 30 ps A t pcq = 50 ps B t setup = 60 ps X' X C t hold = 70 ps Y' Y D t pd = 35 ps t pd = t cd = 25 ps t cd = Hold time constraint: Setup time constraint: t ccq + t cd > t hold ? T c ≥ f c = 1/ T c = 32

Timing Analysis Timing Characteristics CLK CLK t ccq = 30 ps A t pcq = 50 ps B t setup = 60 ps X' X C t hold = 70 ps Y' Y D t pd = 35 ps t pd = 3 x 35 ps = 105 ps t cd = 25 ps t cd = 25 ps Setup time constraint: Hold time constraint: T c ≥ (50 + 105 + 60) ps = 215 ps t ccq + t cd > t hold ? f c = 1/ T c = 4.65 GHz (30 + 25) ps > 70 ps ? No! 33

Fixing Hold Time Violation Timing Characteristics Add buffers to the short paths: t ccq = 30 ps CLK CLK t pcq = 50 ps A t setup = 60 ps B t hold = 70 ps X' X C Y' Y D t pd = 35 ps t pd = t cd = 25 ps t cd = Hold time constraint: Setup time constraint: t ccq + t cd > t hold ? T c ≥ f c = 34

Fixing Hold Time Violation Add buffers to the short paths: Timing Characteristics t ccq = 30 ps CLK CLK A t pcq = 50 ps B t setup = 60 ps X' X t hold = 70 ps C Y' Y D t pd = 35 ps t pd = 3 x 35 ps = 105 ps t cd = 25 ps t cd = 2 x 25 ps = 50 ps Setup time constraint: Hold time constraint: T c ≥ (50 + 105 + 60) ps = 215 ps t ccq + t cd > t hold ? f c = 1/ T c = 4.65 GHz (30 + 50) ps > 70 ps ? Yes! 35

Clock Skew delay CLK CLK1 CLK2 Q1 D2 C L R1 R2 t skew CLK1 CLK2 CLK • The clock doesn’t arrive at all registers at the same time • Skew is the difference between two clock edges • Examine the worst case to guarantee that the dynamic discipline is not violated for any register – many registers in a system! 36

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.