I/O Bus and Interface Data Bus Addr Bus CPU Control Interface - PDF document

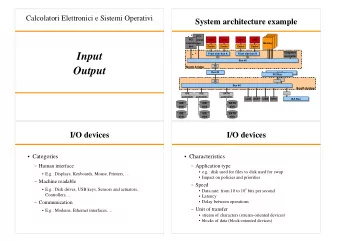

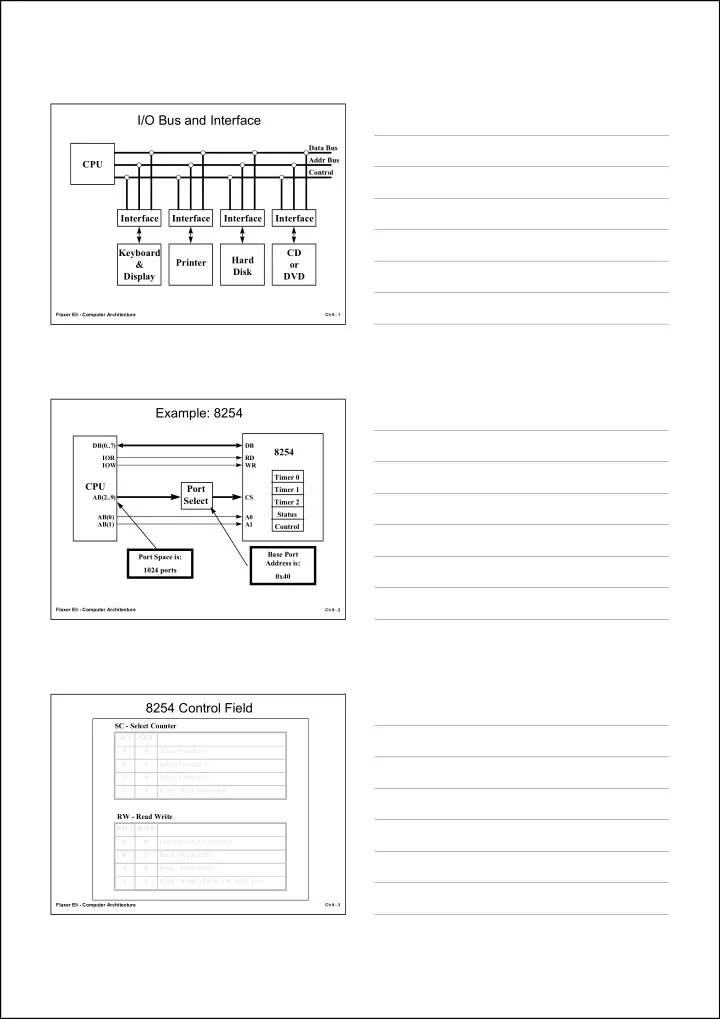

I/O Bus and Interface Data Bus Addr Bus CPU Control Interface Interface Interface Interface Keyboard CD Hard Printer & or Disk Display DVD Flaxer Eli - Computer Architecture Ch 8 - 1 Example: 8254 DB(0..7) DB 8254 IOR RD

I/O Bus and Interface Data Bus Addr Bus CPU Control Interface Interface Interface Interface Keyboard CD Hard Printer & or Disk Display DVD Flaxer Eli - Computer Architecture Ch 8 - 1 Example: 8254 DB(0..7) DB 8254 IOR RD IOW WR Timer 0 CPU Port Timer 1 AB(2..9) CS Select Timer 2 Status AB(0) A0 AB(1) A1 Control Base Port Port Space is: Address is: 1024 ports 0x40 Flaxer Eli - Computer Architecture Ch 8 - 2 8254 Control Field SC - Select Counter SC1 SC0 Select Counter 0 0 0 Select Counter 1 0 1 1 0 Select Counter 2 1 1 Read - Back Command RW - Read Write RW1 RW0 0 0 Counter Latch Command 0 1 Read / Write LSB 1 0 Read / Write MSB 1 1 Read / Write LSB first & MSB after Flaxer Eli - Computer Architecture Ch 8 - 3

8254 Control Field M - Mode M2 M1 M0 0 0 0 Mode 0 0 0 1 Mode 1 0 1 0 Mode 2 0 1 1 Mode 3 1 0 0 Mode 4 1 0 1 Mode 5 BCD - Binary Code Decimal BCD 0 Binary Counter 16 Bit 1 BCD Counter 4 Digit Flaxer Eli - Computer Architecture Ch 8 - 4 Hardware Interrupt Procedure Peripheral CPU Interrupt Number Device DB DB INT INT INTA INTA Interrupt Absolute Opcode Jump Address Vector Address (Method 1) (Method 2) 0 0 Jmp Sub0 Addess of Sub0 1 1 Ret Addess of Ret Code 2 2 Jmp Sub2 Addess of Sub2 * * Ret Addess of Ret Code * * Ret Addess of Ret Code 15 15 Ret Addess of Ret Code Flaxer Eli - Computer Architecture Ch 8 - 5 Multi Interrupts Procedure PIC Device 0 CPU IRQ0 INT DB DB IRQ1 INTA INT INT IRQ2 INTA INTA Device 1 IRQ3 INT INTA Device 2 INT INTA Device 3 INT INTA Flaxer Eli - Computer Architecture Ch 8 - 6

PIC 82C59 Flaxer Eli - Computer Architecture Ch 8 - 7 DMA Controller Address Bus Address Buffers Data Bus Data Bus Buffers Internal Bus Address Register RD WR Count Register CS Control Reg Select RS Logic Control Register Bus Request BR Bus Grant BG DMAR DMA Request To I/O Device Interrupt INTR DMAA DMA Ack Flaxer Eli - Computer Architecture Ch 8 - 8 DMA Transfer Flaxer Eli - Computer Architecture Ch 8 - 9

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.