GEOMETRIC STEINER TREE PACKING WITH DENSITY CONSTRAINTS Nicolai - PowerPoint PPT Presentation

GEOMETRIC STEINER TREE PACKING WITH DENSITY CONSTRAINTS Nicolai Hhnle, Pietro Saccardi Aussois Combinatorial Optimization Workshop January 12, 2017 Research Institute for Discrete Mathematics, Bonn 1/30 OVERVIEW Motivation: global routing

GEOMETRIC STEINER TREE PACKING WITH DENSITY CONSTRAINTS Nicolai Hähnle, Pietro Saccardi Aussois Combinatorial Optimization Workshop January 12, 2017 Research Institute for Discrete Mathematics, Bonn 1/30

OVERVIEW Motivation: global routing in chip design Traditional Steiner tree packing in grid graphs Geomtric Steiner tree packing on rhomboids Shortest paths and Steiner trees on rhomboids Experimental results 2/30

MOTIVATION: GLOBAL ROUTING IN CHIP DESIGN

HOW IS A CHIP BUILT? “Zoom Into a Microchip” by NISENet, available under a CC BY license. 4/30

HOW IS A CHIP BUILT? “Zoom Into a Microchip” by NISENet, available under a CC BY license. 4/30

HOW IS A CHIP BUILT? “Zoom Into a Microchip” by NISENet, available under a CC BY license. 4/30

HOW IS A CHIP BUILT? “Zoom Into a Microchip” by NISENet, available under a CC BY license. 4/30

HOW IS A CHIP BUILT? “Zoom Into a Microchip” by NISENet, available under a CC BY license. 4/30

HOW IS A CHIP BUILT? “Zoom Into a Microchip” by NISENet, available under a CC BY license. 4/30

HOW IS A CHIP BUILT? “Zoom Into a Microchip” by NISENet, available under a CC BY license. 4/30

HOW IS A CHIP BUILT? “Zoom Into a Microchip” by NISENet, available under a CC BY license. 4/30

HOW IS A CHIP BUILT? “Zoom Into a Microchip” by NISENet, available under a CC BY license. 4/30

HOW IS A CHIP BUILT? “Zoom Into a Microchip” by NISENet, available under a CC BY license. 4/30

HOW IS A CHIP BUILT? “Zoom Into a Microchip” by NISENet, available under a CC BY license. 4/30

WIRE DENSITY IS EXTREMELY HIGH Only signal wires are shown (power grid is omitted). Wires are colored by routing layer. 5/30 Tightly packed wires on a chip routed by BonnRoute; zoom is 1000 × .

FACTS AND FIGURES Chip structure • A chip has a layered 3D structure. • Transistors are placed on the lowest layers. • Up to 16 routing layers for interconnects. Chip size • several billions transistors 6/30 A chip with an area of few mm 2 packs: • several meters of wires (few nm thick) • several millions of connections

ROUTING IN CHIP DESIGN Assumptions • The chip functionality is decomposed into elementary Boolean operations. • All the connections (nets) between logic gates are known. Goal Compute connections for each net in such a way that: • different nets are disjoint; • design constraints are satisfied; • timing closure is achieved; • various objectives (wire length, power consumption, yield, …) are optimized. 7/30 • Logic gates (Boolean operations) are implemented at a transistor level. • All the logic gates are already placed on the chip.

ROUTING IN CHIP DESIGN Assumptions • The chip functionality is decomposed into elementary Boolean operations. • Logic gates (Boolean operations) are implemented at a transistor level. • All the logic gates are already placed on the chip. • All the connections (nets) between logic gates are known. Goal Compute connections for each net in such a way that: • various objectives (wire length, power consumption, yield, …) are optimized. 7/30 • different nets are disjoint; • design constraints are satisfied; • timing closure is achieved;

10 9 vertices! • Problem in split into global and detailed: MODELING ROUTING Constraints due to fabrication process Constraints due to problem hardness Huge restriction on wiring Steiner tree problem in 3D grid graphs • Axis-parallel wires. • Monodirectional layers. • Possible wire locations are discretized (tracks). • Global routing ignores disjointness and design rules compliancy. It optimizes globally objectives such as packing density, length and yield. • Detailed routing explores a subset of the routing graph. It handles disjointness and design rules compliancy. 8/30

MODELING ROUTING Constraints due to fabrication process Constraints due to problem hardness Huge restriction on wiring Steiner tree problem in 3D grid graphs 8/30 10 9 vertices!

MODELING ROUTING Constraints due to fabrication process Constraints due to problem hardness Huge restriction on wiring Steiner tree problem in 3D grid graphs • Axis-parallel wires. • Monodirectional layers. • Possible wire locations are discretized (tracks). • Problem in split into global and detailed: It optimizes globally objectives such as packing density, length and yield. • Detailed routing explores a subset of the routing graph. It handles disjointness and design rules compliancy. 8/30 10 9 vertices! • Global routing ignores disjointness and design rules compliancy.

TRADITIONAL STEINER TREE PACKING IN GRID GRAPHS

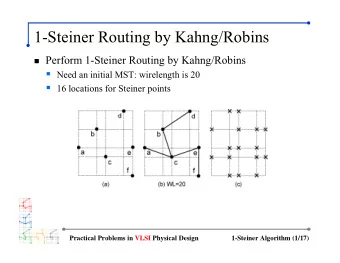

TRADITIONAL APPROACH TO GLOBAL ROUTING 10/30 Coarsening the routing graph → global routing graph.

TRADITIONAL APPROACH TO GLOBAL ROUTING 10/30 Coarsening the routing graph → global routing graph.

TRADITIONAL APPROACH TO GLOBAL ROUTING Task: Find Steiner trees Y n , minimizing 10/30 Problem (Simplified Global Routing) Coarsening the routing graph → global routing graph. Input: Graph G ′ , capacities u : E ( G ′ ) → Z ≥ 0 , lengths l : E ( G ′ ) → R ≥ 0 , nets N , where n ∈ N is ∅ ̸ = n ⊂ V ( G ′ ) , and wire widths w : N × E ( G ′ ) → R ≥ 0 . ∑ ∑ l ( e ) n ∈N e ∈ E ( Y n ) and meeting the capacity constraints: ∑ w ( n , e ) ≤ u ( e ) , ∀ e ∈ E ( Y n ) . n ∈N : e ∈ E ( Y n )

MIN-MAX RESOURCE SHARING Problem (Min-Max Resource Sharing) max 11/30 Input: • R finite set of resources (edges) of finite capacity • C finite set of customers (nets) • B c set of solutions for c ∈ C (Steiner trees) • Resource consumption function usg c : B c → R R ≥ 0 • σ -approximate oracle function f c : R R ≥ 0 → B c Task: Find b c attaining � { } � λ ∗ := inf ∑ � b c ∈ B c , c ∈ C ( usg c ( b c )) r . � � r ∈R c ∈C

ALGORITHM OUTLINE: MIN-MAX RESOURCE SHARING • It maintains resource prices (initially set to 1). • The algorithm proceeds in phases. In each phase: • Return convex combination of Steiner trees for each net. Theorem (D. Müller, K. Radke, J. Vygen, 2011) IP techniques [T. H. Wu, A. Davoodi, and J. T. Linderoth, 2011] could be used but are inpractical for our instances. 12/30 • For every net, find (approx.) cheapest route w.r.t. the given resource prices. • Update the price of the used resources grow multiplicatively with load. Let ω > 0 . A σ ( 1 + ω ) -approximate fractional solution can be computed in time O ( θ log |R| ( |C| + |R| )( log log |R| + ω − 2 )) , where θ is the time for an oracle call.

POTENTIAL DRAWBACKS • Poor topologies. 13/30 • Does not connect to pin shapes (important for signal delay estimation). • Depends heavily on the choice of the grid. • Does not support input wires.

GEOMTRIC STEINER TREE PACKING ON RHOMBOIDS

RHOMBOIDAL TILES Definition and graphs embedded in the plane. T i T j 15/30 Tile set T , layers L , chip area □ . T i ∈ T is a ℓ 1 -ball of unit radius, with ˚ T i ∩ ˚ T j = ∅ and □ ⊆ ∪ T ∈T T . Given a tile price function c : T → R ≥ 0 , we define the cost of a segment s as c ( s ) := ∑ T ∈T c ( T ) ℓ ( s ∩ T ) . The definition can be extented to rectilinear paths

WHY RHOMBOIDAL TILES? 1. continuous and piecewise linear; 2. smooth, unless it intersects some tile’s vertex or the endpoints lie on some tile’s boundary. If we drag a segment or its endpoints, the change in cost is described by a smooth linear function, as long as condition 2 is respected: 16/30 Rhomboids ( ℓ 1 balls) are simple objects! Let c ( s ) be the cost of a segment s . Then c ( s ) is (w.r.t. the coordinates of s ): ⇓

WHY RHOMBOIDAL TILES? 1. continuous and piecewise linear; 2. smooth, unless it intersects some tile’s vertex or the endpoints lie on some tile’s boundary. If we drag a segment or its endpoints, the change in cost is described by a smooth linear function, as long as condition 2 is respected: 16/30 Rhomboids ( ℓ 1 balls) are simple objects! Let c ( s ) be the cost of a segment s . Then c ( s ) is (w.r.t. the coordinates of s ): ⇓

u T , y usg n Y n RHOMBOIDAL TILES AS RESOURCES Given a resource price vector y ? Can we compute a route of (approx.) minimal cost c c E Y n y T w n l T 0 , if we set c T 17/30 Consumption: Congestion: Capacity: Definition R := T × L (rhomboidal tiles × layers). Let Y n denote a route for n ∈ N . T ∈ T × L on layer l T ; w ( n , l ) wire width in tracks on layer l . u ( T ) := total length of free tracks . s ∈ E ( Y n ) w ( n , l T ) ℓ ( s ∩ T ) ( usg n ( Y n )) T := ∑ u ( T ) . cong ( T ) := ∑ n ∈N ( usg n ( Y n )) T .

RHOMBOIDAL TILES AS RESOURCES Consumption: ? Can we compute a route of (approx.) minimal cost c y T Congestion: Capacity: Definition 17/30 R := T × L (rhomboidal tiles × layers). Let Y n denote a route for n ∈ N . T ∈ T × L on layer l T ; w ( n , l ) wire width in tracks on layer l . u ( T ) := total length of free tracks . s ∈ E ( Y n ) w ( n , l T ) ℓ ( s ∩ T ) ( usg n ( Y n )) T := ∑ u ( T ) . cong ( T ) := ∑ n ∈N ( usg n ( Y n )) T . Given a resource price vector y ∈ R R ≥ 0 , if we set c ( T ) := w ( n , l T ) u ( T ) , ⇒ y ⊺ usg n ( Y n ) = c ( E ( Y n ))

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.