Front-end Firmware Transition and Documentation - PowerPoint PPT Presentation

Front-end Firmware Transition and Documentation Status/Plans/Proposals Kurtis Nishimura University of Hawaii December 14, 2012 US Firmware Meeting 1 v2 Firmware Version 2 firmware is largely done: New interface to the DAQ

Front-end Firmware Transition and Documentation Status/Plans/Proposals Kurtis Nishimura University of Hawaii December 14, 2012 US Firmware Meeting 1

v2 Firmware • “Version 2” firmware is largely done: – New interface to the DAQ system. • Memory mapped registers for all current commands and auxiliary data readback. • New packet formats, inbound and outbound. – Selective digitization and readout. • Variable data size and new packet formats – Made for IRS2 Daughter Card Rev.B2. 2

What’s left to do for v2 firmware? • Currently version: – http://idlab-scrod.googlecode.com – Path: SCROD-boardstack/new_daq_interface • (Should migrate to trunk at some point.) • Since v2 will (hopefully) never be used for actual data acquisition, we do not need the following, still unimplemented features: – Distributed clocking (e.g., FTSW support). – Trigger interface (to GDL). • Nevertheless, this firmware is useful as-is, or almost as-is for other projects: – I would like to add at least one more feature (probably on my own time): PLL dynamic reconfiguration. • Will allow for software-reconfiguration of sampling/storage clocks to support arbitrary sampling rates, etc. 3

Moving to v3 (i.e., IRS3B) • I hope that I have made a flexible infrastructure that can relatively easily be maintained/expanded for v3 firmware. • Three main pieces of documentation I am developing: 1. Installation/compilation instructions for v2. • Already aware of a few extra installation instructions regarding command_interpreter.vhd 2. Firmware documentation: description of blocks and overall integration. 3. Interface document: for each system back-end can control, what does it do and how to use it. • Will distribute links as they become available. 4

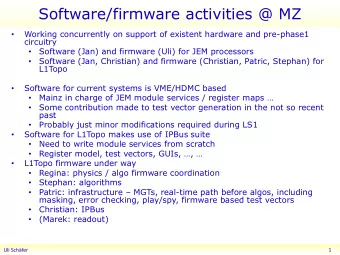

Firmware Statuses and Future Maintainers/Updaters(?) Auxiliary interfaces (Matt A. + ??): Command interpreter (Matt A. + ??) • • Generic I2C interface (EEPROM, temp Picoblaze assembly code • sensors, fiberoptic transceiver Verified working, recommend diagnostics) only changing when absolutely • Exists, working, recommend necessary (e.g., change startup no/minimal changes for v3. sequencing). • IRS3B control (Luca, Gary, Matt A.): Memory mapped register assignment • • Sampling and storage May need changes regularly for • Written for IRS2, must be new functionality. changed for IRS3B. General fiberoptic (Matt A.+Ryan C.?) • • Trigger memory for region-of-interest Verified working w/ Aurora. • mapping. May require revamping for Belle II • Exists, could use more testing. Link-like interface. • Region-of-interest Trigger functionality (Eric C.? + ??) • • Exists, working, recommend Trigger scalers exist, working. minimal/no changes for v3. Recommend no/minimal • Digitizer + packet builder changes. • • Written for IRS3, must be Trigger time stamping + data to changed for IRS3B. back-end trigger system, not • Packet building can remain implemented (fiberoptic slot largely the same. reserved). • ASIC feedback (+Leonid S., +Lynn W.) FTSW interface (?? + M. Nakao) • • Simple proportional feedback Mainly need to interface with exists for Wilkinson rate, needs Nakao-san on future FTSW more testing. updates. • Nothing yet on trigger width or 5 sampling rate.

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![Reversing firmware using radare2 [H2HC] A. Kochkov October, 2014 Motives Implement FOSS](https://c.sambuz.com/903352/reversing-firmware-using-radare2-h2hc-s.webp)