FPL 2019 High-performance Decoding of Variable-length Memory Data - PowerPoint PPT Presentation

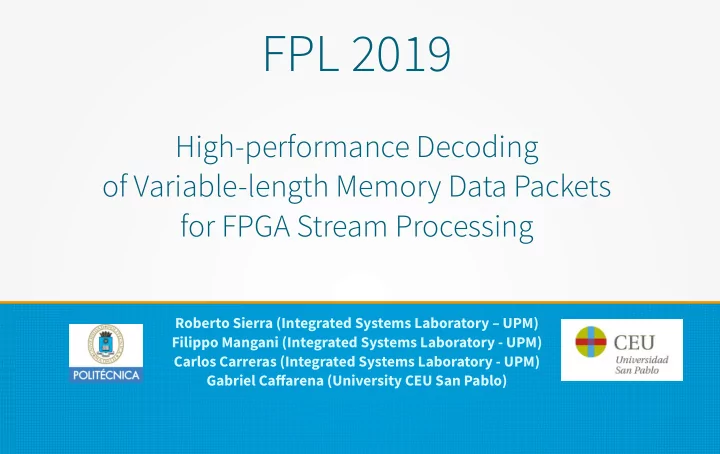

FPL 2019 High-performance Decoding of Variable-length Memory Data Packets for FPGA Stream Processing Roberto Sierra (Integrated Systems Laboratory UPM) Filippo Mangani (Integrated Systems Laboratory - UPM) Carlos Carreras (Integrated

FPL 2019 High-performance Decoding of Variable-length Memory Data Packets for FPGA Stream Processing Roberto Sierra (Integrated Systems Laboratory – UPM) Filippo Mangani (Integrated Systems Laboratory - UPM) Carlos Carreras (Integrated Systems Laboratory - UPM) Gabriel Cafgarena (University CEU San Pablo)

Motivation ● Variable-length data is used to efgiciently compress mesh- based datasets in scientific applications (e.g., CFD) ● Streaming variable-length data from memory to FPGA devices with a fixed-length encoding leads to wasting storage and bandwidth ● Each algorithm (e.g., 2D/3D, custom arithmetic formats) needs a difgerent set of data packet lengths – Known at synthesis time

Our proposal: Architecture ● Parameterizable On-board Memory ● Fully pipelined ● Elastic interfaces (valid/ready) Control Header Processor Logic ● 1 packet/line per clock cycle Packet Builder Headers 1 1 2 2 Packet Shifter 2 3 4 3 4 5 4 Packet Decoder 5 5 5 6 6 6 7 FPGA Memory 6 7 8 Overall architecture 7 8 9 9 9 10 Headers 9 10 Example input and output

Architecture (II) ● Packet Shifuer: 0..................0 Valid i 2 0..................0 – Unfortunately, no barrel shifuer i+1 2 Stage i 0..................0 S in FPGAs 2i i i+1 S2i+1 2 + 2 Ready – 4-1 (or 2-1) shifuer stages Packet Shifuer stage ● Packet Builder: Payload line Control signals – Concatenate memory lines 6 ● Header Decoder: – Computes shifu and number of Fourth Step Cache First Step Second Step Third Step Register Register Register Register Register lines needed by each packet Extended line Packet Builder

Results ● Synthesis results of example decoders Stratix V 5SGXMABN3F45C2 ● Speedup over fixed-length encoding

Thank you!

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.