Efficient Analysis of Pipeline Models for WCET Computation Stephan - PowerPoint PPT Presentation

A b s I n t Efficient Analysis of Pipeline Models for WCET Computation Stephan Wilhelm (sw@absint.com) AbsInt GmbH and Saarland University Outline 1. aiTs pipeline analysis 3. Why improve its efficiency? 5. BDD based pipeline analysis 7.

A b s I n t Efficient Analysis of Pipeline Models for WCET Computation Stephan Wilhelm (sw@absint.com) AbsInt GmbH and Saarland University

Outline 1. aiT’s pipeline analysis 3. Why improve its efficiency? 5. BDD based pipeline analysis 7. Generating pipeline analyzers 9. Status and prospects

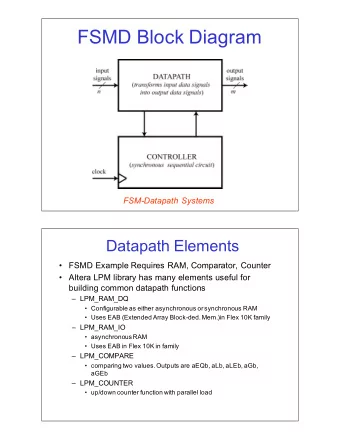

The aiT-Framework Executable Control-Flow Reconstruction Program Value Analyzer Pipeline Analyzer Cache Analyzer WCET Worst-Case Execution Visualization Path Analysis

Pipeline Analysis Pipeline Pipeline Model CFG a e b d c Abstraction a b instruction A Cache Analysis c d instruction B Timing Anomalies! d e e a State explosion.

Timing Anomalies • local worst case vs. global worst case – cache hit on global worst-case path (Lundquist/Stenström) – “unintuitive behavior” – no upper bound • Caused by features like: caches, out-of-order execution, branch prediction, ... No local worst-case decisions. State explosion.

Symbolic Representation of FSM State Sets FSM state sets characteristic functions BDD’s a = 1 b = 1 a b 01 ¬ a ∧ b a = 1 a = 0 0 1 b = 0 b = 0 a = 0 a ¬ a b = 1 01 00 A 2-bit automaton 0 1 1 01 00 10 11 1 - BDD size depends on variable ordering - worst case: exponential - in most cases better orderings are possible

BDD based Pipeline Analysis 11 Start set 01 11 00 10 00 10 1. Partition the set 01 01 11 00 10 A 2-bit automaton 2. Compute images 00: 01 00 10 00 10 01 11 01: 10 3. Apply inputs 10: 01 10 00 10 01 The program 4. Compute union 00 10 01

Model Specification & Validation • Documentation is often incorrect/incomplete. • Model specification is error-prone. • Trace validation is difficult. Generate analysis from HDL specification. • Verilog and VHDL can be compiled into FSM’s (Cheng, 1994). – Implemented in VIS model checker.

Generating Pipeline Analyzers HDL Abstraction Simplified HDL HDL->FSM compiler Properties FSM specification Program (CFG) Model Checker Pipeline Analyzer

Status and Prospects past 1. Implementation of proof-of-concept. – For simple examples. – Only one basic block. 2. Integration with DFA framework (PAG). today 3. Integration with CFG representation. 4. Specification of a real pipeline. – Infineon Tricore 2 future 5. Compare against “classic aiT”.

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.