Di i l T Di i l T Digital Testing Digital Testing i i Lecture - PowerPoint PPT Presentation

Di i l T Di i l T Digital Testing Digital Testing i i Lecture Lecture 4: Yield Analysis & L 4 Yi ld A : Yield Analysis & Yi ld A l i & l i & Product Quality Product Quality Instructor: Shaahin Hessabi Instructor:

Di i l T Di i l T Digital Testing Digital Testing i i Lecture Lecture 4: Yield Analysis & L 4 Yi ld A : Yield Analysis & Yi ld A l i & l i & Product Quality Product Quality Instructor: Shaahin Hessabi Instructor: Shaahin Hessabi Department of Computer Engineering Department of Computer Engineering Sharif University of Technology Sharif University of Technology Adapted from lecture notes prepared by the book authors Adapted from lecture notes prepared by the book authors

Yield Analysis & Product Quality Yield Analysis & Product Quality Yield Analysis & Product Quality Yield Analysis & Product Quality � Yield and manufacturing cost Yield and manufacturing cost g � Clustered defect yield formula Clustered defect yield formula � Yi ld i p � Yield improvement Yi ld i p Yield improvement t t � Defect level Defect level � Test data analysis Test data analysis � Example: SEMATECH chip Example: SEMATECH chip p p p p � Summary Summary Sharif University of Technology Testability: Lecture 4 Page 2 of 16

VLSI Chip Yield VLSI Chip Yield p � Defect: a physical imperfection in the processed wafer. Defect: a physical imperfection in the processed wafer. � A manufacturing defect is a finite chip area with A A A manufacturing defect is a finite chip area with f f d f d f f f h h h h electrically malfunctioning circuitry caused by errors in the electrically malfunctioning circuitry caused by errors in the fabrication process. f b i fabrication process. f b i i i � A chip with no manufacturing defect is called a good chip. A chip with no manufacturing defect is called a good chip. � Fraction (or percentage) of good chips produced in a Fraction (or percentage) of good chips produced in a manufacturing process is called the manufacturing process is called the yield g p g p yield ( Y) y ( ) Y) . . Cost of fabricating and testing a wafer � Cost of a chip = � Cost of a chip = Cost of a chip = Cost of a chip = ------------------------------------------------------ Yield * Number of chip sites on the wafer Sharif University of Technology Testability: Lecture 4 Page 3 of 16

Clustered VLSI Defects Clustered VLSI Defects Clustered VLSI Defects Clustered VLSI Defects Good chips Faulty chips Defects Wafer Clustered defects (VLSI) Unclustered defects Wafer yield = 17/22 = 0.77 Wafer yield = 12/22 = 0.55 Sharif University of Technology Testability: Lecture 4 Page 4 of 16

Yield Parameters Yield Parameters e d e d e e s e e s � Defect density ( Defect density ( d ) = Average number of defects per y ( y ( ) ) ) = Average number of defects per g g p p unit of chip area unit of chip area � Chip area ( Chip area ( A ) Clustering parameter ( α ) � Clustering parameter ( � Negative binomial distribution of defects, Negative binomial distribution of defects, p ( x p ( ) x ) = ) = Prob Prob (number of defects on a chip = P P b ( b (number of defects on a chip = x ( b b f d f f d f t t hi hi x ) ) ) x Γ ( α +x (Ad / α ) ( +x ) ) ) ( ( ) = ------------- ------------- . ---------------------- ---------------------- ) α +x +x x ! Γ ( α ) (1+Ad / α ) x ! ) (1+Ad where Γ is the gamma function α =0 , p (x , p (x ) is a delta function (max. clustering) ∞ α = = , p (x ) is Poisson distribution (no clustering) p (x ) i P i di ib i ( l i ) , Sharif University of Technology Testability: Lecture 4 Page 5 of 16

Yield Equation Yield Equation Yield Equation Yield Equation Y = Prob ( zero defect on a chip ) = p (0) Y = Prob ( zero defect on a chip ) = p (0) ) − α α / α ) Y = ( Y = ( = ( 1 = ( 1 1 + 1 + + Ad + Ad Ad / Ad / / ) ) , α = 0.5, Y = 0.58 , Example: Ad = 1.0 , p , ∞ ∞ e - A - Ad Unclustered defects: α = Unclustered defects: α , Y = e , Y , Y , Y e e ∞ Example: Ad = 1.0, α = p , Y = , Y = 0.37 0.37 too pessimistic ! Sharif University of Technology Testability: Lecture 4 Page 6 of 16

Defect Level or Reject Ratio Defect Level or Reject Ratio Defect Level or Reject Ratio Defect Level or Reject Ratio � Defect level Defect level (DL DL) is the ratio of faulty chips among the ) is the ratio of faulty chips among the chips that pass tests. chips that pass tests. p p p p � DL DL is measured as is measured as parts per million parts per million (ppm ppm). ). � DL DL is a measure of the effectiveness of tests. DL DL is a measure of the effectiveness of tests. is a measure of the effectiveness of tests. is a measure of the effectiveness of tests. � DL DL is a quantitative measure of the manufactured is a quantitative measure of the manufactured product quality For commercial VLSI chips a product quality For commercial VLSI chips a DL product quality. For commercial VLSI chips a product quality. For commercial VLSI chips a DL DL DL greater than greater than 500 500 ppm ppm is considered unacceptable. is considered unacceptable. (normally: (normally: 500 (normally: (normally: 500 500<DL< 500<DL< <DL<50 <DL<50 50) 50) Sharif University of Technology Testability: Lecture 4 Page 7 of 16

Determination of DL Determination of DL e e e e o o o o From field return data: Chips failing in the field are From field return data: Chips failing in the field are 1. 1. returned to the manufacturer. The number of returned to the manufacturer. The number of t t d t th d t th f f t t Th Th b b f f returned chips normalized to one million chips returned chips normalized to one million chips shipped is the shipped is the DL hi hi d i th d i th DL DL DL. . How chips are returned: How chips are returned: � a. a. Failing acceptance test. Failing acceptance test. ili ili b. b. Failing system test. Failing system test. c. c. Failing maintenance test Failing maintenance test Sharif University of Technology Testability: Lecture 4 Page 8 of 16

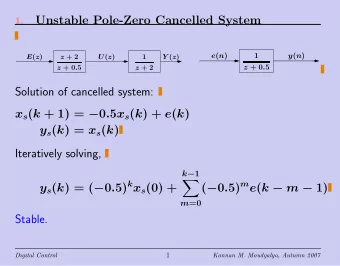

Determination of DL (cont’d) Determination of DL (cont’d) e e e e o o o o (co (co d) d) From test data: Fault coverage of tests and chip fallout From test data: Fault coverage of tests and chip fallout 2. 2. rate are analyzed. A modified yield model is fitted to rate are analyzed. A modified yield model is fitted to t t l l d A d A difi d i ld difi d i ld d l i fitt d t d l i fitt d t the fallout data to estimate the the fallout data to estimate the DL DL. . � Three parameters: (defect replaced by fault: electrical, Th Three parameters: (defect replaced by fault: electrical, Th (d f (d f l l d b f d b f l l l l i i l l Boolean, or functional malfunctions) Boolean, or functional malfunctions) � Fault density � Fault density, Fault density f Fault density, f f = average number of stuck f = average number of stuck = average number of stuck at faults per unit chip area = average number of stuck-at faults per unit chip area at faults per unit chip area at faults per unit chip area Fault clustering parameter, β � Fault clustering parameter, � Stuck Stuck- -at fault coverage, at fault coverage, T g Y ( T ) = (1 + TAf / β ) - β � The modified yield equation: The modified yield equation: � Assuming that tests with Assuming that tests with 100 g 100% fault coverage (T = % fault coverage (T =1 g ( g ( 1. .0 0) ) ) remove all faulty chips: remove all faulty chips: ) – β β yield, if T= Af / β ) yield, if T=1 1 � good chips good chips Y = Y Y = Y (1 1) = ( ) = (1 1 + + Af Sharif University of Technology Testability: Lecture 4 Page 9 of 16

Defect Level Defect Level Defect Level Defect Level Faulty chips considered as good Y ( T ) - Y (1) Y ( T ) Y (1) DL ( T ) = -------------------- -------------------- Y ( T ) All chips which pass the All chips which pass the test, with coverage T + TAf ) β ( β + = 1 - -------------------- -------------------- ( β + Af ) β Where T is the fault coverage of tests, Af is the average number of faults on the chip of area A , β is the fault clustering parameter. Af and β are determined by test data analysis. Sharif University of Technology Testability: Lecture 4 Page 10 of 16

Example: SEMATECH Chip Example: SEMATECH Chip Example: SEMATECH Chip Example: SEMATECH Chip � Bus interface controller ASIC fabricated and tested Bus interface controller ASIC fabricated and tested at IBM, Burlington, Vermont at IBM, Burlington, Vermont � 116 116, ,000 000 equivalent ( equivalent (2- -input NAND) gates input NAND) gates � 304 304- -pin package, pin package, 249 249 I/O I/O � Clock: Clock: 40 40MHz, some parts MHz, some parts 50 50MHz MHz 45 μ CMOS, � 0. .45 CMOS, 3 3. .3 3V, V, 9 9. .4 4mm x mm x 8 8. .8 8mm area mm area � Full scan, Full scan, 99 99. .79 79% fault coverage % fault coverage � Advantest Advantest 3381 3381 ATE, ATE, 18 18, ,466 466 chips tested at chips tested at 2 5MH t t l 2. .5MHz test clock MH t t l MHz test clock k k � Data obtained courtesy of Phil Nigh (IBM) Data obtained courtesy of Phil Nigh (IBM) Sharif University of Technology Testability: Lecture 4 Page 11 of 16

Test Coverage from Fault Simulator Test Coverage from Fault Simulator Test Coverage from Fault Simulator Test Coverage from Fault Simulator ge coverag co fault at f -at Stuck- Stuc Vector n Vector n ctor number ctor number mber mber Sharif University of Technology Testability: Lecture 4 Page 12 of 16

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.