Critical Power Slope: Understanding the Runtime Effects of - PowerPoint PPT Presentation

Critical Power Slope: Understanding the Runtime Effects of Frequency Scaling Akihiko Miyoshi ,Charles Lefurgy , Eric Van Hensbergen , Ram Rajamony , Raj Rajkumar Real-Time and Multimedia Systems Lab Austin Research

Critical Power Slope: Understanding the Runtime Effects of Frequency Scaling Akihiko Miyoshi † ,Charles Lefurgy ‡ , Eric Van Hensbergen ‡ , Ram Rajamony ‡ , Raj Rajkumar † † Real-Time and Multimedia Systems Lab ‡ Austin Research Laboratory Dept. of Electrical and Computer Engineering IBM Carnegie Mellon University

The Question • Operating Points – [600MHz,6V], [525MHz,4.2V],[450MHz,2.8V],[375MHz,2V],[300MHz, 1.7V], [225MHz,1.5V],[150MHz,1.45V] • Where should I operate (for energy efficiency)? – Dynamic Voltage Scaling (DVS) algorithms – Lowest performance without sacrificing user/application requirement • Why lowest performance is not always the best – Even for voltage scaling systems

Energy Efficiency power Low frequency High frequency ... time Watts Watts E active E E active idle t t

Assumption • Majority of OS policies assume Watts Watts < E active E E active idle t t • Not always the case! – When it is not the case? – How do we determine this?

Outline • Motivation E E – < : not always true f f high low – How do we choose which operating points to use? • Measurement results • Analytical model: Critical Power Slope • Analysis on voltage scaling systems • Conclusion

Power Management Techniques • Provides multiple operating points – [600MHz,6V],[450MHz,2.8V],[300MHz, 1.7V]…etc • Three empirical data points – Frequency Scaling • PowerPC 405GP – Clock Throttling • Pentium with ACPI – Voltage Scaling • Strong ARM SA-1100 • Note: We are not making any statement on the benefits of these techniques! – These are merely samples which real systems use to manage power.

Basic Results • Runtime and frequency – CPU intensive workload: inverse relationship • Power and frequency – Frequency scaling, clock throttling processors • CPU active: linear relationship • CPU idle: constant CPU active Power m: slope CPU idle Frequency

Energy Consumption • Compare energy consumption at different operating points – Same workload W – Same amount of time t power t E active E idle time

Energy consumption 2591J 174.3sec (Pentium L1 cache read hit) Joul es 3000 2500 2490J 2000 1500 Ext r a I dl e Syst em Act i ve 1000 500 0 12 25 37 50 62 75 87 100 CPU per f or mance ( %)

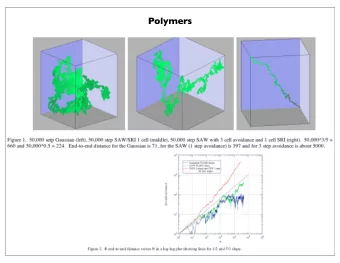

Energy consumption (PPC L1 cache read hit) 162J 200 136J 66.4sec 150 Ex t r a I dl e Ot her s Joul es 100 SDRAM CPU 50 0 66 133 200 266 M Hz

Measurement Results • Results consistent with different workloads – Register, L1 cache, memory, disk accesses – Web server (Pentium) • Pentium – Highest frequency always energy efficient • PowerPC – Lowest frequency always energy efficient • Why? – What happens on voltage scaling systems?

Outline • Motivation – Which operating points should we consider? • Measurement results – Pentium: highest performance better – PowerPC: lowest performance better • Analytical model: Critical Power Slope • Analysis on voltage scaling systems • Conclusion

Characterization • CPU intensive workload W • Frequency f min – Assume utilization of system = 1 T – units of time to complete W f min – Energy consumed = E T P f min f min f min f > • At frequency ( f ) min f min T – Time to compute W : f min f f min T – Remaining extra idle time: − f min( 1 ) f = + − f min f min E ( T ) P T ( 1 ) P f f min f f min idle f f

Critical Power Slope = + − P P m ( f f ) f f min min – Power increases linearly with frequency – m : slope = + − + − f min f min E ( T )[ P m ( f f )] T ( 1 ) P f f min f min min f min idle f f f • Is energy efficient?? min E > E – True if f f min – Depends on m

Critical Power Slope cont’d • Use slope m to characterize system E = E – Find hypothetical m for and call it f f min Critical Power Slope (CPS) = − m P P f min idle critical f min

What does it mean? m > m critical Power = − m P P f min idle critical f min m < m critical m critical P f min P P idle idle f min Freq

Implications of CPS m < m critical • If E > E < – Energy efficient to run at higher freq. f f min – Pentium = m − 15 W 12 W = critical . 028 × 848 MHz 12 . 5 % = m − 30 W 15 W = . 020 × 848 MHz 12 . 5 % m > m • If critical E > E – Energy efficient to run at lower freq. f f min – PowerPC = m − 2 . 27 W 2 . 02 W = critical . 0038 66 MHz = m − 3 . 13 W 2 . 27 W = . 0043 − 266 MHz 66 MHz

Voltage Scaling Processors (Strong Arm SA-1100) J.Pouwelse, K.Langendoen, and H. Sips, “Dynamic Voltage Scaling on a Low-Power Microprocessor”, MOBICOM2001

CPS for voltage scaling system f • Look at every operating point at frequency x − = P P fx m fx fx idle fx critical m < m fx fx • If critical f – Energy efficient at higher frequency than x m > m fx fx • If f critical – Energy efficient at lower frequency than x

Analysis on SA-1100 • Above 74MHz m > m fx fx critical • At 74MHz = 74 MHz − m 121 mW 46 mW = 0 . 001 critical 74 MHz = 74 MHz − m 121 mW 106 mW = 0 . 001 − 74 MHz 59 MHz • Below 74MHz m < m fx fx critical • Energy Inefficient below 74MHz!

Summary Power Pentium Power PowerPC Frequency Frequency Power SA-1100 CPS: Characterizes the runtime trade-off of power management techniques Frequency

Conclusion • Which operating points should we consider? – Traditional DVS algorithms attempt to go to lowest frequency – Not always the best choice • Critical Power Slope • Identifies energy inefficient operating points • Can be used to inform OS (DVS algorithms) of operating points it should not consider

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.