Compositional Verification of PLC Software using Horn Clauses and - PowerPoint PPT Presentation

Compositional Verification of PLC Software using Horn Clauses and Mode Abstraction Dimitri Bohlender | Stefan Kowalewski WODES 2018, June 1, 2018 Introduction CHC-based Verification Conclusion Outline Introduction CHC-based Verification

Introduction CHC-based Verification Conclusion Motivation Mode Spaces in Model-Checking 0 “Idle” req && !m !(req && !m) DiagCode =0x0000 1 4 h.data:=in ReqHandler( 2 ReqHandler( h.data, h.data, h.DiagCode, “Processing” DiagCode h.DiagCode, h.res =0x8000 h.res ) ) 3 5 out:=h.res out:=h.res 6 “Error” DiagCode m:=req =0xC001 7 Figure: Main CFA of example Figure: Mode space of ReqHandler ◮ Requests are processed in ≤ two execution cycles? ⇒ On request, “Processing” mode is reached in a single cycle Compositional Verification of PLC Software using CHCs and Mode Abstraction 4 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Motivation Requirements Towards Formalism & Model Checker ◮ Compositional reasoning ◮ Integrates with abstraction (no cloning or inlining) of calls (call summaries) Example Example ◮ Let f1:FB; f2:FB; ◮ Consider abs( x ) = y ◮ Reason about FB( . . . ) ◮ Use summary ◮ Avoid f1( . . . ) , f2( . . . ) and y ≥ 0 instruction cloning ◮ Until details needed ◮ Constrained Horn Clauses (CHCs) meet these ◮ Uniform formalism for symbolic model checking of software Compositional Verification of PLC Software using CHCs and Mode Abstraction 5 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Motivation Requirements Towards Formalism & Model Checker ◮ Compositional reasoning ◮ Integrates with abstraction (no cloning or inlining) of calls (call summaries) Example Example ◮ Let f1:FB; f2:FB; ◮ Consider abs( x ) = y ◮ Reason about FB( . . . ) ◮ Use summary ◮ Avoid f1( . . . ) , f2( . . . ) and y ≥ 0 instruction cloning ◮ Until details needed ◮ Constrained Horn Clauses (CHCs) meet these ◮ Uniform formalism for symbolic model checking of software Compositional Verification of PLC Software using CHCs and Mode Abstraction 5 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Motivation Requirements Towards Formalism & Model Checker ◮ Compositional reasoning ◮ Integrates with abstraction (no cloning or inlining) of calls (call summaries) Example Example ◮ Let f1:FB; f2:FB; ◮ Consider abs( x ) = y ◮ Reason about FB( . . . ) ◮ Use summary ◮ Avoid f1( . . . ) , f2( . . . ) and y ≥ 0 instruction cloning ◮ Until details needed ◮ Constrained Horn Clauses (CHCs) meet these ◮ Uniform formalism for symbolic model checking of software Compositional Verification of PLC Software using CHCs and Mode Abstraction 5 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Motivation Requirements Towards Formalism & Model Checker ◮ Compositional reasoning ◮ Integrates with abstraction (no cloning or inlining) of calls (call summaries) Example Example ◮ Let f1:FB; f2:FB; ◮ Consider abs( x ) = y ◮ Reason about FB( . . . ) ◮ Use summary ◮ Avoid f1( . . . ) , f2( . . . ) and y ≥ 0 instruction cloning ◮ Until details needed ◮ Constrained Horn Clauses (CHCs) meet these ◮ Uniform formalism for symbolic model checking of software Compositional Verification of PLC Software using CHCs and Mode Abstraction 5 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Motivation Requirements Towards Formalism & Model Checker ◮ Compositional reasoning ◮ Integrates with abstraction (no cloning or inlining) of calls (call summaries) Example Example ◮ Let f1:FB; f2:FB; ◮ Consider abs( x ) = y ◮ Reason about FB( . . . ) ◮ Use summary ◮ Avoid f1( . . . ) , f2( . . . ) and y ≥ 0 instruction cloning ◮ Until details needed ◮ Constrained Horn Clauses (CHCs) meet these ◮ Uniform formalism for symbolic model checking of software Compositional Verification of PLC Software using CHCs and Mode Abstraction 5 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Motivation Requirements Towards Formalism & Model Checker ◮ Compositional reasoning ◮ Integrates with abstraction (no cloning or inlining) of calls (call summaries) Example Example ◮ Let f1:FB; f2:FB; ◮ Consider abs( x ) = y ◮ Reason about FB( . . . ) ◮ Use summary ◮ Avoid f1( . . . ) , f2( . . . ) and y ≥ 0 instruction cloning ◮ Until details needed ◮ Constrained Horn Clauses (CHCs) meet these ◮ Uniform formalism for symbolic model checking of software Compositional Verification of PLC Software using CHCs and Mode Abstraction 5 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Motivation Requirements Towards Formalism & Model Checker ◮ Compositional reasoning ◮ Integrates with abstraction (no cloning or inlining) of calls (call summaries) Example Example ◮ Let f1:FB; f2:FB; ◮ Consider abs( x ) = y ◮ Reason about FB( . . . ) ◮ Use summary ◮ Avoid f1( . . . ) , f2( . . . ) and y ≥ 0 instruction cloning ◮ Until details needed ◮ Constrained Horn Clauses (CHCs) meet these ◮ Uniform formalism for symbolic model checking of software Compositional Verification of PLC Software using CHCs and Mode Abstraction 5 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Motivation Requirements Towards Formalism & Model Checker ◮ Compositional reasoning ◮ Integrates with abstraction (no cloning or inlining) of calls (call summaries) Example Example ◮ Let f1:FB; f2:FB; ◮ Consider abs( x ) = y ◮ Reason about FB( . . . ) ◮ Use summary ◮ Avoid f1( . . . ) , f2( . . . ) and y ≥ 0 instruction cloning ◮ Until details needed ◮ Constrained Horn Clauses (CHCs) meet these ◮ Uniform formalism for symbolic model checking of software Compositional Verification of PLC Software using CHCs and Mode Abstraction 5 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Motivation Requirements Towards Formalism & Model Checker ◮ Compositional reasoning ◮ Integrates with abstraction (no cloning or inlining) of calls (call summaries) Example Example ◮ Let f1:FB; f2:FB; ◮ Consider abs( x ) = y ◮ Reason about FB( . . . ) ◮ Use summary ◮ Avoid f1( . . . ) , f2( . . . ) and y ≥ 0 instruction cloning ◮ Until details needed ◮ Constrained Horn Clauses (CHCs) meet these ◮ Uniform formalism for symbolic model checking of software Compositional Verification of PLC Software using CHCs and Mode Abstraction 5 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Motivation Requirements Towards Formalism & Model Checker ◮ Compositional reasoning ◮ Integrates with abstraction (no cloning or inlining) of calls (call summaries) Example Example ◮ Let f1:FB; f2:FB; ◮ Consider abs( x ) = y ◮ Reason about FB( . . . ) ◮ Use summary ◮ Avoid f1( . . . ) , f2( . . . ) and y ≥ 0 instruction cloning ◮ Until details needed ◮ Constrained Horn Clauses (CHCs) meet these ◮ Uniform formalism for symbolic model checking of software Compositional Verification of PLC Software using CHCs and Mode Abstraction 5 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Constrained Horn Clauses Constrained Horn Clauses ◮ Special case of Satisfiability Modulo Theories (SMT) Definition Given sets of variables V , function symbols F , and predicates P , a Constrained Horn Clause (CHC) is a formula ∀V p 1 ( � X 1 ) ∧ · · · ∧ p k ( � → h ( � X k ) ∧ ϕ X ) , k ≥ 0 , � �� � � �� � body head where ◮ � X i , � X ⊆ V are possibly empty vectors of variables ◮ ϕ is a constraint over F and V ◮ CHCs satisfiable if satisfying interpretation of p i exists Compositional Verification of PLC Software using CHCs and Mode Abstraction 6 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Constrained Horn Clauses Constrained Horn Clauses ◮ Special case of Satisfiability Modulo Theories (SMT) Definition Given sets of variables V , function symbols F , and predicates P , a Constrained Horn Clause (CHC) is a formula ∀V p 1 ( � X 1 ) ∧ · · · ∧ p k ( � → h ( � X k ) ∧ ϕ X ) , k ≥ 0 , � �� � � �� � body head where ◮ � X i , � X ⊆ V are possibly empty vectors of variables ◮ ϕ is a constraint over F and V ◮ CHCs satisfiable if satisfying interpretation of p i exists Compositional Verification of PLC Software using CHCs and Mode Abstraction 6 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Constrained Horn Clauses Constrained Horn Clauses ◮ Special case of Satisfiability Modulo Theories (SMT) Definition Given sets of variables V , function symbols F , and predicates P , a Constrained Horn Clause (CHC) is a formula ∀V p 1 ( � X 1 ) ∧ · · · ∧ p k ( � → h ( � X k ) ∧ ϕ X ) , k ≥ 0 , � �� � � �� � body head where ◮ � X i , � X ⊆ V are possibly empty vectors of variables ◮ ϕ is a constraint over F and V ◮ CHCs satisfiable if satisfying interpretation of p i exists Compositional Verification of PLC Software using CHCs and Mode Abstraction 6 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Constrained Horn Clauses Constrained Horn Clauses ◮ Special case of Satisfiability Modulo Theories (SMT) Definition Given sets of variables V , function symbols F , and predicates P , a Constrained Horn Clause (CHC) is a formula ∀V p 1 ( � X 1 ) ∧ · · · ∧ p k ( � → h ( � X k ) ∧ ϕ X ) , k ≥ 0 , � �� � � �� � body head where ◮ � X i , � X ⊆ V are possibly empty vectors of variables ◮ ϕ is a constraint over F and V ◮ CHCs satisfiable if satisfying interpretation of p i exists Compositional Verification of PLC Software using CHCs and Mode Abstraction 6 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Constrained Horn Clauses Constrained Horn Clauses ◮ Special case of Satisfiability Modulo Theories (SMT) Definition Given sets of variables V , function symbols F , and predicates P , a Constrained Horn Clause (CHC) is a formula ∀V p 1 ( � X 1 ) ∧ · · · ∧ p k ( � → h ( � X k ) ∧ ϕ X ) , k ≥ 0 , � �� � � �� � body head where ◮ � X i , � X ⊆ V are possibly empty vectors of variables ◮ ϕ is a constraint over F and V ◮ CHCs satisfiable if satisfying interpretation of p i exists Compositional Verification of PLC Software using CHCs and Mode Abstraction 6 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Concept For each block type A with signature VarTypes , add a predicate p A : Loc × VarTypes × Loc × VarTypes → B � �� � � �� � source target ◮ Will define transitive reachability within A ⇒ Observable semantics of procedure captured by , � , � X ′ ) p A ( l entry X, l exit ���� � �� � const const ◮ Solving CHC � finding over-approximating summary of A Compositional Verification of PLC Software using CHCs and Mode Abstraction 7 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Concept For each block type A with signature VarTypes , add a predicate p A : Loc × VarTypes × Loc × VarTypes → B � �� � � �� � source target ◮ Will define transitive reachability within A ⇒ Observable semantics of procedure captured by , � , � X ′ ) p A ( l entry X, l exit ���� � �� � const const ◮ Solving CHC � finding over-approximating summary of A Compositional Verification of PLC Software using CHCs and Mode Abstraction 7 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Concept For each block type A with signature VarTypes , add a predicate p A : Loc × VarTypes × Loc × VarTypes → B � �� � � �� � source target ◮ Will define transitive reachability within A ⇒ Observable semantics of procedure captured by , � , � X ′ ) p A ( l entry X, l exit ���� � �� � const const ◮ Solving CHC � finding over-approximating summary of A Compositional Verification of PLC Software using CHCs and Mode Abstraction 7 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Concept For each block type A with signature VarTypes , add a predicate p A : Loc × VarTypes × Loc × VarTypes → B � �� � � �� � source target ◮ Will define transitive reachability within A ⇒ Observable semantics of procedure captured by , � , � X ′ ) p A ( l entry X, l exit ���� � �� � const const ◮ Solving CHC � finding over-approximating summary of A Compositional Verification of PLC Software using CHCs and Mode Abstraction 7 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Encoding a Transition Variables instances: ◮ � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � req ′ , in ′ , m ′ , h . data ′ , h . DiagCode ′ , h . res ′ , out ′ � X ′ = ◮ � 0 req && !m !(req && !m) 1 4 Transitive Reachability: h.data:=in ReqHandler( p Main ( l, � X, 1 , � 2 X ′ ) ReqHandler( h.data, h.data, h.DiagCode, ∧ h . data ′′ = in ′ ∧ id ( X ′ \ � h . data ′ � ) h.DiagCode, h.res h.res ) → p Main ( l, � X, 2 , � X ′′ ) ) 3 5 out:=h.res out:=h.res 6 m:=req 7 Compositional Verification of PLC Software using CHCs and Mode Abstraction 8 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Encoding a Transition Variables instances: ◮ � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � req ′ , in ′ , m ′ , h . data ′ , h . DiagCode ′ , h . res ′ , out ′ � X ′ = ◮ � 0 req && !m !(req && !m) 1 4 Transitive Reachability: h.data:=in ReqHandler( p Main ( l, � X, 1 , � 2 X ′ ) ReqHandler( h.data, h.data, h.DiagCode, ∧ h . data ′′ = in ′ ∧ id ( X ′ \ � h . data ′ � ) h.DiagCode, h.res h.res ) → p Main ( l, � X, 2 , � X ′′ ) ) 3 5 out:=h.res out:=h.res 6 m:=req 7 Compositional Verification of PLC Software using CHCs and Mode Abstraction 8 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Encoding a Transition Variables instances: ◮ � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � req ′ , in ′ , m ′ , h . data ′ , h . DiagCode ′ , h . res ′ , out ′ � X ′ = ◮ � 0 req && !m !(req && !m) 1 4 Transitive Reachability: h.data:=in ReqHandler( p Main ( l, � X, 1 , � 2 X ′ ) ReqHandler( h.data, h.data, h.DiagCode, ∧ h . data ′′ = in ′ ∧ id ( X ′ \ � h . data ′ � ) h.DiagCode, h.res h.res ) → p Main ( l, � X, 2 , � X ′′ ) ) 3 5 out:=h.res out:=h.res 6 m:=req 7 Compositional Verification of PLC Software using CHCs and Mode Abstraction 8 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Encoding a Transition Variables instances: ◮ � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � req ′ , in ′ , m ′ , h . data ′ , h . DiagCode ′ , h . res ′ , out ′ � X ′ = ◮ � 0 req && !m !(req && !m) 1 4 Transitive Reachability: h.data:=in ReqHandler( p Main ( l, � X, 1 , � 2 X ′ ) ReqHandler( h.data, h.data, h.DiagCode, ∧ h . data ′′ = in ′ ∧ id ( X ′ \ � h . data ′ � ) h.DiagCode, h.res h.res ) → p Main ( l, � X, 2 , � X ′′ ) ) 3 5 out:=h.res out:=h.res 6 m:=req 7 Compositional Verification of PLC Software using CHCs and Mode Abstraction 8 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Encoding a Transition Variables instances: ◮ � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � req ′ , in ′ , m ′ , h . data ′ , h . DiagCode ′ , h . res ′ , out ′ � X ′ = ◮ � 0 req && !m !(req && !m) 1 4 Transitive Reachability: h.data:=in ReqHandler( p Main ( l, � X, 1 , � 2 X ′ ) ReqHandler( h.data, h.data, h.DiagCode, ∧ h . data ′′ = in ′ ∧ id ( X ′ \ � h . data ′ � ) h.DiagCode, h.res h.res ) → p Main ( l, � X, 2 , � X ′′ ) ) 3 5 out:=h.res out:=h.res 6 m:=req 7 Compositional Verification of PLC Software using CHCs and Mode Abstraction 8 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Encoding a Transition Variables instances: ◮ � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � req ′ , in ′ , m ′ , h . data ′ , h . DiagCode ′ , h . res ′ , out ′ � X ′ = ◮ � 0 req && !m !(req && !m) 1 4 Transitive Reachability: h.data:=in ReqHandler( p Main ( l, � X, 1 , � 2 X ′ ) ReqHandler( h.data, h.data, h.DiagCode, ∧ h . data ′′ = in ′ ∧ id ( X ′ \ � h . data ′ � ) h.DiagCode, h.res h.res ) → p Main ( l, � X, 2 , � X ′′ ) ) 3 5 out:=h.res out:=h.res 6 m:=req 7 Compositional Verification of PLC Software using CHCs and Mode Abstraction 8 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Encoding a Call Variables instances: � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � �� � � X h . . . Transitive Reachability (& call summary): p Main ( l, � X, 2 , � X ′ ) 2 ReqHandler( X ′ \ � h.data, ∧ p ReqHandler (0 , � h , 42 , � h ) ∧ id ( � X ′ X ′′ X ′ h ) h.DiagCode, ∧ S ReqHandler ( � h , � X ′ X ′′ h.res h ) ) 3 → p Main ( l, � X, 3 , � X ′′ ) . . . Compositional Verification of PLC Software using CHCs and Mode Abstraction 9 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Encoding a Call Variables instances: � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � �� � � X h . . . Transitive Reachability (& call summary): p Main ( l, � X, 2 , � X ′ ) 2 ReqHandler( X ′ \ � h.data, ∧ p ReqHandler (0 , � h , 42 , � h ) ∧ id ( � X ′ X ′′ X ′ h ) h.DiagCode, ∧ S ReqHandler ( � h , � X ′ X ′′ h.res h ) ) 3 → p Main ( l, � X, 3 , � X ′′ ) . . . Compositional Verification of PLC Software using CHCs and Mode Abstraction 9 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Encoding a Call Variables instances: � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � �� � � X h . . . Transitive Reachability (& call summary): p Main ( l, � X, 2 , � X ′ ) 2 ReqHandler( X ′ \ � h.data, ∧ p ReqHandler (0 , � h , 42 , � h ) ∧ id ( � X ′ X ′′ X ′ h ) h.DiagCode, ∧ S ReqHandler ( � h , � X ′ X ′′ h.res h ) ) 3 → p Main ( l, � X, 3 , � X ′′ ) . . . Compositional Verification of PLC Software using CHCs and Mode Abstraction 9 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Encoding a Call Variables instances: � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � �� � � X h . . . Transitive Reachability (& call summary): p Main ( l, � X, 2 , � X ′ ) 2 ReqHandler( X ′ \ � h.data, ∧ p ReqHandler (0 , � h , 42 , � h ) ∧ id ( � X ′ X ′′ X ′ h ) h.DiagCode, ∧ S ReqHandler ( � h , � X ′ X ′′ h.res h ) ) 3 → p Main ( l, � X, 3 , � X ′′ ) . . . Compositional Verification of PLC Software using CHCs and Mode Abstraction 9 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Encoding a Call Variables instances: � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � �� � � X h . . . Transitive Reachability (& call summary): p Main ( l, � X, 2 , � X ′ ) 2 ReqHandler( X ′ \ � h.data, ∧ p ReqHandler (0 , � h , 42 , � h ) ∧ id ( � X ′ X ′′ X ′ h ) h.DiagCode, ∧ S ReqHandler ( � h , � X ′ X ′′ h.res h ) ) 3 → p Main ( l, � X, 3 , � X ′′ ) . . . Compositional Verification of PLC Software using CHCs and Mode Abstraction 9 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Encoding a Call Variables instances: � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � �� � � X h . . . Transitive Reachability (& call summary): p Main ( l, � X, 2 , � X ′ ) 2 ReqHandler( X ′ \ � h.data, ∧ p ReqHandler (0 , � h , 42 , � h ) ∧ id ( � X ′ X ′′ X ′ h ) h.DiagCode, ∧ S ReqHandler ( � h , � X ′ X ′′ h.res h ) ) 3 → p Main ( l, � X, 3 , � X ′′ ) . . . Compositional Verification of PLC Software using CHCs and Mode Abstraction 9 / 15 D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Checking Safety Specifications 0 req && !m !(req && !m) ◮ Does safety property safe ( � X ) 1 4 h.data:=in hold at the end of every cycle? ReqHandler( 2 ReqHandler( h.data, ⇒ Yes, if adding h.data, h.DiagCode, h.DiagCode, h.res p Main (0 , � X, 7 , � X ′ ) → safe ( � X ′ ) h.res ) ) 3 5 keeps CHCs satisfiable out:=h.res out:=h.res 6 ◮ Violated, if unsatisfiable m:=req 7 10 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Checking Safety Specifications 0 req && !m !(req && !m) ◮ Does safety property safe ( � X ) 1 4 h.data:=in hold at the end of every cycle? ReqHandler( 2 ReqHandler( h.data, ⇒ Yes, if adding h.data, h.DiagCode, h.DiagCode, h.res p Main (0 , � X, 7 , � X ′ ) → safe ( � X ′ ) h.res ) ) 3 5 keeps CHCs satisfiable out:=h.res out:=h.res 6 ◮ Violated, if unsatisfiable m:=req 7 10 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Modelling of PLC Software with CHCs Checking Safety Specifications 0 req && !m !(req && !m) ◮ Does safety property safe ( � X ) 1 4 h.data:=in hold at the end of every cycle? ReqHandler( 2 ReqHandler( h.data, ⇒ Yes, if adding h.data, h.DiagCode, h.DiagCode, h.res p Main (0 , � X, 7 , � X ′ ) → safe ( � X ′ ) h.res ) ) 3 5 keeps CHCs satisfiable out:=h.res out:=h.res 6 ◮ Violated, if unsatisfiable m:=req 7 10 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Approximating the Mode-Space Idea: ◮ Procedure’s complexity needs to be low w.r.t. CHC-solving ⇒ Adapt value-set analysis (VSA) to determine mode-transitions Procedure: 1. Use global VSA to approximate all variables’ values 2. For each function block type, e.g. ReqHandler 2.1 For each computed mode-value, e.g. { 0 , 0x8000 , 0xC001 } • Keep global VSA values but fix mode, e.g. set DiagCode=0 • Compute block’s single-cycle VSA • Interpret resulting mode-values as targets, e.g. { 0 , 0x8000 } 11 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Approximating the Mode-Space Idea: ◮ Procedure’s complexity needs to be low w.r.t. CHC-solving ⇒ Adapt value-set analysis (VSA) to determine mode-transitions Procedure: 1. Use global VSA to approximate all variables’ values 2. For each function block type, e.g. ReqHandler 2.1 For each computed mode-value, e.g. { 0 , 0x8000 , 0xC001 } • Keep global VSA values but fix mode, e.g. set DiagCode=0 • Compute block’s single-cycle VSA • Interpret resulting mode-values as targets, e.g. { 0 , 0x8000 } 11 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Approximating the Mode-Space Idea: ◮ Procedure’s complexity needs to be low w.r.t. CHC-solving ⇒ Adapt value-set analysis (VSA) to determine mode-transitions Procedure: 1. Use global VSA to approximate all variables’ values 2. For each function block type, e.g. ReqHandler 2.1 For each computed mode-value, e.g. { 0 , 0x8000 , 0xC001 } • Keep global VSA values but fix mode, e.g. set DiagCode=0 • Compute block’s single-cycle VSA • Interpret resulting mode-values as targets, e.g. { 0 , 0x8000 } 11 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Approximating the Mode-Space Idea: ◮ Procedure’s complexity needs to be low w.r.t. CHC-solving ⇒ Adapt value-set analysis (VSA) to determine mode-transitions Procedure: 1. Use global VSA to approximate all variables’ values 2. For each function block type, e.g. ReqHandler 2.1 For each computed mode-value, e.g. { 0 , 0x8000 , 0xC001 } • Keep global VSA values but fix mode, e.g. set DiagCode=0 • Compute block’s single-cycle VSA • Interpret resulting mode-values as targets, e.g. { 0 , 0x8000 } 11 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Approximating the Mode-Space Idea: ◮ Procedure’s complexity needs to be low w.r.t. CHC-solving ⇒ Adapt value-set analysis (VSA) to determine mode-transitions Procedure: 1. Use global VSA to approximate all variables’ values 2. For each function block type, e.g. ReqHandler 2.1 For each computed mode-value, e.g. { 0 , 0x8000 , 0xC001 } • Keep global VSA values but fix mode, e.g. set DiagCode=0 • Compute block’s single-cycle VSA • Interpret resulting mode-values as targets, e.g. { 0 , 0x8000 } 11 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Approximating the Mode-Space Idea: ◮ Procedure’s complexity needs to be low w.r.t. CHC-solving ⇒ Adapt value-set analysis (VSA) to determine mode-transitions Procedure: 1. Use global VSA to approximate all variables’ values 2. For each function block type, e.g. ReqHandler 2.1 For each computed mode-value, e.g. { 0 , 0x8000 , 0xC001 } • Keep global VSA values but fix mode, e.g. set DiagCode=0 • Compute block’s single-cycle VSA • Interpret resulting mode-values as targets, e.g. { 0 , 0x8000 } 11 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Approximating the Mode-Space Idea: ◮ Procedure’s complexity needs to be low w.r.t. CHC-solving ⇒ Adapt value-set analysis (VSA) to determine mode-transitions Procedure: 1. Use global VSA to approximate all variables’ values 2. For each function block type, e.g. ReqHandler 2.1 For each computed mode-value, e.g. { 0 , 0x8000 , 0xC001 } • Keep global VSA values but fix mode, e.g. set DiagCode=0 • Compute block’s single-cycle VSA • Interpret resulting mode-values as targets, e.g. { 0 , 0x8000 } 11 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Approximating the Mode-Space Idea: ◮ Procedure’s complexity needs to be low w.r.t. CHC-solving ⇒ Adapt value-set analysis (VSA) to determine mode-transitions Procedure: 1. Use global VSA to approximate all variables’ values 2. For each function block type, e.g. ReqHandler 2.1 For each computed mode-value, e.g. { 0 , 0x8000 , 0xC001 } • Keep global VSA values but fix mode, e.g. set DiagCode=0 • Compute block’s single-cycle VSA • Interpret resulting mode-values as targets, e.g. { 0 , 0x8000 } 11 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Mode-Space as Call Summary ◮ Mode-space constrains possible transitions “Idle” ⇒ Yields call summary S ReqHandler ( � X h , � DiagCode X ′ h ) : =0x0000 ( h . DiagCode = 0 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0x8000 ) “Processing” ∧ ( h . DiagCode = 0x8000 → h . DiagCode ′ = 0 DiagCode =0x8000 ∨ h . DiagCode ′ = 0xC001 ) ∧ ( h . DiagCode = 0xC001 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0xC001 ) “Error” DiagCode =0xC001 ◮ Add to encoding of each call of ReqHandler 12 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Mode-Space as Call Summary ◮ Mode-space constrains possible transitions “Idle” ⇒ Yields call summary S ReqHandler ( � X h , � DiagCode X ′ h ) : =0x0000 ( h . DiagCode = 0 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0x8000 ) “Processing” ∧ ( h . DiagCode = 0x8000 → h . DiagCode ′ = 0 DiagCode =0x8000 ∨ h . DiagCode ′ = 0xC001 ) ∧ ( h . DiagCode = 0xC001 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0xC001 ) “Error” DiagCode =0xC001 ◮ Add to encoding of each call of ReqHandler 12 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Mode-Space as Call Summary ◮ Mode-space constrains possible transitions “Idle” ⇒ Yields call summary S ReqHandler ( � X h , � DiagCode X ′ h ) : =0x0000 ( h . DiagCode = 0 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0x8000 ) “Processing” ∧ ( h . DiagCode = 0x8000 → h . DiagCode ′ = 0 DiagCode =0x8000 ∨ h . DiagCode ′ = 0xC001 ) ∧ ( h . DiagCode = 0xC001 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0xC001 ) “Error” DiagCode =0xC001 ◮ Add to encoding of each call of ReqHandler 12 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Mode-Space as Call Summary ◮ Mode-space constrains possible transitions “Idle” ⇒ Yields call summary S ReqHandler ( � X h , � DiagCode X ′ h ) : =0x0000 ( h . DiagCode = 0 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0x8000 ) “Processing” ∧ ( h . DiagCode = 0x8000 → h . DiagCode ′ = 0 DiagCode =0x8000 ∨ h . DiagCode ′ = 0xC001 ) ∧ ( h . DiagCode = 0xC001 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0xC001 ) “Error” DiagCode =0xC001 ◮ Add to encoding of each call of ReqHandler 12 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Mode-Space as Call Summary ◮ Mode-space constrains possible transitions “Idle” ⇒ Yields call summary S ReqHandler ( � X h , � DiagCode X ′ h ) : =0x0000 ( h . DiagCode = 0 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0x8000 ) “Processing” ∧ ( h . DiagCode = 0x8000 → h . DiagCode ′ = 0 DiagCode =0x8000 ∨ h . DiagCode ′ = 0xC001 ) ∧ ( h . DiagCode = 0xC001 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0xC001 ) “Error” DiagCode =0xC001 ◮ Add to encoding of each call of ReqHandler 12 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Mode-Space as Call Summary ◮ Mode-space constrains possible transitions “Idle” ⇒ Yields call summary S ReqHandler ( � X h , � DiagCode X ′ h ) : =0x0000 ( h . DiagCode = 0 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0x8000 ) “Processing” ∧ ( h . DiagCode = 0x8000 → h . DiagCode ′ = 0 DiagCode =0x8000 ∨ h . DiagCode ′ = 0xC001 ) ∧ ( h . DiagCode = 0xC001 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0xC001 ) “Error” DiagCode =0xC001 ◮ Add to encoding of each call of ReqHandler 12 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Mode-Space as Call Summary ◮ Mode-space constrains possible transitions “Idle” ⇒ Yields call summary S ReqHandler ( � X h , � DiagCode X ′ h ) : =0x0000 ( h . DiagCode = 0 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0x8000 ) “Processing” ∧ ( h . DiagCode = 0x8000 → h . DiagCode ′ = 0 DiagCode =0x8000 ∨ h . DiagCode ′ = 0xC001 ) ∧ ( h . DiagCode = 0xC001 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0xC001 ) “Error” DiagCode =0xC001 ◮ Add to encoding of each call of ReqHandler 12 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Mode-Space as Call Summary ◮ Mode-space constrains possible transitions “Idle” ⇒ Yields call summary S ReqHandler ( � X h , � DiagCode X ′ h ) : =0x0000 ( h . DiagCode = 0 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0x8000 ) “Processing” ∧ ( h . DiagCode = 0x8000 → h . DiagCode ′ = 0 DiagCode =0x8000 ∨ h . DiagCode ′ = 0xC001 ) ∧ ( h . DiagCode = 0xC001 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0xC001 ) “Error” DiagCode =0xC001 ◮ Add to encoding of each call of ReqHandler 12 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Mode-Space as Call Summary ◮ Mode-space constrains possible transitions “Idle” ⇒ Yields call summary S ReqHandler ( � X h , � DiagCode X ′ h ) : =0x0000 ( h . DiagCode = 0 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0x8000 ) “Processing” ∧ ( h . DiagCode = 0x8000 → h . DiagCode ′ = 0 DiagCode =0x8000 ∨ h . DiagCode ′ = 0xC001 ) ∧ ( h . DiagCode = 0xC001 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0xC001 ) “Error” DiagCode =0xC001 ◮ Add to encoding of each call of ReqHandler 12 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Mode-Space as Call Summary Mode-Space as Call Summary ◮ Mode-space constrains possible transitions “Idle” ⇒ Yields call summary S ReqHandler ( � X h , � DiagCode X ′ h ) : =0x0000 ( h . DiagCode = 0 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0x8000 ) “Processing” ∧ ( h . DiagCode = 0x8000 → h . DiagCode ′ = 0 DiagCode =0x8000 ∨ h . DiagCode ′ = 0xC001 ) ∧ ( h . DiagCode = 0xC001 → h . DiagCode ′ = 0 ∨ h . DiagCode ′ = 0xC001 ) “Error” DiagCode =0xC001 ◮ Add to encoding of each call of ReqHandler 12 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Experiments Benchmarks ◮ Two groups of PLC programs from PLCopen Safety library • elementary modules implementing safety concepts (23 specs) • user examples composed of elementary ones (17 specs) ◮ Elementary modules exhibit mode-semantics via DiagCode ◮ We check invariants taken or derived from PLCopen ◮ CHC-solving via Z3’s Property Directed Reachability (PDR) 13 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Experiments Benchmarks ◮ Two groups of PLC programs from PLCopen Safety library • elementary modules implementing safety concepts (23 specs) • user examples composed of elementary ones (17 specs) ◮ Elementary modules exhibit mode-semantics via DiagCode ◮ We check invariants taken or derived from PLCopen ◮ CHC-solving via Z3’s Property Directed Reachability (PDR) 13 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Experiments Benchmarks ◮ Two groups of PLC programs from PLCopen Safety library • elementary modules implementing safety concepts (23 specs) • user examples composed of elementary ones (17 specs) ◮ Elementary modules exhibit mode-semantics via DiagCode ◮ We check invariants taken or derived from PLCopen ◮ CHC-solving via Z3’s Property Directed Reachability (PDR) 13 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Experiments Benchmarks ◮ Two groups of PLC programs from PLCopen Safety library • elementary modules implementing safety concepts (23 specs) • user examples composed of elementary ones (17 specs) ◮ Elementary modules exhibit mode-semantics via DiagCode ◮ We check invariants taken or derived from PLCopen ◮ CHC-solving via Z3’s Property Directed Reachability (PDR) 13 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Experiments Benchmarks ◮ Two groups of PLC programs from PLCopen Safety library • elementary modules implementing safety concepts (23 specs) • user examples composed of elementary ones (17 specs) ◮ Elementary modules exhibit mode-semantics via DiagCode ◮ We check invariants taken or derived from PLCopen ◮ CHC-solving via Z3’s Property Directed Reachability (PDR) 13 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Experiments Benchmarks ◮ Two groups of PLC programs from PLCopen Safety library • elementary modules implementing safety concepts (23 specs) • user examples composed of elementary ones (17 specs) ◮ Elementary modules exhibit mode-semantics via DiagCode ◮ We check invariants taken or derived from PLCopen ◮ CHC-solving via Z3’s Property Directed Reachability (PDR) 13 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

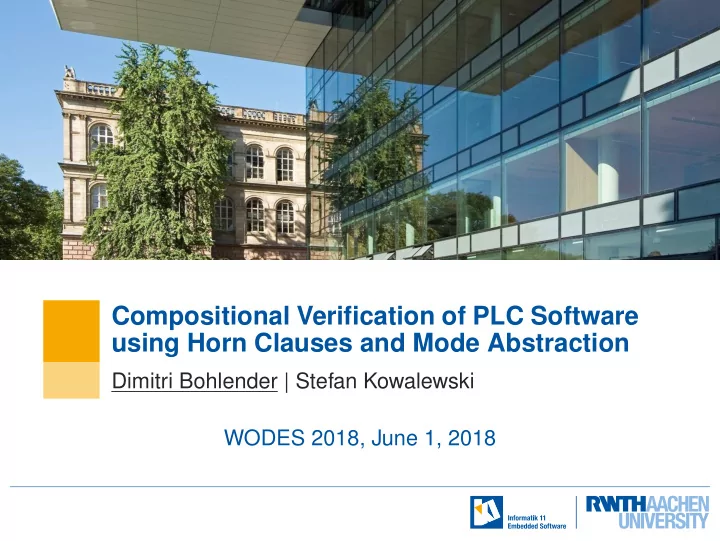

Introduction CHC-based Verification Conclusion Experiments Results 10 3 PDR + Mode Abstraction 10 2 10 1 10 0 10 0 10 1 10 2 10 3 PDR Figure: Time [s] spent on verification of each task 14 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Concluding Remarks Summary ◮ Logic control applications exhibit mode-semantics ◮ Mode-space contains global information ◮ Approximate mode-abstraction possible via VSA ◮ CHCs enable • compositional characterisation and reasoning • uniform characterisation of program, spec & abstraction ◮ Experiments suggest that • mode-abstraction may help significantly • overall, mode-abstraction overhead is negligble 15 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Concluding Remarks Summary ◮ Logic control applications exhibit mode-semantics ◮ Mode-space contains global information ◮ Approximate mode-abstraction possible via VSA ◮ CHCs enable • compositional characterisation and reasoning • uniform characterisation of program, spec & abstraction ◮ Experiments suggest that • mode-abstraction may help significantly • overall, mode-abstraction overhead is negligble 15 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Concluding Remarks Summary ◮ Logic control applications exhibit mode-semantics ◮ Mode-space contains global information ◮ Approximate mode-abstraction possible via VSA ◮ CHCs enable • compositional characterisation and reasoning • uniform characterisation of program, spec & abstraction ◮ Experiments suggest that • mode-abstraction may help significantly • overall, mode-abstraction overhead is negligble 15 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Concluding Remarks Summary ◮ Logic control applications exhibit mode-semantics ◮ Mode-space contains global information ◮ Approximate mode-abstraction possible via VSA ◮ CHCs enable • compositional characterisation and reasoning • uniform characterisation of program, spec & abstraction ◮ Experiments suggest that • mode-abstraction may help significantly • overall, mode-abstraction overhead is negligble 15 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Concluding Remarks Summary ◮ Logic control applications exhibit mode-semantics ◮ Mode-space contains global information ◮ Approximate mode-abstraction possible via VSA ◮ CHCs enable • compositional characterisation and reasoning • uniform characterisation of program, spec & abstraction ◮ Experiments suggest that • mode-abstraction may help significantly • overall, mode-abstraction overhead is negligble 15 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Concluding Remarks Summary ◮ Logic control applications exhibit mode-semantics ◮ Mode-space contains global information ◮ Approximate mode-abstraction possible via VSA ◮ CHCs enable • compositional characterisation and reasoning • uniform characterisation of program, spec & abstraction ◮ Experiments suggest that • mode-abstraction may help significantly • overall, mode-abstraction overhead is negligble 15 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Introduction CHC-based Verification Conclusion Concluding Remarks Summary ◮ Logic control applications exhibit mode-semantics ◮ Mode-space contains global information ◮ Approximate mode-abstraction possible via VSA ◮ CHCs enable • compositional characterisation and reasoning • uniform characterisation of program, spec & abstraction ◮ Experiments suggest that • mode-abstraction may help significantly • overall, mode-abstraction overhead is negligble 15 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Appendix References Related Work Related Tools & Techniques Mode-Abstraction: ◮ Predicate abstraction [GS97] ◮ Abstract-domain selection based on variable usage [Ape+13] Recent years: ◮ Decoupling Language Details from Verifier Implementations ◮ Modular structure & off-the-shelf components Intermediate Verification Language: ◮ B OOGIE [Lei08] • used by SMACK [RE14] • checked by C ORRAL [LQL12] ◮ Constrained Horn Clauses (CHCs) [Bjø+15] • used by S EA H ORN [Gur+15] • checked by S PACER [KGC14] or Z3 [MB08] 16 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Appendix References Typical Logic Control Applications PLCopen Safety Application SF_Equivalent SF_EmergencyStop InputDevice1_active Activate Ready Activate Ready S1_S_EStopIn_1 S_ChannelA S_EquivalentOut S_EStopIn S_EStopOut S_EStopOut Error_EStop1 S1_S_EStopIn_2 S_ChannelB Error Error_Equiv1 FALSE S_StartReset Error S_DiscrepancyTime DiagCode Diag_Equiv1 DiagCode Diag_EStop1 T#10ms FALSE S_AutoReset S0_Reset Reset SF_ESPE AND InputDevice2_active Activate Ready S2_S_ESPE_In S_ESPE_In S_ESPE_Out FALSE S_StartReset Error Error_ESPE1 DiagCode Diag_ESPE1 FALSE S_AutoReset S0_Reset Reset SF_SafeStop1 Ready Activate AND S_StopIn S_Stopped S_Stopped S_EStopOut AxisID_1 AxisID Error Error_SafeStop1 T#100ms MonitoringTime DiagCode Diag_SafeStop1 S3_Drive_Reset Reset Single Cycle 17 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Appendix References Typical Logic Control Applications Typical Block Specification !Activate Idle 0 DiagCode=0 1 Ready=FALSE Activate Ready=TRUE !S_ChannelNC 1 & S_ChannelNO !S_ChannelNC Init Error 3 1 DiagCode=0x8001 DiagCode=0xC003 S_ChannelNC & S_ChannelNO !S_ChannelNC 3 !S_ChannelNC & S_ChannelNO & S_ChannelNO e 2 m S_ChannelNO i T y d c e s n !S_ChannelNO a p p a e l & !S_ChannelNC r e c s 1 i 2 D 2 2 1 O C N & N O l l Error 1/2 C N e From Active l e N n Wait for NO Wait for NC e n l n DiagCode=0xC001 n n Wait e a n a DiagCode=0x8004 DiagCode=0x8014 n h a h | DiagCode=0xC002 n C DiagCode=0x8005 h C _ a _ C S h S _ C ! 1 1 _ S & S ! 3 3 DiscrepancyTime DiscrepancyTime S_ChannelNC elapsed elapsed S_AntivalentOut=FALSE S_AntivalentOut=TRUE 2 !S_ChannelNC | S_ChannelNO Safety Output !S_ChannelNO Enabled 1 DiagCode=0x8000 18 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Appendix References Encoding Details Intuition for Logical Characterisation ◮ Reason about program semantics by leveraging Satisfiability Modulo Theories (SMT) solving ⇒ Characterise semantics via first order logic formulae Condition Formula over the program’s variables � x > y + 1 � = x > y + 1 Statement Formula over pre- & post variables instances � x ′ = y + 1 � � y ′ = y � � x := y + 1 � = ∧ Procedure Predicate over pre- & post variables instances � � � x ≥ 0 → x ′ = x � � x < 0 → x ′ = − x � abs( x, x ′ ) = ∨ Unclear Characterisation of procedures with loops 19 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Appendix References Encoding Details Intuition for Logical Characterisation ◮ Reason about program semantics by leveraging Satisfiability Modulo Theories (SMT) solving ⇒ Characterise semantics via first order logic formulae Condition Formula over the program’s variables � x > y + 1 � = x > y + 1 Statement Formula over pre- & post variables instances � x ′ = y + 1 � � y ′ = y � � x := y + 1 � = ∧ Procedure Predicate over pre- & post variables instances � � � x ≥ 0 → x ′ = x � � x < 0 → x ′ = − x � abs( x, x ′ ) = ∨ Unclear Characterisation of procedures with loops 19 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Appendix References Encoding Details Intuition for Logical Characterisation ◮ Reason about program semantics by leveraging Satisfiability Modulo Theories (SMT) solving ⇒ Characterise semantics via first order logic formulae Condition Formula over the program’s variables � x > y + 1 � = x > y + 1 Statement Formula over pre- & post variables instances � x ′ = y + 1 � � y ′ = y � � x := y + 1 � = ∧ Procedure Predicate over pre- & post variables instances � � � x ≥ 0 → x ′ = x � � x < 0 → x ′ = − x � abs( x, x ′ ) = ∨ Unclear Characterisation of procedures with loops 19 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Appendix References Encoding Details Intuition for Logical Characterisation ◮ Reason about program semantics by leveraging Satisfiability Modulo Theories (SMT) solving ⇒ Characterise semantics via first order logic formulae Condition Formula over the program’s variables � x > y + 1 � = x > y + 1 Statement Formula over pre- & post variables instances � x ′ = y + 1 � � y ′ = y � � x := y + 1 � = ∧ Procedure Predicate over pre- & post variables instances � � � x ≥ 0 → x ′ = x � � x < 0 → x ′ = − x � abs( x, x ′ ) = ∨ Unclear Characterisation of procedures with loops 19 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Appendix References Encoding Details Intuition for Logical Characterisation ◮ Reason about program semantics by leveraging Satisfiability Modulo Theories (SMT) solving ⇒ Characterise semantics via first order logic formulae Condition Formula over the program’s variables � x > y + 1 � = x > y + 1 Statement Formula over pre- & post variables instances � x ′ = y + 1 � � y ′ = y � � x := y + 1 � = ∧ Procedure Predicate over pre- & post variables instances � � � x ≥ 0 → x ′ = x � � x < 0 → x ′ = − x � abs( x, x ′ ) = ∨ Unclear Characterisation of procedures with loops 19 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Appendix References Encoding Details Intuition for Logical Characterisation ◮ Reason about program semantics by leveraging Satisfiability Modulo Theories (SMT) solving ⇒ Characterise semantics via first order logic formulae Condition Formula over the program’s variables � x > y + 1 � = x > y + 1 Statement Formula over pre- & post variables instances � x ′ = y + 1 � � y ′ = y � � x := y + 1 � = ∧ Procedure Predicate over pre- & post variables instances � � � x ≥ 0 → x ′ = x � � x < 0 → x ′ = − x � abs( x, x ′ ) = ∨ Unclear Characterisation of procedures with loops 19 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Appendix References Encoding Details Encoding the Running Example Variables instances: ◮ � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � req ′ , in ′ , m ′ , h . data ′ , h . DiagCode ′ , h . res ′ , out ′ � X ′ = ◮ � Reachability facts & rules: 0 req && !m !(req && !m) ◮ Initial configuration reachable 1 4 init ( � X ) → p Main (0 , � X, 0 , � X ) h.data:=in ReqHandler( 2 ReqHandler( h.data, ◮ Transitive reachability h.data, h.DiagCode, h.DiagCode, h.res p Main ( l, � X, 1 , � X ′ ) h.res ) ) ∧ h . data ′′ = in ′ ∧ id ( X ′ \ � h . data ′ � 5 3 ) out:=h.res out:=h.res 6 → p Main ( l, � X, 2 , � X ′′ ) m:=req 7 20 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Appendix References Encoding Details Encoding the Running Example Variables instances: ◮ � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � req ′ , in ′ , m ′ , h . data ′ , h . DiagCode ′ , h . res ′ , out ′ � X ′ = ◮ � Reachability facts & rules: 0 req && !m !(req && !m) ◮ Initial configuration reachable 1 4 init ( � X ) → p Main (0 , � X, 0 , � X ) h.data:=in ReqHandler( 2 ReqHandler( h.data, ◮ Transitive reachability h.data, h.DiagCode, h.DiagCode, h.res p Main ( l, � X, 1 , � X ′ ) h.res ) ) ∧ h . data ′′ = in ′ ∧ id ( X ′ \ � h . data ′ � 5 3 ) out:=h.res out:=h.res 6 → p Main ( l, � X, 2 , � X ′′ ) m:=req 7 20 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Appendix References Encoding Details Encoding the Running Example Variables instances: ◮ � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � req ′ , in ′ , m ′ , h . data ′ , h . DiagCode ′ , h . res ′ , out ′ � X ′ = ◮ � Reachability facts & rules: 0 req && !m !(req && !m) ◮ Initial configuration reachable 1 4 init ( � X ) → p Main (0 , � X, 0 , � X ) h.data:=in ReqHandler( 2 ReqHandler( h.data, ◮ Transitive reachability h.data, h.DiagCode, h.DiagCode, h.res p Main ( l, � X, 1 , � X ′ ) h.res ) ) ∧ h . data ′′ = in ′ ∧ id ( X ′ \ � h . data ′ � 5 3 ) out:=h.res out:=h.res 6 → p Main ( l, � X, 2 , � X ′′ ) m:=req 7 20 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Appendix References Encoding Details Encoding the Running Example Variables instances: ◮ � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � req ′ , in ′ , m ′ , h . data ′ , h . DiagCode ′ , h . res ′ , out ′ � X ′ = ◮ � Reachability facts & rules: 0 req && !m !(req && !m) ◮ Initial configuration reachable 1 4 init ( � X ) → p Main (0 , � X, 0 , � X ) h.data:=in ReqHandler( 2 ReqHandler( h.data, ◮ Transitive reachability h.data, h.DiagCode, h.DiagCode, h.res p Main ( l, � X, 1 , � X ′ ) h.res ) ) ∧ h . data ′′ = in ′ ∧ id ( X ′ \ � h . data ′ � 5 3 ) out:=h.res out:=h.res 6 → p Main ( l, � X, 2 , � X ′′ ) m:=req 7 20 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Appendix References Encoding Details Encoding the Running Example Variables instances: ◮ � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � req ′ , in ′ , m ′ , h . data ′ , h . DiagCode ′ , h . res ′ , out ′ � X ′ = ◮ � Reachability facts & rules: 0 req && !m !(req && !m) ◮ Initial configuration reachable 1 4 init ( � X ) → p Main (0 , � X, 0 , � X ) h.data:=in ReqHandler( 2 ReqHandler( h.data, ◮ Transitive reachability h.data, h.DiagCode, h.DiagCode, h.res p Main ( l, � X, 1 , � X ′ ) h.res ) ) ∧ h . data ′′ = in ′ ∧ id ( X ′ \ � h . data ′ � 5 3 ) out:=h.res out:=h.res 6 → p Main ( l, � X, 2 , � X ′′ ) m:=req 7 20 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Appendix References Encoding Details Encoding the Running Example Variables instances: ◮ � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � req ′ , in ′ , m ′ , h . data ′ , h . DiagCode ′ , h . res ′ , out ′ � X ′ = ◮ � Reachability facts & rules: 0 req && !m !(req && !m) ◮ Initial configuration reachable 1 4 init ( � X ) → p Main (0 , � X, 0 , � X ) h.data:=in ReqHandler( 2 ReqHandler( h.data, ◮ Transitive reachability h.data, h.DiagCode, h.DiagCode, h.res p Main ( l, � X, 1 , � X ′ ) h.res ) ) ∧ h . data ′′ = in ′ ∧ id ( X ′ \ � h . data ′ � 5 3 ) out:=h.res out:=h.res 6 → p Main ( l, � X, 2 , � X ′′ ) m:=req 7 20 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Appendix References Encoding Details Encoding the Running Example Variables instances: ◮ � X = ( req , in , m, h . data , h . DiagCode , h . res , out ) � req ′ , in ′ , m ′ , h . data ′ , h . DiagCode ′ , h . res ′ , out ′ � X ′ = ◮ � Reachability facts & rules: 0 req && !m !(req && !m) ◮ Initial configuration reachable 1 4 init ( � X ) → p Main (0 , � X, 0 , � X ) h.data:=in ReqHandler( 2 ReqHandler( h.data, ◮ Transitive reachability h.data, h.DiagCode, h.DiagCode, h.res p Main ( l, � X, 1 , � X ′ ) h.res ) ) ∧ h . data ′′ = in ′ ∧ id ( X ′ \ � h . data ′ � 5 3 ) out:=h.res out:=h.res 6 → p Main ( l, � X, 2 , � X ′′ ) m:=req 7 20 / 15 Compositional Verification of PLC Software using CHCs and Mode Abstraction D. Bohlender | S. Kowalewski

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.