Chapter 2 Chapter 2 Electronics In In Out Out In Out The - PowerPoint PPT Presentation

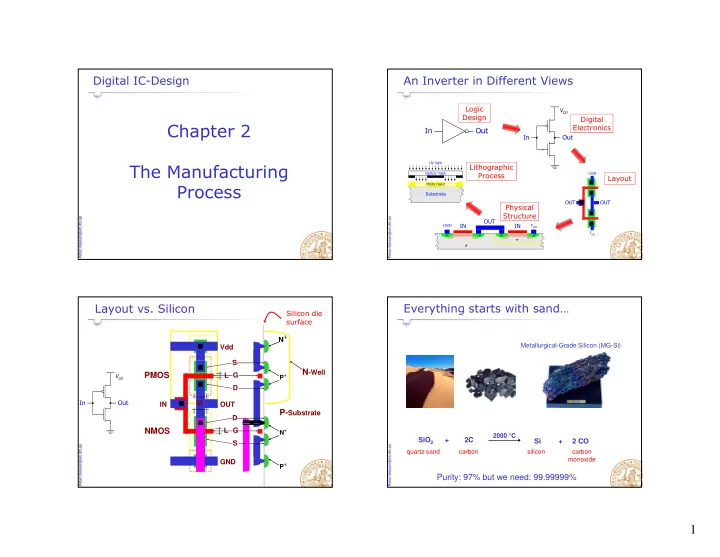

Digital IC-Design An Inverter in Different Views Logic V DD Design Digital Chapter 2 Chapter 2 Electronics In In Out Out In Out The Manufacturing UV light Lithographic Optical mask Process GND Layout Process Process Photo

Digital IC-Design An Inverter in Different Views Logic V DD Design Digital Chapter 2 Chapter 2 Electronics In In Out Out In Out The Manufacturing UV light Lithographic Optical mask Process GND Layout Process Process Photo resist Substrate OUT OUT Physical Structure OUT IN IN GND V DD V DD n + n + p + p + n - p - Layout vs. Silicon Everything starts with sand… Silicon die surface N + Metallurgical-Grade Silicon (MG-Si) Vdd S S N -Well PMOS P + L G V DD D In Out W IN OUT P- Substrate D N + NMOS L G 2000 °C SiO 2 + 2C Si + 2 CO S quartz sand carbon silicon carbon monoxide GND P + Purity: 97% but we need: 99.99999% 1

Fabrication Manufacturing: A Lithographic Process Wafer Processing Si - Ingot Si - Wafers Oxiation Masking/Patterning Etching Photographic glass plate Processed wafer Die Attach Wire Bonding Encapsulated IC (mask) Each layer is projected to the silicon die Manufacturing Process: Example Manufacturing Process: Simplified Etching Implantation of well regions Resist SiO 2 Substrate Substrate Deposit polysilicon D it l ili Si - Gate After etching & resist removal Implantation of heavy doped regions Photo resist Resist Silicon dioxide (SiO 2 ) SiO 2 - for Drain, source, and substrate/well contacts Substrate (Si) Si Creating windows for contacts and Creating windows for contacts and UV light UV light Optical mask vias Implant of heavily doped areas Resist SiO 2 SiO 2 Deposit metal Si Si Exposed resist 2

Wafer Stepper Intel use 30cm wafers Wafer in 90nm technology Light goes through Each mask is repeated mask the mask, lens and with a stepper the objective the objective For us: MPW - many designs share the same reticule Reticule lens Silicon dies objective (chips) after die sawing i wafer Optical Mask Optical Proximity Correction (OPC) Predistortion of the mask layout is needed when scaling down the technology Feature sizes are close to light OPC Corrections OPC Corrections wave lengths No OPC With OPC Diffraction phenomena have become a major problem Out of reach for the Out of reach for the Optics!!! Original Layout Mask correction is needed! Needed for 0.1 micron and less 3

Phase Shifting Masks (PSM) Clean room To keep the air clean of particles conventional mask phase shifting mask glass Phase shifter (glass) To much light for OK! the photo resist Clean Room Digital IC-Design Particles in the air • air in a city: 15 million -100 million Design Rules particles per ft 3 • air in the mountains: up to 10 million particles per ft 3 ft 3 air in a clean room for ICs: � 1 - 100 particles per ft 3 4

Design Rules Layer Representation Well Interface between designer and process Interface between designer and process Active A ti engineer Polysilicon Guidelines for constructing process Metal 1 masks Metal 2 Unit dimension: Minimum line width Contact to poly Contact to poly scalable design rules: λ -parameter scalable design rules: λ parameter absolute dimensions (micron rules) Contact to active Via (M1 to M2) Minimum Distance Rule (typ. 0.35 tech.) Minimum Width Rule (typical 0.35 tech) Active Poly M1 M1 Active Poly M1 M1 M2 M2 0.5 μ m 0.3 μ m 0.4 μ m 0.5 μ m 0.6 μ m 0.6 μ m 0.6 μ m 0.6 μ m 5

Transistor Rules (0.35 technology) Contact Rules (0.35 technology) Contacts have 0.5 μ m fixed size 0.3 μ m 0.6 μ m 0.4 μ m 0.4 μ m 0 4 μ m ( (0.4 2 ) ) 0.4 μ m 1.0 μ m 0.3 μ m 0.5 μ m 0.6 μ m 0.4 μ m 0.6 μ m μ 1.0 μ m 0.4 μ m 0.7 μ m 0 7 m 0.7 μ m 0 7 m Contact to active 0.7 μ m 0.5 μ m Contact to poly Note that the minimum transistor width is wider 0.9 μ m Via (Metal 1 to Metal 2) than the minimum active width (0.5 μ m) Layout Editor Design Rule Checker (DRC) Polysilicon to y close to active! 6

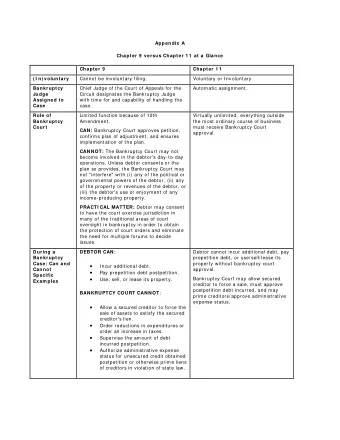

Packaging Flip-Chip Bonding Packaging follows after fabrication Solder Bumps Bonding Bonding Pads Pads Core Core Die upside down Die upside down Inter- wire connect Silicon layer die Die Substrate Bonding everywhere even inside the core Bonding on the border around the core Some Package Types Packages add Parasitics DIP Dual in line Package Bonded Silicon Die Package Package Capacitance (pF) Capacitance (pF) Inductance (nH) Inductance (nH) 68 Pin Plastic DIP 4 35 Wafer 68 Pin Ceramic DIP 7 20 256 Pin Grid Array 5 15 PGA Bond Wire 1 1 Pin Grid Solder Bump Solder Bump 0 5 0.5 0.1 0 1 Array PLCC Source: Sze 7

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.