Channel Replacements Li Wu April 2, 2009 Outline: Introduction - PowerPoint PPT Presentation

CMOS Extension-III-V Channel Replacements Li Wu April 2, 2009 Outline: Introduction III-V Compound Semiconductor Advantages III-V Compound Semiconductor Challenges Recent Progress Conclusion Introduction : In order to

CMOS Extension-III-V Channel Replacements Li Wu April 2, 2009

Outline: Introduction III-V Compound Semiconductor Advantages III-V Compound Semiconductor Challenges Recent Progress Conclusion

Introduction : In order to sustain Moore’s law alive, it will require not only shrink the transistor dimensions, but also introduce new materials and new device architecture to achieve the highest performance per watt of power consumption. There has been a lot of interest in III-V compound semiconductor.

III-V Compound Semiconductor Advantages Low Energy Dissipation High Electron Mobility Low Energy Delay Product

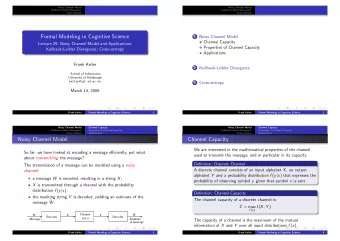

1. Low Energy Dissipation In Fig. 1 left, there is a reduction in the switching energy of individual silicon. the total number of electrons participating in the energy event is reduced dramatically Figure 1: Transistor switching energy plotted as a function of physical gate length

There is a an increase in device power density per unit area, as shown in Fig 2. Figure 2: Individual transistor switching power density plotted as a function of physical gate length.

Enhancement mode n-channel InSb quantum well transistors were demonstrated with unity gain cutoff frequency, fT, exceeding 300 GHz at an operating voltage of only 0.5V .

2. High Electron Mobility As shown in Fig. 4. For a given electric field, III-V materials can have higher velocity compared to Silicon. Also, the equal velocity can be achieved at a lower applied voltage for III- V materials. Figure 4: Electron drift velocity vs electric field for various semiconductors

Table 1 above shows more in detail, of all these non-Si materials, III-V is the most mature and practical, having been used in commercial communication and optoelectronic products. Among the III-V systems of interest, InSb has the highest electron mobility of 30,000 cm/(V*s), while Si has electron mobility of 600 cm/(V*s).

Low Energy Delay Product Energy delay product Which represents the energy efficiency of the transistor Though silicon CMOS often have the ability to trade energy for performance, it is quite difficult to improve both energy and performance simultaneously.

Figure 5 : Normalized energy-delay product of n- channel InSb and InGaAs quantum- well transistors compared with that of standard silicon MOSFET

III-V Compound Semiconductor Challenges III-V materials do not have an effective gate stack solution. III-V substrates are expensive, brittle, and difficult to make in large sizes. III-V materials do not have a superior hole mobility compared to Si

III-V materials do not have an effective gate stack solution. Unlike Silicon, the native oxides of III-Vs have very poor electrical properties. Currently all III-V QW devices use a direct Schottky metal gate, which results in a large parasitic gate leakage. Despite some progress in recent years, the problem of forming a high-quality gate insulator remains a significant barrier to implementing III-V for CMOS applications.

III-V substrates are expensive, brittle, and difficult to make in large sizes. From an economics point of view, the success of any future CMOS technology with non-Si channels will depend on its compatibility with the existing Si manufacturing infrastructure. Therefore, methods need to be developed to integrate III-V channels on Si substrates.

III-V materials do not have a superior hole mobility compared to Si. Table 2: Mobility of electrons and holes in priciple semiconductor

III-Vs still have the net mobility advantage over Si for CMOS application due to their much higher electron mobility, and lightly lower or comparable hole mobility, as shown in table 2.

A better integration scheme is to utilize III- V for the NFET and Ge for the p-channel transistor due to the high hole mobility of Ge, as shown in Fig 6. Figure 6: Ultimate CMOS structure composed of the combination of III-V semiconductors n-MOSFETs and Ge p-MOSFET on insulator

Recent Progress: High performance depletion-mode InSb and InGaAs QW transistors have been fabricated on silicon substrates. Hole mobility has been improved in III-V material systems using bi-axial strain, with hole mobility of >1000 cm/(V*s) .

Atomic Layer Deposition (ALD) high-K gate dielectrics have been deposited on InGaAs substrate with encouraging results. Figure 7: Gate to channel leakage characteristics for Al2O3 high-k dielectric and Al metal gate stack on AlInSb/InSb device layers showing reduction in leakage compared to Schottky metal gate

Conclusion: In conclusion, as the end of Si CMOS scaling is clearly in sight, III-V compound semiconductors have received renewed attention as the channel materials for future generation CMOS applications due to their high bulk electron mobility.

However, in order to implement III-Vs in manufacturing CMOS technology, we have to overcome the challenges. Although we are still far away from solving all the technical issues, all these research results are important milestones. They will help drive towards the goal of making III-V on silicon practical for future high speed and ultra-low power digital applications .

References: 1. International technology roadmap for semiconductors 2007_ERD 2. “III -V field-effect transistors for low power digital logic applications”, by Suman Datta 3. “Boolean logic and alternative information - processing devices” by George Bourianoff , Joe E. Brewer, Ralph Cavin, James A. Hutchby, and Victor Zhirnov 4. http://en.wikipedia.org/wiki/Main_Page

Thank you!

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.