Boolean Arithmetic Foundations of Global Networked Computing: - PowerPoint PPT Presentation

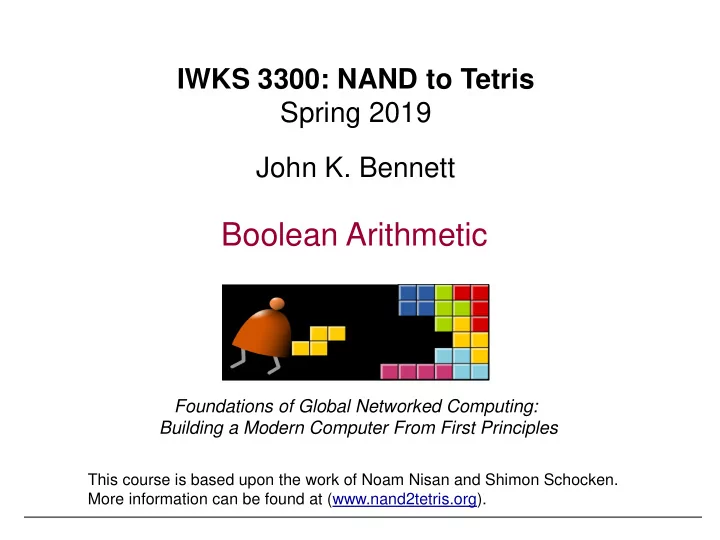

IWKS 3300: NAND to Tetris Spring 2019 John K. Bennett Boolean Arithmetic Foundations of Global Networked Computing: Building a Modern Computer From First Principles This course is based upon the work of Noam Nisan and Shimon Schocken. More

IWKS 3300: NAND to Tetris Spring 2019 John K. Bennett Boolean Arithmetic Foundations of Global Networked Computing: Building a Modern Computer From First Principles This course is based upon the work of Noam Nisan and Shimon Schocken. More information can be found at (www.nand2tetris.org).

Counting Systems quant ntity ty decimal mal binary ary 3-bit register ter 0 0 000 1 1 001 2 10 010 3 11 011 4 100 100 5 101 101 6 110 110 7 111 111 8 1000 overflow 9 1001 overflow 10 1010 overflow

Number Representation Base 10: 3 2 1 0 ( 9038 ) 9 1 0 0 1 0 3 1 0 8 1 0 9038 ten Base 2: 4 3 2 1 0 ( 10011 ) 1 2 0 2 0 2 1 2 1 2 19 two General Case: n i ( x x ... x ) x b n n 1 0 b i i 0

Binary Representation of Numeric Values Sign Magnitude Sign Magnitude (e.g., -2 = 1010) 1 1 0 0 0 1 1 = 3 One’s Complement + 1 0 1 0 = -2 (invert: e.g., -2 = 1101) Two’s Complement = -5 1 1 0 1 (invert and add 1: e.g., -2 = 1101) Two zeros: 0 != -0 Two ’ s Complement One’s Complement 1 1 1 0 0 0 1 1 = 3 0 0 1 + 1 1 1 0 = -2 0 0 1 1 = 3 + 1 1 0 1 = -2 = 1 0 0 0 1 = -1 1 1 1 0 Only one zero: 0 = -0 Two zeros: 0 != -0 Invertible: --n = n

Representing 2 ’ s Complement Negative Numbers (4-bit system) The representation of all positive numbers 0 0000 0000 -0 begins with a “0” 1 0001 1111 -1 The representation of all negative numbers 2 0010 1110 -2 begins with a “1“ 3 0011 1101 -3 To convert a two’s comp. number: 4 0100 1100 -4 Inside CPU : complement number and 5 0101 1011 -5 add 1 (easy to do with full adders) On Paper : leave all trailing 0’s and first 6 0110 1010 -6 1 from right intact, then flip all the 7 0111 1001 -7 remaining bits moving left Example: 2 - 5 = 2 + (-5) = 0 0 1 0 + 1 0 1 1 1 1 0 1 = -3

Overflow in 2 ’ s Complement Binary Addition Assuming 4-bit numbers (3 bits plus sign): 1 1 1 1 0 0 0 1 1 0 1 1 1 0 0 1 = -7 = -5 + + 0 1 1 1 = 7 0 1 0 1 = 5 = 2 = -2 0 0 1 0 1 1 1 0 No overflow Overflow (but we don ’ t care) How it works: Like decimal addition 0 1 1 1 When signs are opposite, 0 1 0 1 = 5 carry into or out of sign bit + 0 1 1 1 = 7 can be ignored When signs are the same, = -4 1 1 0 0 carry into sign bit (that Overflow (we do care) changes sign) indicates overflow (that must be handled)

Building an Adder chip 16 a 16 16-bit out 16 adder b Adder: a chip designed to add two (two ’ s comp.) integers Proposed implementation: Half adder: designed to add 2 bits Full adder: designed to add 3 bits Adder: designed to add two n -bit numbers.

Half adder (designed to add 2 bits) sum carry a b 0 0 0 0 sum a half 0 1 1 0 adder b carry 1 0 1 0 1 1 0 1 Implementation: based on two gates that you ’ ve seen before.

How To Build A Half Adder Truth table for Half Adder ∑ A B A XOR B (A + B) Cout 0 0 0 0 0 0 1 1 1 0 1 0 1 1 0 1 1 0 0 1 A B Half Adder ?? ∑ Cout

How To Build A Half Adder Truth table for XOR and Half Adder ∑ A B A XOR B (A + B) Cout A AND B 0 0 0 0 0 0 0 1 1 1 0 0 1 0 1 1 0 0 1 1 0 0 1 1 A B ∑ = A XOR B Half Adder Cout = A AND B ∑ Cout

Full adder (designed to add with carry in) carry a b c sum 0 0 0 0 0 0 0 1 1 0 a sum 0 1 0 1 0 full b 0 1 1 0 1 adder carry c 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 Implementation: based on half-adder gates.

Implementation of Full Adder Truth table for Full Adder ∑ Cin A B Cout 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 B Cin A 0 1 1 0 1 Full Adder 1 0 0 1 0 ∑ 1 0 1 0 1 Cout 1 1 0 0 1 1 1 1 1 1

How To Build A Full Adder A B Cin Truth table for Full Adder A 1 B 1 ∑ 1 ∑ Cin A B Cout 1 Cout 2 Cout Half Adder 0 0 0 0 0 0 0 0 ∑ 1 Cout 1 0 0 1 1 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 0 1 0 0 1 1 0 0 0 0 0 1 0 B 2 A 2 1 0 1 1 0 1 0 1 Half Adder 1 1 0 1 0 1 0 1 ∑ 2 Cout 2 1 1 1 0 1 0 1 1 ∑ ?? Cout

How To Build A Full Adder A B Cin Truth table for Full Adder A 1 B 1 ∑ 1 ∑ Cin A B Cout 1 Cout 2 Cout Half Adder 0 0 0 0 0 0 0 0 ∑ 1 Cout 1 0 0 1 1 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 0 1 0 0 1 1 0 0 0 0 0 1 0 B 2 A 2 1 0 1 1 0 1 0 1 Half Adder 1 1 0 1 0 1 0 1 ∑ 2 Cout 2 1 1 1 0 1 0 1 1 ∑ Cout

n -bit Adder (designed to add two 16-bit numbers) 16 a 16 16-bit out 16 adder b ... 1 0 1 1 a + 0 0 1 0 b … … 1 1 0 1 out Simple Implementation: series of full-adder gates.

Chained Carry Adder Chained carry makes addition time approximately equal to number of bits times the propagation delay of a Full Adder A B Cin A B Cin A B Cin Full Adder Full Adder Full Adder ∑ ∑ ∑ Cout Cout Cout Full adder prop. delay = 3 gpd (carry output) So a 16 bit adder would take 48 gpd to complete add

Carry Look Ahead Basics If we understand how carry works we can compute carry in advance. This is called “ Carry Look-Ahead. ” For any bit position, if A = 1 and B = 1; Cout = 1, i.e., a carry will be generated to the next bit position, regardless of value of Cin . This is called “ Carry Generate ” For any bit position, if one input is 1 and the other input is 0; Cout will equal Cin (i.e., the value of Cin will be propagated to the next bit position. This is called “ Carry Propagate ” For any bit position, if A = 0 and B = 0; Cout will equal 0, regardless of value of Cin . This is called “ Carry Stop. ” A B Cin A B Cin A B Cin Full Adder Full Adder Full Adder ∑ ∑ ∑ Cout Cout Cout

Carry Generate, Propagate and Stop Truth table for Full Adder ∑ Cin A B Cout f gps f gps 0 0 0 x CS i f gps 0 1 1 x CP i f gps 1 0 1 x CP i A B Cin f gps 1 1 0 x CG i Full Adder ∑ Cout X No need for carry chain

Carry Look Ahead Basics The equations to compute Cin at Bit Position i are as follows: Cin i = Cg i-1 + Cp i-1 ● Cg i-2 + Cp i-1 ● Cp i-2 ● Cg i-3 … + Cp i-1 ● Cp i-2 … Cp 1 ● Cg 0

Practical Considerations Very wide (more than 8 input) gates are impractical, so we would likely use a log n depth tree of gates to implement the wide ANDs and ORs. This is still faster than chained carry, even for 16 bits (and is much faster for 32 or 64 bit adders). Cin i = Cg i-1 + Cp i-1 ● Cg i-2 + Cp i-1 ● Cp i-2 ● Cg i-3 … + Cp i-1 ● Cp i-2 … Cp 1 ● Cg 0

Practical Implementation Note Use Cin 0 to add one (for example, when inverting the sign of a two ’ s complement number). Cin 0 then becomes a control signal that can be turned on by the control part of the microprocessor. A B Cin Full Adder ∑ Cout

The ALU (of the Hack platform) 16 a sum x a sum 16 half 16-bit full b out adder 16 adder adder b carry carry y c no zx nx zy ny f out(x, y, control bits ) = x+y, x-y, y – x, 0, 1, -1, x 16 bits x, y, -x, -y, ALU out 16 bits y !x, !y, 16 bits x+1, y+1, x-1, y-1, x&y, x|y zr ng

ALU logic (Hack platform) Implementation: build a logic gate architecture that “ executes ” the control bit “ instructions ” : if zx==1 then set x to 0 (bit-wise), etc.

ALU Details – How might we build this?

Example: How Do We Get “ -x ”

Example: How Do We Get “ -x ” out of ALU 1111 1111 1111 1 x = x (assume x = 4) = 0000 0000 0000 0100 y = !0 = 1111 1111 1111 1111 f = !(x+y); x+y = 0000 0000 0000 0011 !(x+y) = 1111 1111 1111 1100 1111111111111100 = - 4 (two’s complement)

Straightforward ALU Implementation zx nx zy ny f no x x 16 bits ALU out 16 bits y 16 bits 0 zr ng zx nx y + f 0 no (zr and zg impl. not shown) zy ny How could this design be improved?

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.