1 The Translation The Translation Lookaside Lookaside Buffer (TLB) - PDF document

Review: the Program and the Process VAS Review: the Program and the Process VAS BSS Process text segment Block Started by Symbol is initialized directly (uninitialized global data) e.g., heap and sbuf go here. from program text header

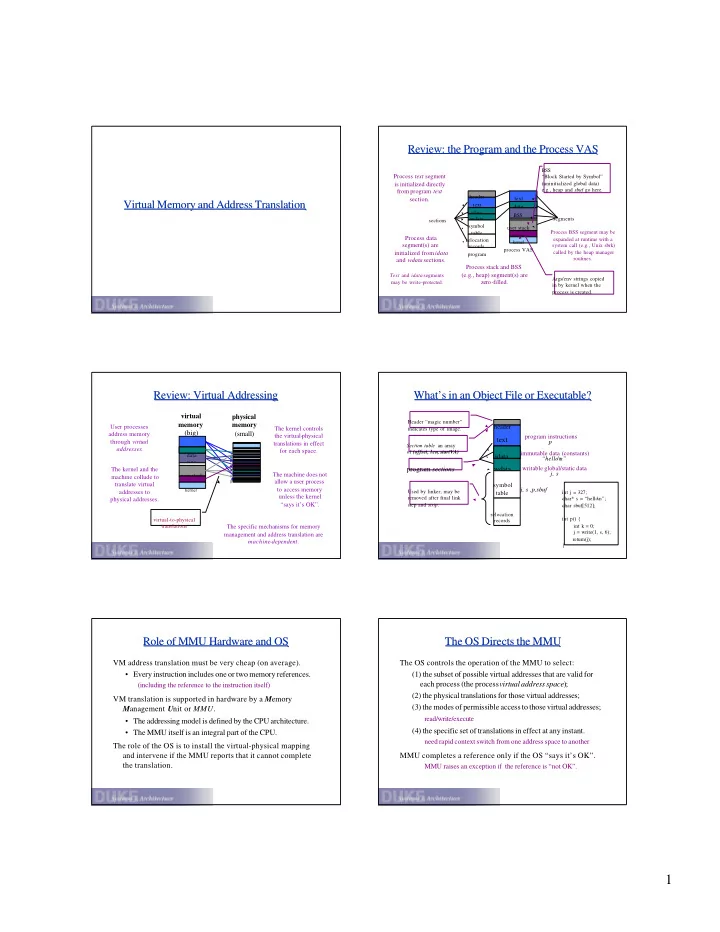

Review: the Program and the Process VAS Review: the Program and the Process VAS BSS Process text segment “Block Started by Symbol” is initialized directly (uninitialized global data) e.g., heap and sbuf go here. from program text header section. text Virtual Memory and Address Translation Virtual Memory and Address Translation text data data idata data BSS wdata segments sections symbol user stack Process BSS segment may be table args/env Process data expanded at runtime with a relocation kernel segment(s) are system call (e.g., Unix sbrk) records process VAS called by the heap manager initialized from idata program routines. and wdata sections. Process stack and BSS (e.g., heap) segment(s) are Text and idata segments Args/env strings copied zero-filled. may be write-protected. in by kernel when the process is created. Review: Virtual Addressing Review: Virtual Addressing What’s in an Object File or Executable? What’s in an Object File or Executable? virtual physical Header “magic number” memory memory User processes header The kernel controls indicates type of image. (big) address memory (small) the virtual- physical program instructions text through virtual p translations in effect Section table an array text addresses . for each space. of (offset, len, startVA) immutable data (constants) data data idata data “hello\n” BSS The kernel and the program sections wdata writable global/static data j, s The machine does not user stack machine collude to allow a user process translate virtual args/env symbol to access memory j, s ,p,sbuf kernel addresses to Used by linker; may be int j = 327; table unless the kernel removed after final link physical addresses. char* s = “hello \n”; “says it’s OK”. step and strip . char sbuf[512]; relocation int p() { virtual-to-physical records translations The specific mechanisms for memory int k = 0; j = write(1, s, 6); management and address translation are return(j); machine-dependent . } Role of MMU Hardware and OS Role of MMU Hardware and OS The OS Directs the MMU The OS Directs the MMU VM address translation must be very cheap (on average). The OS controls the operation of the MMU to select: • Every instruction includes one or two memory references. (1) the subset of possible virtual addresses that are valid for each process (the process virtual address space ); (including the reference to the instruction itself) (2) the physical translations for those virtual addresses; VM translation is supported in hardware by a M emory (3) the modes of permissible access to those virtual addresses; M anagement U nit or MMU . read/write/execute • The addressing model is defined by the CPU architecture. (4) the specific set of translations in effect at any instant. • The MMU itself is an integral part of the CPU. need rapid context switch from one address space to another The role of the OS is to install the virtual-physical mapping and intervene if the MMU reports that it cannot complete MMU completes a reference only if the OS “says it’s OK”. the translation. MMU raises an exception if the reference is “not OK”. 1

The Translation The Translation Lookaside Lookaside Buffer (TLB) Buffer (TLB) Care and Feeding of Care and Feeding ofTLBs TLBs An on-chip hardware translation buffer (TB or TLB) caches The OS kernel carries out its memory management functions by issuing privileged operations on the MMU. recently used virtual-physical translations (ptes). Alpha 21164: 48-entry fully associative TLB. Choice 1 : OS maintains page tables examined by the MMU. A CPU pipeline stage probes the TLB to complete over 99% • MMU loads TLB autonomously on each TLB miss of address translations in a single cycle. • page table format is defined by the architecture Like other memory system caches, replacement of TLB • OS loads page table bases and lengths into privileged memory management registers on each context switch. entries is simple and controlled by hardware. e.g., Not Last Used Choice 2 : OS controls the TLB directly. If a translation misses in the TLB, the entry must be fetched • MMU raises exception if the neededpte is not in the TLB. by accessing the page table(s) in memory. • Exception handler loads the missing pteby reading data structures in memory ( software-loaded TLB ). cost: 10-500 cycles A Simple Page Table A Simple Page Table Page Tables (2) Page Tables (2) Second-level page tables Each process/VAS has process page table its own page table. PFN 0 PFN 1 Virtual addresses are Top-level translated relative to page table the current page table. PFN i In this example, each VPN j maps to PFN j , PFN i + but in practice any offset physical frame may be used for any virtual page. page #i offset user virtual address The page tables are physical memory themselves stored in 32 bit address with 2 page table fields page frames memory; a protected Two-level page tables register holds a pointer to [fromTanenbaum ] the current page table. Alpha Page Tables (Forward Mapped) Alpha Page Tables (Forward Mapped) A Page Table Entry (PTE) A Page Table Entry (PTE) L1 L2 L3 PO This is (roughly) what a MIPS/Nachos 21 page table entry (pte) looks like. valid bit : OS uses this bit to tell the seg 0/1 10 10 10 13 MMU if the translation is valid. sparse 64-bit address space base write-enable : OS touches this to enable or (43 bits in 21064 and 21164) + disable write access for this mapping. + PFN + three-level page table dirty bit : MMU sets this when a store is offset at each level is (forward-mapped) completed to the page (page is modified). determined by specific bits in VA PFN reference bit : MMU sets this when a reference is made through the mapping. 2

Page Tables (3) Page Tables (3) Virtual Address Translation Virtual Address Translation virtual address 29 0 13 Example : typical 32-bit 00 VPN offset architecture with 8KB pages. Virtual address translation maps a virtual page number (VPN) to a physical page frame number (PFN): address the rest is easy. translation Deliver exception to OS if translation is not valid and accessible in requested mode. Typical page table entry [from Tanenbaum ] physical address { + PFN offset What You Should Know What You Should Know Background Background • Basics of paged memory management The remaining slides provide background from CPS 110. Be sure you understand why page-based memory allocation is more • Typical address space layout memory-efficient than the old way: allocating contiguous physical • Basics of address translation memory for each address space ( partitioning ). • Architectural mechanisms to support paged memory • Two partitioning strategies: fixed and variable • Importance for kernel protection and process isolation • How to make partitioning transparent to programs • Why the simple page table is inadequate • How to protect memory in a partitioned system • Motivation for and structure of hierarchical tables • Fragmentation: internal and external • Fragmentation issues for each strategy • Motivation for and structure of hashed (inverted) tables • Relevance to heap managers today • Approaches to variable partitioning: First fit, best fit, etc., and the role of compaction. Memory Management 101 Memory Management 101 Memory and Multiprogramming Memory and Multiprogramming Once upon a time ...memory was called “core”, and programs One day, IBM decided to load multiple jobs in memory at (“jobs”) were loaded and executed one by one. once. • improve utilization of that expensive CPU • load image in contiguous physical memory • improve system throughput start execution at a known physical location allocate space in high memory for stack and data Problem 1 : how do programs address their memory space? load-time relocation? • address text and data using physical addresses prelinkexecutables for known start address Problem 2 : how does the OS protect memory from rogue programs? • run to completion ??? 3

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.