1 Load Word Kodas som 16 bitars jump offset fr att ange hur mnga - PDF document

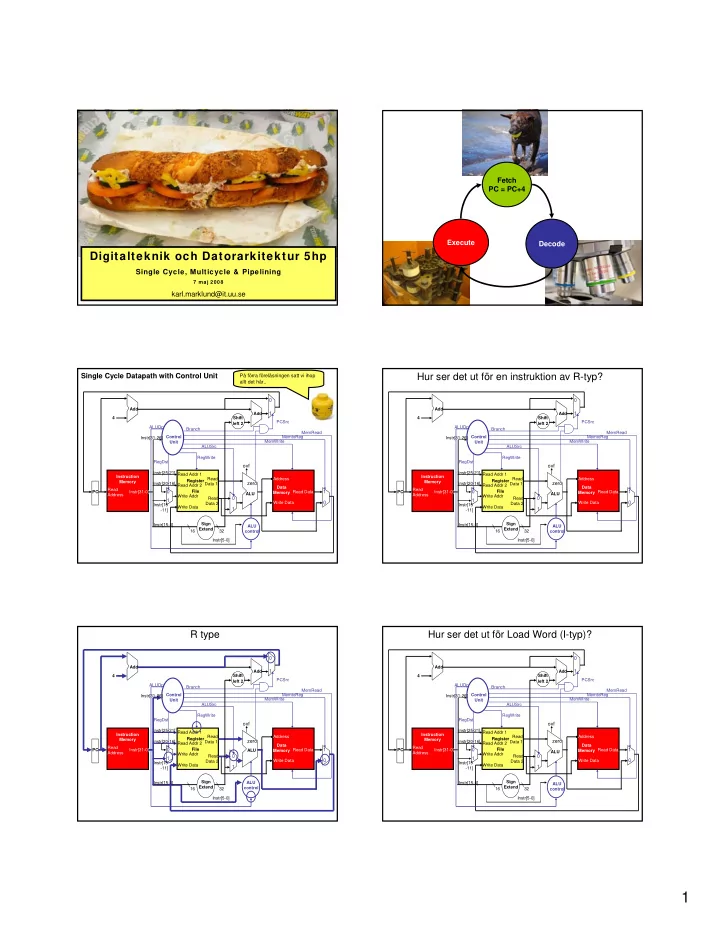

Fetch PC = PC+4 Execute Decode Digitalteknik och Datorarkitektur 5hp Single Cycle, Multicycle & Pipelining 7 maj 2008 karl.marklund@it.uu.se Single Cycle Datapath with Control Unit Hur ser det ut fr en instruktion av R-typ? P

Fetch PC = PC+4 Execute Decode Digitalteknik och Datorarkitektur 5hp Single Cycle, Multicycle & Pipelining 7 maj 2008 karl.marklund@it.uu.se Single Cycle Datapath with Control Unit Hur ser det ut för en instruktion av R-typ? På förra föreläsningen satt vi ihop allt det här.. 0 0 Add Add Add 1 Add 1 4 Shift 4 Shift PCSrc PCSrc left 2 left 2 ALUOp ALUOp Branch Branch MemRead MemRead Control MemtoReg Control MemtoReg Instr[31-26] Instr[31-26] MemWrite MemWrite Unit Unit ALUSrc ALUSrc RegWrite RegWrite RegDst RegDst ovf ovf Instr[25-21] Instr[25-21] Read Addr 1 Read Addr 1 Instruction Instruction Read Address Read Address Memory Register Memory Register zero zero Instr[20-16] Data 1 Instr[20-16] Data 1 Read Addr 2 Read Addr 2 Data Data Read Read 0 File 1 0 File 1 PC Instr[31-0] Read Data PC Instr[31-0] Read Data Memory Memory Address ALU Address ALU Write Addr Write Addr Read 0 Read 0 1 1 Write Data 0 Write Data 0 Data 2 Data 2 Instr[15 Instr[15 Write Data Write Data 1 1 -11] -11] Sign Sign Instr[15-0] Instr[15-0] ALU ALU Extend Extend 16 32 control 16 32 control Instr[5-0] Instr[5-0] R type Hur ser det ut för Load Word (I-typ)? 0 0 Add Add 1 1 Add Add 4 Shift 4 Shift PCSrc PCSrc left 2 left 2 ALUOp ALUOp Branch Branch MemRead MemRead Control MemtoReg Control MemtoReg Instr[31-26] Instr[31-26] MemWrite MemWrite Unit Unit ALUSrc ALUSrc RegWrite RegWrite RegDst RegDst ovf ovf Instr[25-21]` Instr[25-21] Read Addr 1 Read Addr 1 Instruction Instruction Read Address Read Address Register Register Memory Memory Instr[20-16] Data 1 zero Instr[20-16] Data 1 zero Read Addr 2 Read Addr 2 Data Data Read Read PC Instr[31-0] 0 File Read Data 1 PC Instr[31-0] 0 File Read Data 1 ALU Memory Memory ALU Address Address Write Addr Write Addr 0 0 Read Read 1 1 Write Data 0 Write Data 0 Data 2 Data 2 Instr[15 Instr[15 Write Data Write Data 1 1 -11] -11] Sign Sign Instr[15-0] ALU Instr[15-0] ALU Extend control Extend 16 32 16 32 control Instr[5-0] Instr[5-0] 1

Load Word Kodas som 16 bitars jump offset för att ange hur många instruktioner vi skall 0 hoppa (framåt eller bakåt) Add Add 1 4 Shift PCSrc left 2 ALUOp Branch MemRead Control MemtoReg beq $t1, $t2 my_label Instr[31-26] Unit MemWrite ALUSrc RegWrite RegDst ovf Instr[25-21]` Read Addr 1 Instruction Read Address Register Memory zero Instr[20-16] Data 1 Read Addr 2 Data Read 0 File 1 PC Instr[31-0] ALU Memory Read Data Hur funkar Address Write Addr Read 0 1 0 Write Data Data 2 Instr[15 branch- Write Data 1 -11] instruktioner... Sign Instr[15-0] ALU Extend control 16 32 Instr[5-0] Branch on Equal (beq) På förra föreläsningen byggde vi en datapath i Logisim som klarade av add , addi och sub . 0 Add Add 1 4 Shift PCSrc left 2 ALUOp Branch MemRead Control MemtoReg Instr[31-26] MemWrite Unit addi $t0, $zero, 127 ALUSrc addi $t1, $zero, 3 RegWrite RegDst add $t2, $t0, $t1 ovf Instr[25-21]` Read Addr 1 add $t3, $t2, $t2 Instruction Read Address Memory Register zero Instr[20-16] Data 1 sub $t4, $t3, $t1 Read Addr 2 Data Read 0 File 1 PC Instr[31-0] ALU Read Data Memory Address Write Addr Read 0 1 Write Data 0 Data 2 Write Data Instr[15 1 -11] Sign Instr[15-0] ALU Begränsade oss till stöd för program Extend control 16 32 liknande detta. Instr[5-0] Single cycle design – fetch, decode and execute each instructions in one clock cycle State State Combinational element element Logic 1 3 2 clock one clock cycle No datapath resource can be used more than once per instruction , so some must be duplicated (e.g., separate Instruction Memory and Data Memory, several adders) Fetch PC = PC+4 Cycle time is determined by length of the longest path Execute Decode Foto: C.E. Delohery some rights reserved 2

NOTE: this is a single-cycle implementation Easy to Single Cycle Disadvantages & Advantages understand Clock Cycle time must be long enough for the longest possible path and implement . A god candidate for the May be waste of area since some longest path? functional units (e.g., adders) must be duplicated since they can not be shared We are on during a clock cycle our way to Load Word implement R-type instructions a single such as add etc only uses four functional cycle Uses the clock cycle inefficiently – the Uses five functional units: datapath units: clock cycle must be timed to for MIPS in 1. Instruction memory accommodate the slowest instruction -- 1. Instruction memory Logisim. especially problematic for more complex 2. Register file 2. Register file instructions like floating point multiply. What about 3. ALU 3. ALU Store Word? 4. Data memory Cycle 1 Cycle 2 4. Register file Clk 5. Register file lw add Waste Foto: Fort Photo some rights reserved Multicycle Datapath Approach Not part of the ISA (Instruction Multicycle Datapath Set Architecture) Break up instructions into steps Approach: let an instruction take • At the end of a cycle where each step takes a cycle more than 1 clock cycle to while trying to: – Store values needed in a later cycle by the current instruction in an internal register (not visible to the programmer). All (except IR) complete. hold data only between a pair of adjacent clock cycles (no write Balance the amount of work to be control signal needed) done in each step. Restrict each cycle to use only one major functional unit. IR Memory PC Read Addr 1 A Address Read Register ALUout Read Addr 2 Data 1 Read Data File ALU (Instr. or Data) Write Addr Read B Write Data MDR Data 2 Write Data – IR – Instruction Register MDR – Memory Data Register In addition to faster clock rates, multicycle allows � – A, B – regfile read data registers ALUout – ALU output functional units that can be used more than once per Not every register instruction as long as they are used on different clock Parf of the ISA instruction takes cycles, as a result only need one memory – but only one the same number of – Data used by subsequent instructions are stored in programmer memory access per cycle need only one ALU/adder – clock cycles . visible registers (i.e., register file, PC, or memory) but only one ALU operation per cycle The Multicycle Datapath The Multicycle Datapath with Control Signals PCWriteCond PCWrite PCSource IorD ALUOp Control MemRead ALUSrcB MemWrite ALUSrcA MemtoReg RegWrite IRWrite RegDst Instr[31-26] PC[31-28] Shift Shift 28 28 Instr[25-0] Instr[25-0] left 2 left 2 2 2 0 0 1 1 PC Memory 0 PC Memory 0 0 Read Addr 1 0 Read Addr 1 A A Address IR Address IR Read Read 1 1 Register Register 1 zero 1 zero Data 1 Data 1 Read Addr 2 Read Addr 2 ALUout ALUout Read Data Read Data 0 0 File File (Instr. or Data) (Instr. or Data) ALU ALU Write Addr Write Addr 1 Read 1 Read B B Write Data Data 2 0 Write Data Data 2 0 1 1 Write Data Write Data 4 4 MDR MDR 1 1 0 0 2 2 Instr[15-0] Sign Shift 3 Instr[15-0] Sign Shift 3 Extend left 2 Extend left 2 ALU 32 32 control Instr[5-0] Instr[5-0] 3

The Five Steps of the Load Instruction The Five Steps of the Load Instruction Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5 Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5 lw lw IFetch Dec Exec Mem WB IFetch Dec Exec Mem WB • IFetch: Instruction Fetch and Update PC The Five Steps of the Load Instruction The Five Steps of the Load Instruction Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5 Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5 lw lw IFetch Dec Exec Mem WB IFetch Dec Exec Mem WB • IFetch: Instruction Fetch and Update PC • IFetch: Instruction Fetch and Update PC • Dec: Instruction Decode, Register Read, Sign • Dec: Instruction Decode, Register Read, Sign Extend Offset Extend Offset • Exec: Execute R-type; Calculate Memory Address ; Branch Comparison; Branch and Jump Completion The Five Steps of the Load Instruction The Five Steps of the Load Instruction Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5 Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5 lw lw IFetch Dec Exec Mem WB IFetch Dec Exec Mem WB • IFetch: Instruction Fetch and Update PC • IFetch: Instruction Fetch and Update PC • Dec: Instruction Decode, Register Read, Sign • Dec: Instruction Decode, Register Read, Sign Extend Offset Extend Offset • Exec: Execute R-type; Calculate Memory Address ; • Exec: Execute R-type; Calculate Memory Address ; Branch Comparison; Branch and Jump Completion Branch Comparison; Branch and Jump Completion • Mem: Memory Read ; Memory Write Completion; R- • Mem: Memory Read ; Memory Write Completion; R- type Completion (RegFile write) type Completion (RegFile write) • WB: Memory Read Completion (RegFile write) INSTRUCTIONS TAKE FROM 3 - 5 CYCLES! 4

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.